ADC128S102

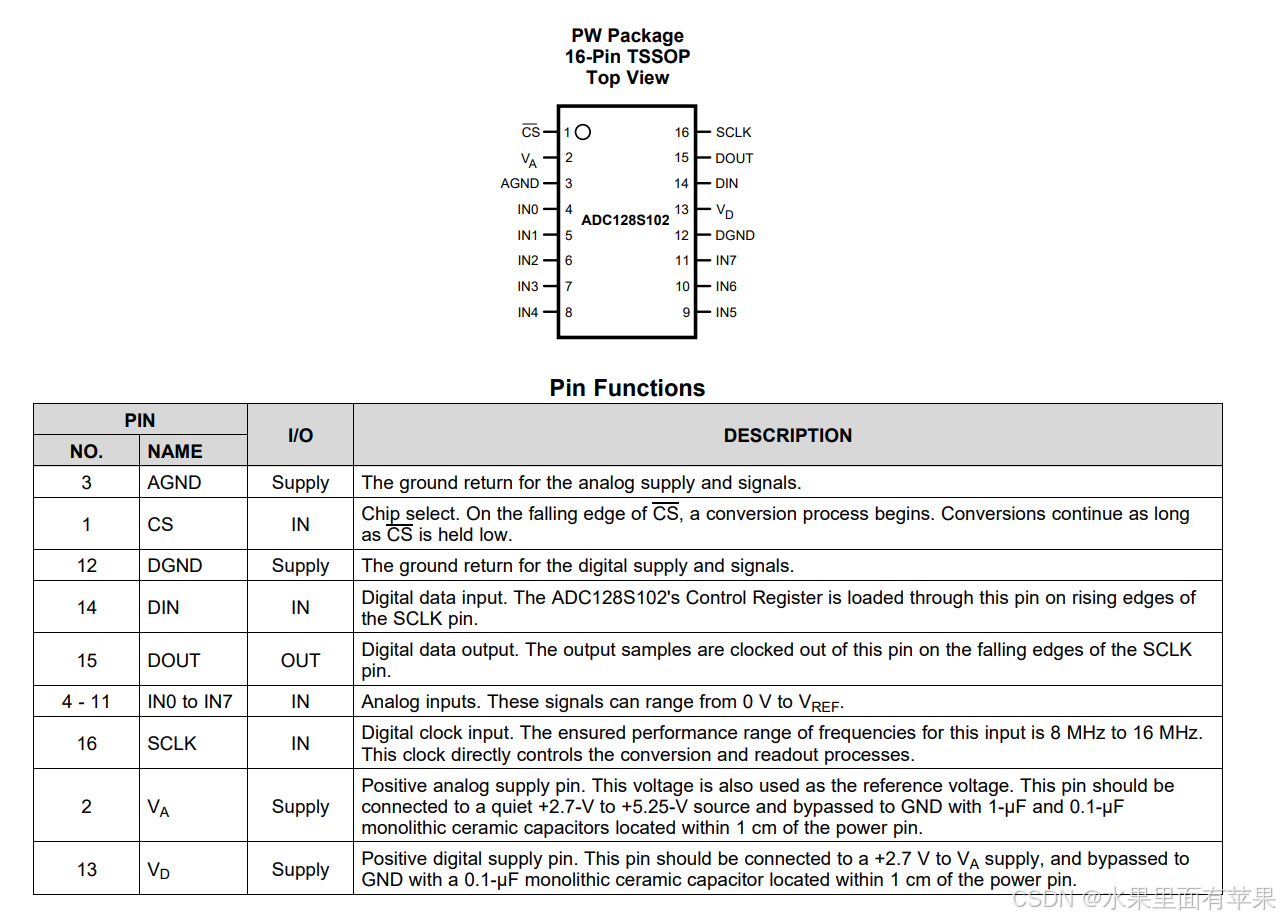

1. 引脚说明

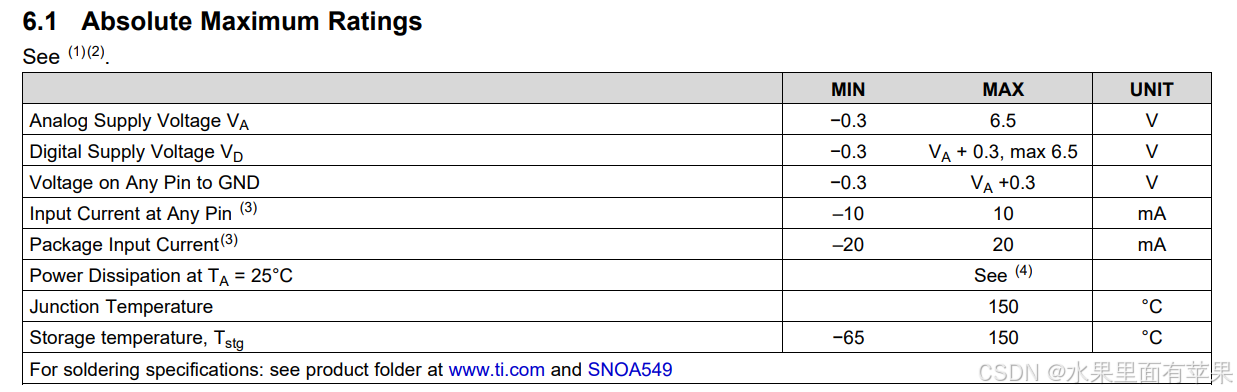

2. 最大操作

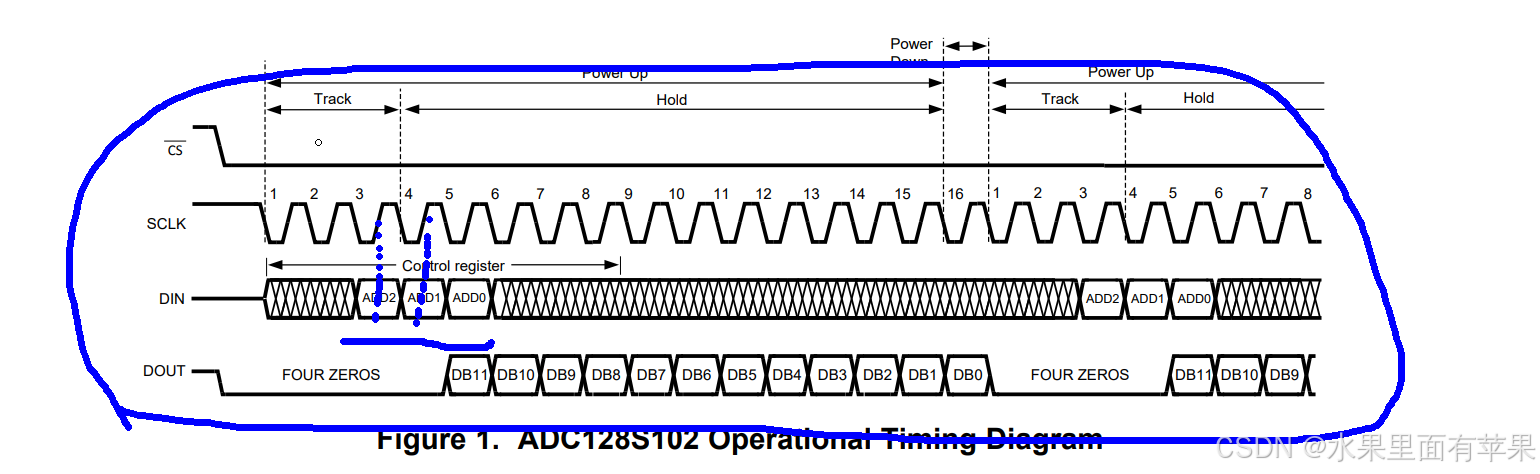

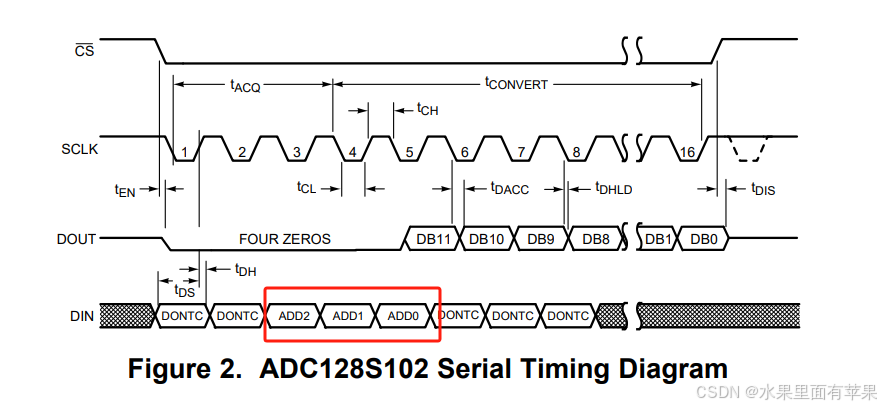

3. 时序图

- 时钟平时为 1,第一个沿改变数据,第二个沿采样数据。

- 当CS由高变低,代表着电路开始转换;而当CS由低变高,则代表电路转换的结束,每个转换周期必须包含 16 个 SCLK 时钟上升沿。当CS为高时,A/D 转换器的输出端 DOUT 为高阻态 ,当CS为低时,A/D 转换器激活,处于可工作状态,等待 SCLK 信号的配合.

- :当片选输入端CS高时,芯片处于不工作状态,数字输出端 DOUT 为高阻态;当片选输入端CS由高跳变为低,从第一个时钟信号输入端 SCLK 的上升沿采入 DIN 信号开始,芯片正式开始工作。每 16 个时钟为一个转换周期,输出一个 12位的串行数据。在 16 个时钟周期中,1、2 数据为无效,3-4为地址位控制字,5~16 为 12位数字串行输出数据

4. 注意地址的位置

5. 每次读取数据时,要发送需要转换的地址,下次16个脉冲时输出上一次设置的地址。

2360

2360

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?