文章目录

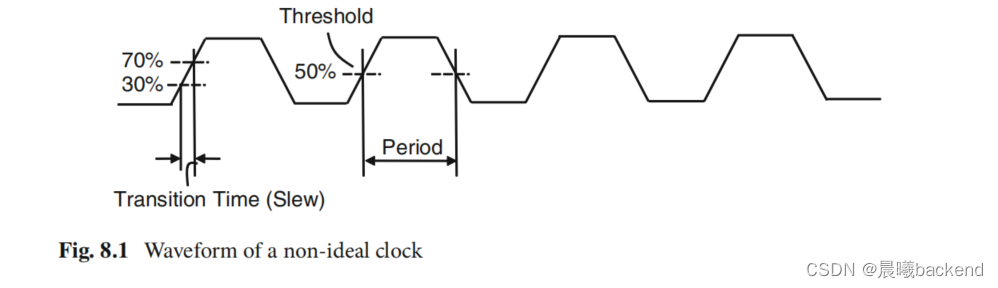

8.1 Transition Time

8.2 set_clock_transition

- Transition time of a clock is modeled in SDC using set_clock_transition .

set_clock_transition [- rise ]

[- fall ]

[- max ]

[- min ]

clock_list

transition_time

-

-rise选项用于提供时钟上升沿的过渡时间,-fall用于提供下降沿的过渡时间。-max和-min选项设定过渡时间的最大和最小操作条件。-rise/-fall/-max/-min这些选项可单独使用或一起使用。

-

但是必须注意它们不能与过渡时间矛盾。例如,过渡时间不能为负数或者最大值不应当小于最小值。过渡时间可以设定于一个时钟或一组时钟。设定的过渡时间适用于时钟网络,并且网络中时序电路元器件的时钟引脚数值是相同的。使用该约束的时钟应当匹配使用create_clock或者create_generated_clock约束设定的命名。

# Rise transition on Clock C1

set_clock_transition -rise 0.2 [get_clocks C1]

# Fall transition on Clock C2 for min and max conditions

set_clock_transition -fall -min 0.2 [get_clocks C2]

set_clock_transition -fall -max 0.4 [get_clocks C2]

# Transition ( rise , fall , min , max ) on all clocks in the design

set_clock_transition 0.3 [all_clocks]

- 应当注意**set_clock_transition仅用于预布局阶段,即时钟树综合完成之前。**在时钟树生成之后,该命令不应用于任何的后布局时序分析。

- 通过该命令设定的过渡时间是从一个状态过渡为另一个状态所需的时间。然而,过渡时间的阈值范围是特征库的属性。

8.3 Skew and Jitter

-

一个由源产生的时钟信号不可能同时到达所有的触发器。到达不同触发器的时间不同可能是由于时钟网络里不同的路径、耦合电容或者其他PVT(工艺、电压、温度)上的变化而引起的。**这会导致相同的时钟信号到达各个设备时的时钟沿无法对齐。时钟到达不同点的差异称为时钟偏斜。**时钟偏斜存在于相同时钟(内部时钟)或不同(通常是同步的)时钟(交互时钟)之间的不同点上。

-

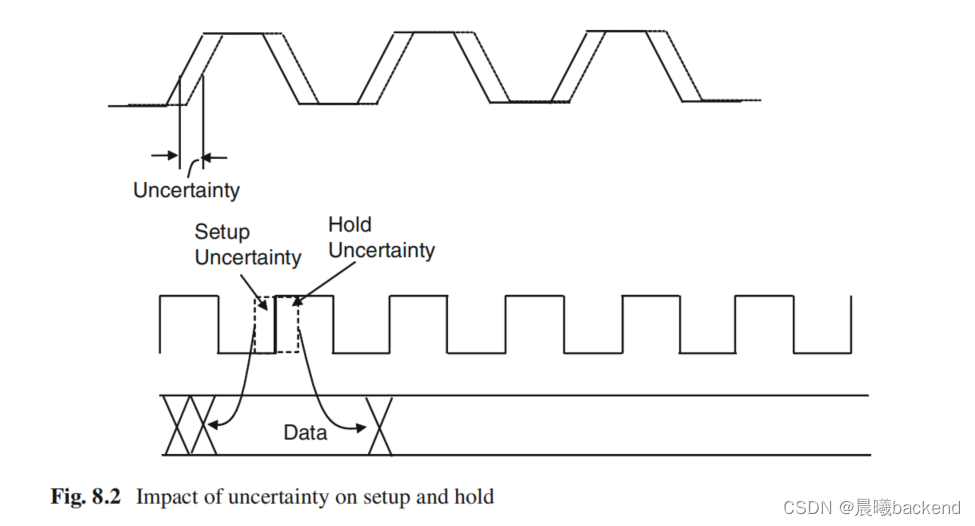

在产生时钟的设备(如PLL)处,考虑到串扰、电磁干扰或PLL特性等因素时钟沿不具备确定性。这种时钟周期性的不良偏差称为抖动。由于偏斜或抖动问题,设计会违反建立和保持原则。如图8.2所示,这些偏差致使时钟沿在时标上滑动从而减少或增加有效时间以满足建立和/或保持要求。偏斜或抖动会导致不可预测性,即无法准确计算何时一个边沿能够到达触发器(时序设备),这称为不确定度。

8.4 set_clock_uncertainty

- Clock skew and jitter are modeled in SDC using set _clock _uncertainty .

set_clock_uncertainty [-from | -rise_from | -fall_from from_clock]

[-to |-rise_to | -fall_to to_clock]

[-setup ]

[-hold ]

[-rise ]

[-fall ]

[object_list]

Uncertainty_value

8.4.1 Intraclock Uncertainty—内部时钟不确定度

-

对单个时钟(内部时钟不确定度)的偏斜或抖动建模时,你需要设定时钟名称、端口和引脚。当你设定一个时钟时,则其不确定度适用于所有由该时钟驱动的时序电路元器件。当适用于端口或者引脚时,则对所有端口或引脚扇出的时钟(及其相应的时序电路元器件)

也适用。 -

可以利用-setup和-hold选项对建立和保持检查设定不同的不确定度。

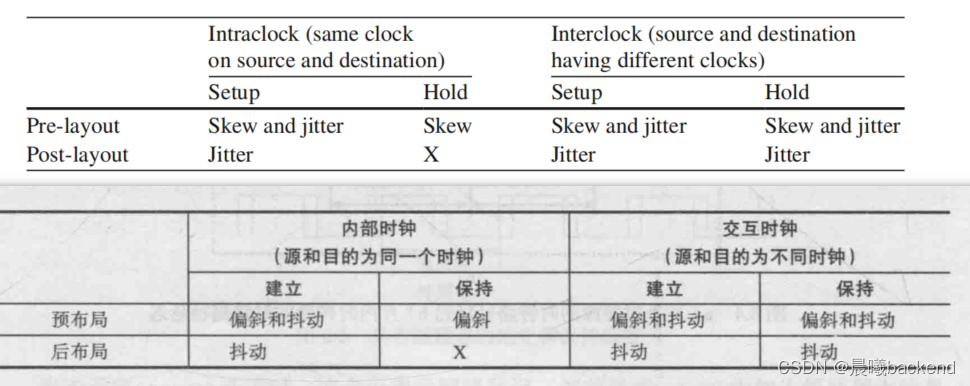

- For intraclock uncertainty, setup is impacted by both jitter and skew. While hold is impacted only by skew, not jitter.

-

A hold check is made at the same edge for launch and capture clock. Thus, any jitter impacts both the launch and the capture devices by exactly the same amount, and in the same direction. Thus, intraclock hold analysis need not care about jitter.

Hence, it is recommended to have different values for setup and hold uncertainty with hold (only skew) being less than setup (skew and jitter).

8.4.2 Interclock Uncertainty—交互时钟不确定度

-

While modeling interclock uncertainty, source (start) clock is specified using the -from option and the destination (end) clock is specified using -to option.

-

如果设计者想针对不同的上升沿和下降沿分别建立不确定度,则可利用-rise_from、-fall_from、-rise_to、-fall_to这些选项.在这些选项之前用户可利用-rise和-fall进行设定。然而,**利用-from设置上升沿条件或-to设置下降沿条件并不能保证很好的精确度。**这或许是因为时间区间有可能在设置这些参数之前就从参照标准中被删除了。如今大多数静态时序分析工具把这些视为过时的选项。

-

如果用户希望只对建立检查设定不确定度或者给建立和保持设定不同的值,则可以利用-setup和-hold选项。建立要包括两个时钟的抖动和偏斜。不像内部时钟,这种情况中两个时钟的抖动和偏斜都需要考虑保持,因为发射和捕获时钟都有自己的偏斜和抖动。最坏的情况下,它们可能是反向的,如对于建立来说,发射时钟有延迟而捕获时钟却提前了;对于保持时间来说,发射时钟提前了,捕获时钟却又延迟了。

-

下列指令可用于设置所有由各自时钟驱动的触发器和锁存器的不确定度。

# Clock uncertainty from C1 to C2 for setup and hold

set_clock_uncertainty -from C1 -to C2 -setup 0.5

set_clock_uncertainty -from C1 -to C2 -hold 0.5

# Clock uncertainty from rising edge (C1) to falling edge (C2)

set_clock_uncertainty -rise_from C1 -fall_to C2 0.5

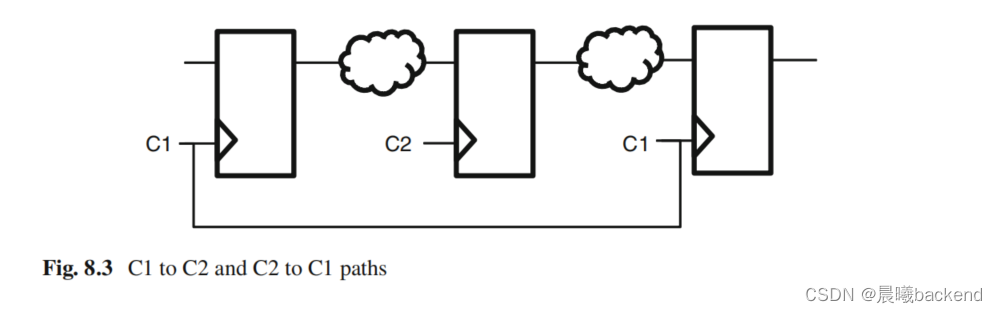

在图8.3中给出了C1到C2和C2到C1的路径。常见的错误之一是设置了C1到C2的不确定度,这不会包括C2到C1的路径。 不确定度必须涵盖所有源和目的时钟的组合。

# Clock uncertainty between C1 and C2

set_clock_uncertainty -from C1 -to C2 0.5

set_clock_uncertainty -from C2 -to C1 0.5

- 当交互时钟和内部时钟都设定了不确定度时,交互时钟优先级更高。

# Intraclock and Interclock Uncertainty Conflict

set_clock_uncertainty 0.6 -from C2 -to C1

set_clock_uncertainty 0.5 [get_clocks C1]

- 在上面的例子中时钟C1上有两个不同的不确定度。**在所有C2到C1的路径中,交互时钟使用的不确定度为0.6,其优先级最高。**在其他以C1为目的时钟的路径中,内部时钟的不确定度为0.5。

不确定度的另一个要点是预布局和后布局两个阶段数值会发生变化。预布局阶段时钟树综合还未执行,不确定度必须考虑偏斜所带来的影响。而时钟树综合之后,偏斜部分已经确定,就不需要再作为不确定度来设置了。因此,布局后阶段的时钟不确定度一般小于预布局阶段的。

8.5 Clock Latency

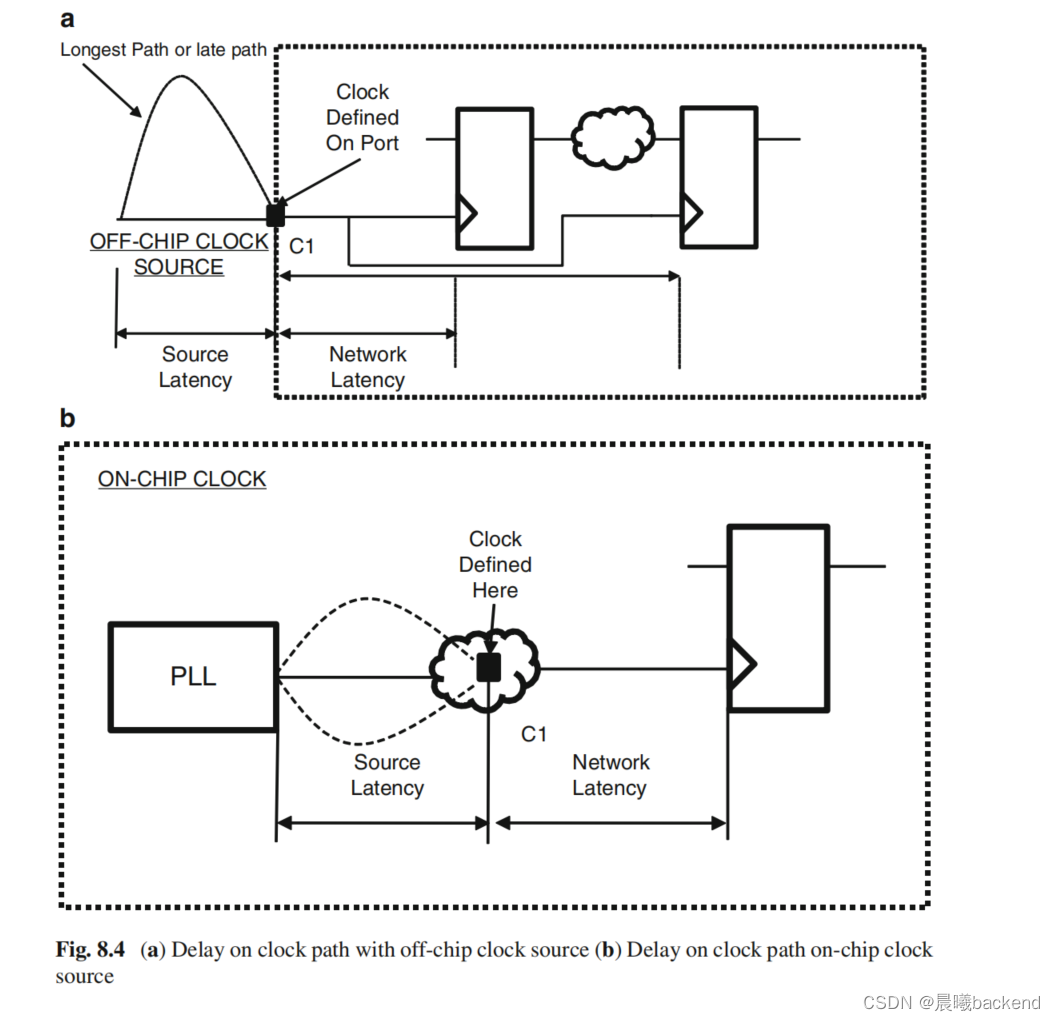

- 时钟延迟包括两部分——源和网络延迟(source and network latency)。源延迟是指源时钟到定义的时钟点(在SDC中通过create_clock / create_generated_clock定义)的延迟。这个源可以是片内的也可以是片外的。

- 网络延迟是从被时钟定义的点到实际触发的时序设备所需要的时间。

8.6 set_clock_latency

set_clock_latency [-rise]

[-fall ]

[-min ]

[-max ]

[-source ]

[-late ]

[-early ]

[-clock clock_list]

delay

object_list

- -rise/-fall选项指定了时钟上升沿和下降沿的延迟。

- -min/-max选项可单独使用或一起使用,它们指定了操作条件最小和最大延迟。但要注意不能设置互相矛盾的延迟值。例如,

延迟不能是负数或者最大值小于最小值。

若需设定延迟的源组件,用户需要利用-source选项以及时钟名。在图8.4a中,假设在端口定义SDC时钟的是C1,则源延迟表示的是从片外源到端口的延迟。可表示为:

set_clock_latency -source 0.5 [get_clocks C1]

- 在图8.4b中,如果从PLL到时钟定义处(即PLL的输出)有多条路径,则最长路径的延迟可利用-late选项表示,而最短路径的延迟可利用-early选项来表示。

set_clock_latency -source -early 0.5 [get_clocks C1]

set_clock_latency -source -late 1.0 [get_clocks C1]

- 当未设定-source选项时,该命令表示网络延迟。

- 对于图8.4a,以下的指令表示时钟网络的延迟。这些延迟适用于所有由时钟触发的时序设备。

# Network Latency – Applies to rise (for max and min conditions)

set_clock_latency 0.5 -rise [get_clocks C1]

# Network Latency – Applies to fall (for max and min conditions)

set_clock_latency 0.3 -fall [get_clocks C1]

# Network Latency to all register clock pins in fanout of A

set_clock_latency 0.5 [get_ports A]

# Network Latency to all register pins in fanout of B, which are clocked

# by C1 and C2

set_clock_latency 1.0 -clock {C1 C2} [get_ports B]

- SDC中源延迟和网络延迟在概念上是有差别的。源延迟仅可用于时钟,而网络延迟可用于时钟、端口或者引脚。

- 源延迟仅能用于对早期和后期路径建模。最后,网络延迟是时钟树综合之前的一个预估延迟,CTS完成后并不需要再设定。

- After CTS, it is recommended to use set_propagated_clock command to give directive to the tool that clock network latency needs

to be computed based on the actual circuit elements – including parasitics. The actual network latency after CTS is also referred to insertion delay . That said, source latency still need to be specifi ed after CTS for the propagated clock. - CTS之后实际的网络延迟也称为插入延迟。也就是说,源延迟仍需要在传递时钟的CTS之后设定。

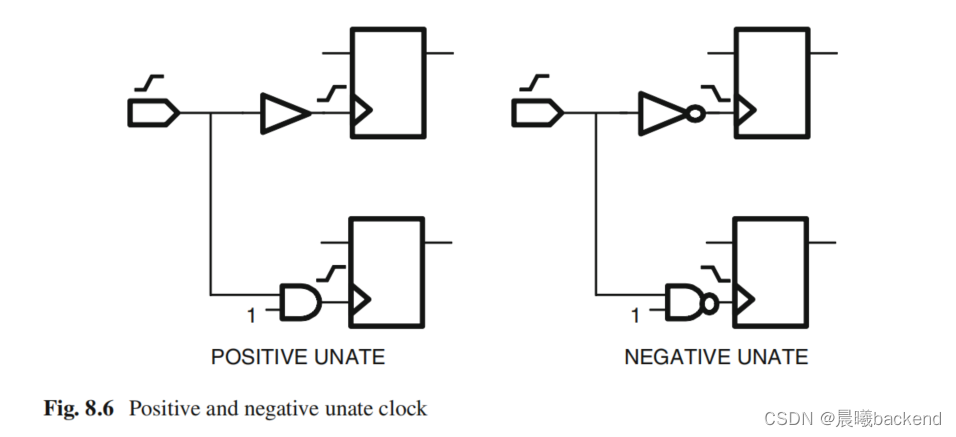

8.7 Clock Path Unateness

8.8 set_clock_sense

set_clock_sense [-positive | -negative | -stop_propagation ]

[-pulse pulse ]

[-clock clock_list]

pin_list

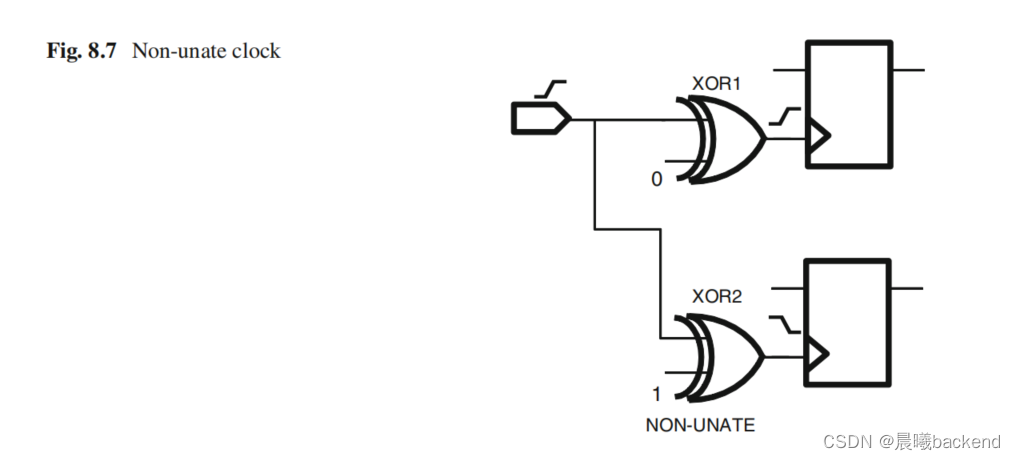

这个指令只在非单调时钟网络中才有意义。为了设定时钟网络的单调性,用户需要对时钟所通过的引脚进行命名。例如,对图8.7中的负单调时钟,SDC可写成:

set_clock_sense -negative [get_pins XOR2/Z]

- 如果多个时钟路径收敛于异或门这类元器件,那么上述指令意味着所有时钟的负边沿都将被加入到分析中。要选择部分时钟可利用-clock选项。例如:

set_clock_sense -positive -clock [get_clocks C1] [get_pins XOR1/Z]

set_clock_sense -negative -clock [get_clocks C2] [get_pins XOR2/Z]

与-positive和-negative选项互斥的是-stop_propagation。如果设计者希望禁用部分时钟的传递可利用这个选项。

set_clock_sense -stop_propagation -clock [get_clocks C3] [get_pins XOR1/Z]

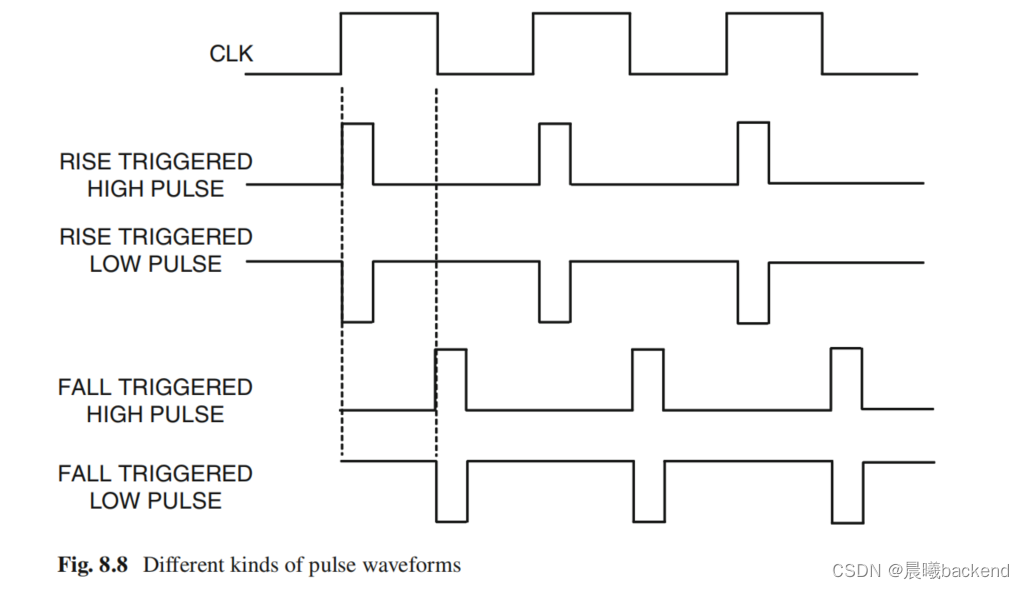

- 可以利用create_generated_clock 建立脉冲。另一种建立脉冲的方法是在set_clock_sense中利用-pulse选项,如下所示:

set_clock_sense -pulse rise_triggered_high_pulse [get_pins AN1/Z]

-pulse选项可在以下选项中选择一个值:rise_triggered_high_pulse、rise_triggered_low_pulse、fall_triggered_high_pulse、fall_triggered_low_pulse。上升沿触发脉冲是源时钟的上升沿有效,反之下降沿触发则是下降沿有效。图8.8给出了不同类型的脉冲波形。

**针对脉冲使用set_clock_sense优于create_generated_clock,因为这样不会多创建一个时钟而产生一个多余的域。**对于一个脉冲,无论使用什么方法,脉冲宽度都假设为0。而当仅使用set clock sense时,实际的脉冲宽度是基于上升和下降延迟的差值计算得出的。用户可以设置产生脉冲的引脚的延迟。例如,上述的set clock sense补全则为:

set_clock_latency -rise 0.2 [get_pins AN1/Z]

set_clock_latency -fall 0.9 [get_pins AN1/Z]

- This will result in a pulse of width 0.7ns . In general the pulse width is calculated as

Pulse_width = | rise_latency -fall_latency |

8.9 Ideal Network

set_ideal_network [-no_propagate ]

object_list

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?