文章目录

- 6.1 Clock Divider

- 6.2 Clock Multiplier

- 6.3 Clock Gating

- 6.4 create_generated_clock

- 6.4.1 Defining the Generated Clock Object---定义生成时钟的对象

- 6.4.2 Defining the Source of Generated Clock---定义生成时钟的源

- 6.4.3 Naming the Clock

- 6.4.4 Specifying the Generated Clock Characteristic---设定生成时钟的特性

- 6.4.5 Shifting the Edges---Shifting the Edges

- 6.4.6 More than One Clock on the Same Source---多个同源时钟

- 6.4.7 Enabling Combinational Path---使能组合电路路径

- 6.5 Generated Clock Gotchas---生成时钟相关的注意事项

-

当设计中有多个时钟存在时,它们需要互相协作或各司其职。异步时钟是不能共享确定相位关系的时钟信号。当多个时钟域交

互时,设计中只有异步时钟很难满足建立和保持要求。 -

同步时钟则会共享固定相位关系。往往同步时钟产生自同一个时钟源。

-

如今的SoC(片上系统)在同一个芯片内包含多种异构设备。同一个芯片内可能包括高速的处理器以及低速的存储器。这些工作在不同频率下的器件通常由不同的时钟触发。每个部分的运行是基于各自时钟的,这些会带来异步性的设计问题。这可能导致几个时钟都源于一个主时钟。这种时钟称为生成时钟或派生时钟。这类时钟可通过以下几种方式产生:

- 时钟分频器,Clock dividers

- 时钟乘法器,Clock multipliers

- 时钟门控,Clock gating

6.1 Clock Divider

- 时钟分频器产生一个比原始的时钟源频率更低且周期更长的时钟信号。

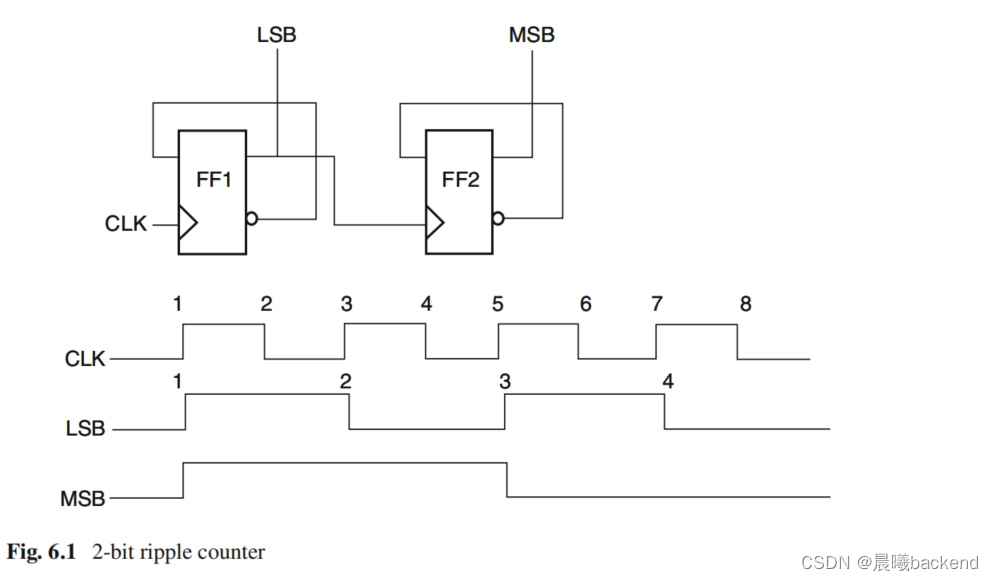

- 典型的时钟分频器是2位纹波计数器。纹波计数器的电路如图6.1所示。对于该电路,如果第一个输入触发器的时钟周期为10ns,则在产生波

形的LSB(最低有效位)除以2,得到周期为20ns的信号。同样,在波形的MSB(最高有效位)除以4,则得到周期为40ns的信号。

6.2 Clock Multiplier

-

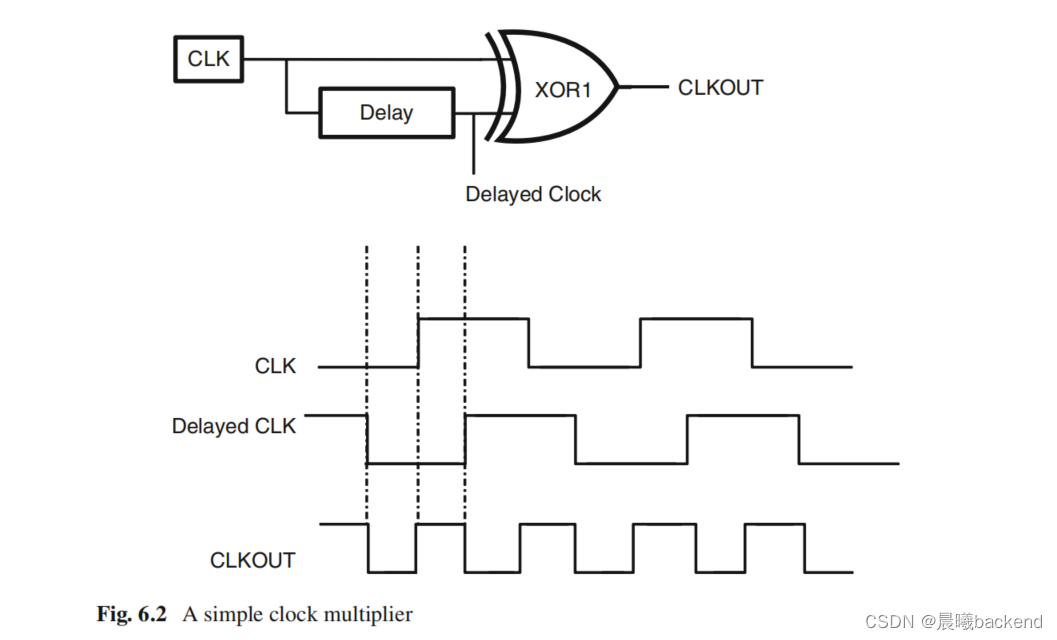

时钟乘法器是一种通过频率增加和周期减少来获得更快时钟速度的电路。这种技术通常用于微处理器和内部总线,并配合内部高速缓存以提高处理器的吞吐量。图6.2给出了一个简单的实现时钟倍频的时钟乘法器电路。该电路实现了时钟信号的产生以及具有延迟的功能。延时可通过缓冲器和反相器引入到线路中。

-

通常利用PLL(锁相环)来实现倍频。

6.3 Clock Gating

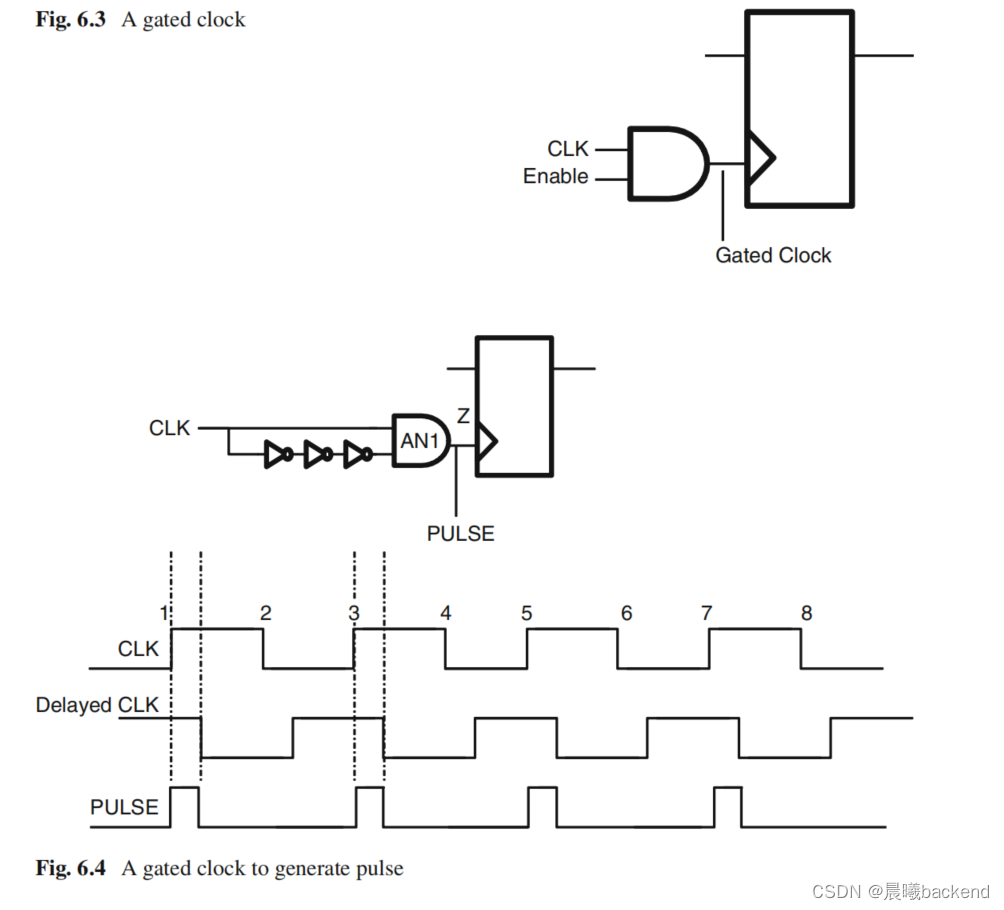

- 自20世纪90年代中期以来,时钟门控成为了一种非常流行的减少功耗的技术。当触发器或寄存器因时钟触发而改变状态时,会产生一定的功耗。然而,部分逻辑电路可能又不会在某些时候派上用场。这种情况下,禁用这部分时钟信号可以减少状态切换带来的功耗。也就是说,时钟信号要等到逻辑电路使能之后才有效,这种时钟称为门控时钟。图6.3给出了一个门控时钟的示例。

6.4 create_generated_clock

create_generated_clock [source_objects]

-source clock_source_pin

[ -master_clock master_clock_name]

[ -name generated_clock_name]

[ -edges edge_list]

[ -divide_by factor]

[ -multiply_by factor]

[ -invert ]

[ -edge_shift shift_list]

[ -duty_cycle percent]

[ -combinational ]

[ -add ]

[ -comment comment_string]

6.4.1 Defining the Generated Clock Object—定义生成时钟的对象

- create_generated_clock is generally specifi ed on design objects where the clock is actually available after division or multiplication or any other form of generation. These design objects called source objects can be port, pin, or net. When defi ning a clock on a net, ensure that net has a driver pin or the port. Otherwise the clock will not have a source. These are the points from where generated clocks can propagate into the circuit.

6.4.2 Defining the Source of Generated Clock—定义生成时钟的源

- 设定生成时钟的源引脚可利用-source选项。这个选项可以指明生成时钟是由哪个主时钟的源引脚派生的。例如,在图6.1中,生成时钟定义为LSB和MSB,生成时钟的源信号则定义为CLK。

- 建议理解源对象和生成时钟源之间的区别(difference between a source object and the source of the generated clock)

- 源对象指的是生成时钟(或者时钟)设定在哪个位置,

- 而生成时钟源指的是哪个是获得生成时钟的参考信号。

6.4.3 Naming the Clock

- 像主时钟一样,生成时钟也需要通过名称来标识。可通过-name选项设定一个名称。若没有定义-name时,开发工具会自动指派一个名称。与生成时钟建立依赖关系后,以后任何SDC指令都将引用该名称。

6.4.4 Specifying the Generated Clock Characteristic—设定生成时钟的特性

- 设定生成时钟的特性可利用以下3个选项当中的1个:

- -edges------作为一个对应源时钟边沿的整数列表,它表明了是从哪个生成时钟而产生的时钟边沿。时钟沿是指生成时钟交替的上升沿和下降沿。时钟沿的个数必须为奇数个整数,并且应当至少由3个整数表示一个完整生成时钟的周期。时钟沿计数由“1”开始,这个“1”表示源时钟的第一个上升沿。

- -divide_by------这表示生成时钟通过某个因子而分频,周期则通过这个因子而加倍。

- -multiply_by------这表示生成时钟通过某个因子而倍频,周期则要除以这个因子。应当注意的是,尽管时钟通过周期特性来定义,但要记住multiply_by和divide_by则是通过频率特性来设定的(即周期的倒数)。

- 总的来说,**任何使用-divide_by或-multiply_by来表示的生成时钟也可以使用-edges来表示。反之则未必正确(相位变化了只能用-edge)。**参照图6.1,假设create_clock定义CLK,在CLK的LSB和MSB定义生成时钟。

create_clock -period 10 -name CLK [get_ports CLK]

create_generated_clock -name LSB -source [get_port CLK] -divide_by 2 [get_pins FF1/Q]

create_generated_clock -name MSB -source [get_pins FF1/Q] -divide_by 2 [get_pins FF2/Q]

- 在LSB和MSB生成的时钟同样可用-edges选项表示:

create_generated_clock -name LSB -source [get_ports CLK] -edges {1 3 5}[get_pins FF1/Q]

create_generated_clock -name MSB -source [get_pins FF1/Q] -edges {1 3 5}[get_pins FF2/Q]

- MSB上相同的波形可由CLK作为源时钟而生成。对于这种情况时钟沿应该为{159}。

create_generated_clock -name MSB -source [get_ports CLK] -edges {1 5 9} [get_pins FF2/Q]

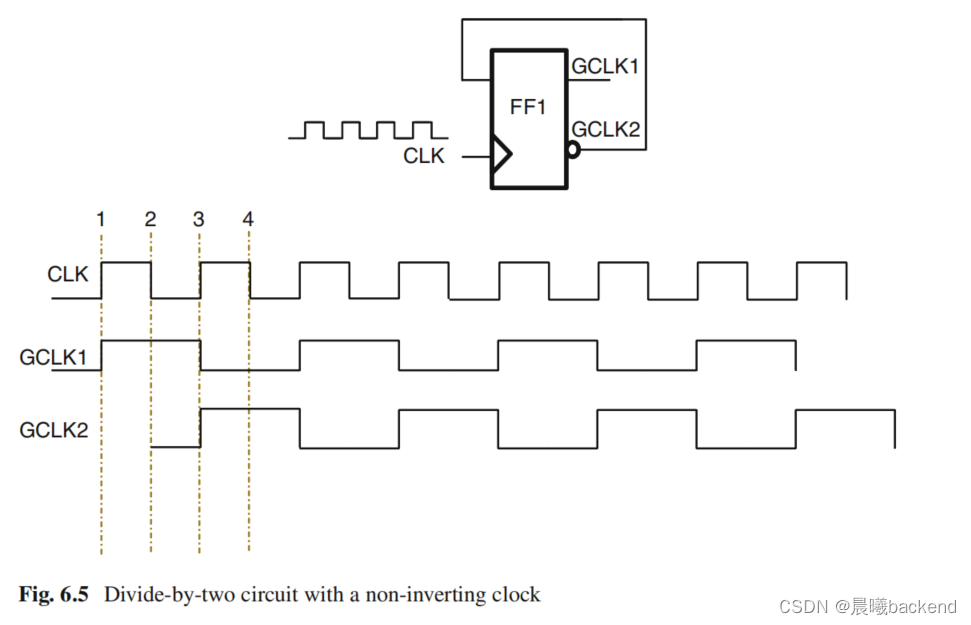

- 在图6.5中,分频器由源时钟的上升沿触发,并定义生成时钟GCLK1为:

create_generated_clock -name GCLK1 -source [get_ports CLK] -divide_by 2 [get_pins FF1/Q]

- GCLK2是GCLK1的反相版本,因此定义为:

create_generated_clock -name GCLK2 -source [get_ports CLK] -divide_by 2 -invert [get_pins FF1/QBAR]

应当注意的是,-invert并不会在生成时钟的过渡过程中导致源时钟沿发生变化。它仅仅影响生成时钟的起始是在上升沿过渡还是下降沿过渡。

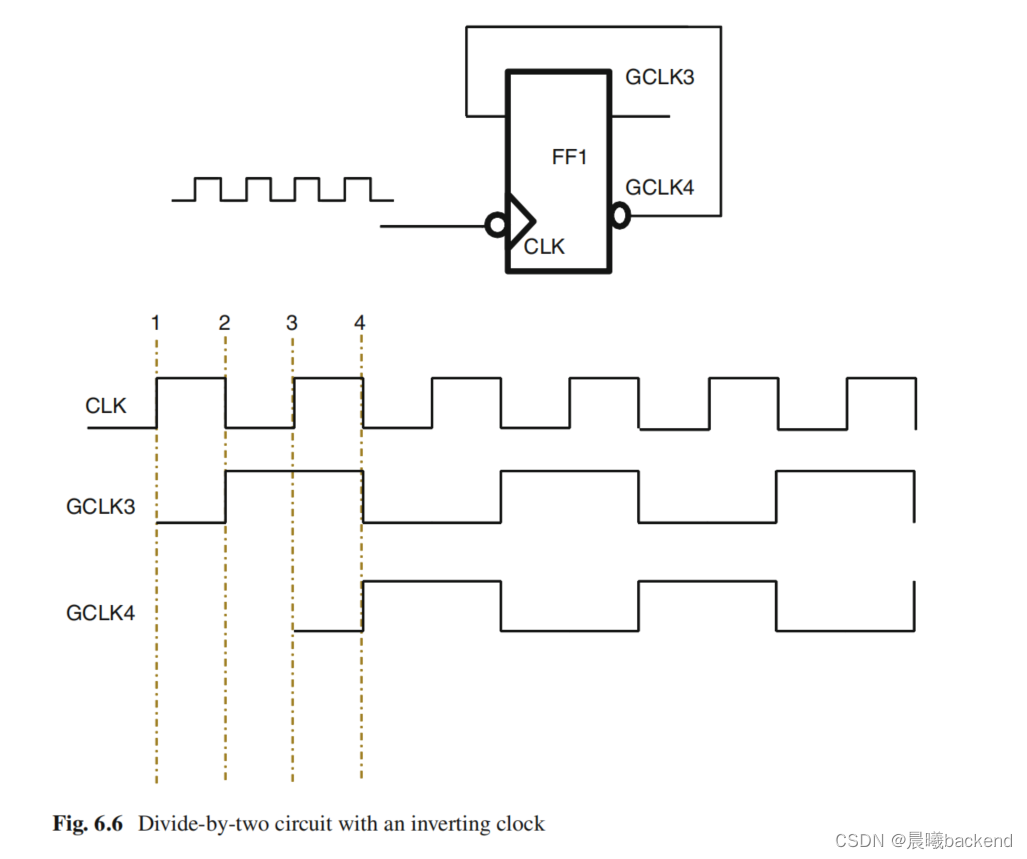

- 然而在图6.6中,分频器由源时钟的下降沿触发。这种情况下,生成时钟GCLK3定义为:

create_generated_clock -name GCLK3 -source [get_ports CLK] -edges { 2 4 6} [get_pins FF1/Q]

- GCLK4是GCLK3的反相版本,因此定义为:

create_generated_clock -name GCLK4 -source [get_ports CLK] -edges { 4 6 8} [get_pins FF1/QBAR]

如上所示,GCLK3和GCLK4可利用-edges选项表示。若用任何其他方式设定,则会导致实际电路和SDC指令所表示的波形不一致。这是定义生成时钟时最常犯的错误。[这里相位变化了,只能用-edge]

- 图6.2中的CLKOUT一般表示为:

create_generated_clock -name CLKOUT -source [get_ports CLK] -multiply_by 2 [get_pins XOR1/Z]

- 当定义的时钟需要倍频时,占空比可用-duty_cycle选项来设定。该选项只能配合multiply_by来使用,用以表示倍频时钟为1时脉冲宽度的百分比。例如,图6.2中CLKOUT的占空比为50%,其表示为:

create_generated_clock -name CLKOUT -source [get_ports CLK] -multiply_by 2 [get_pins XOR1/Z] -duty_cycle 50

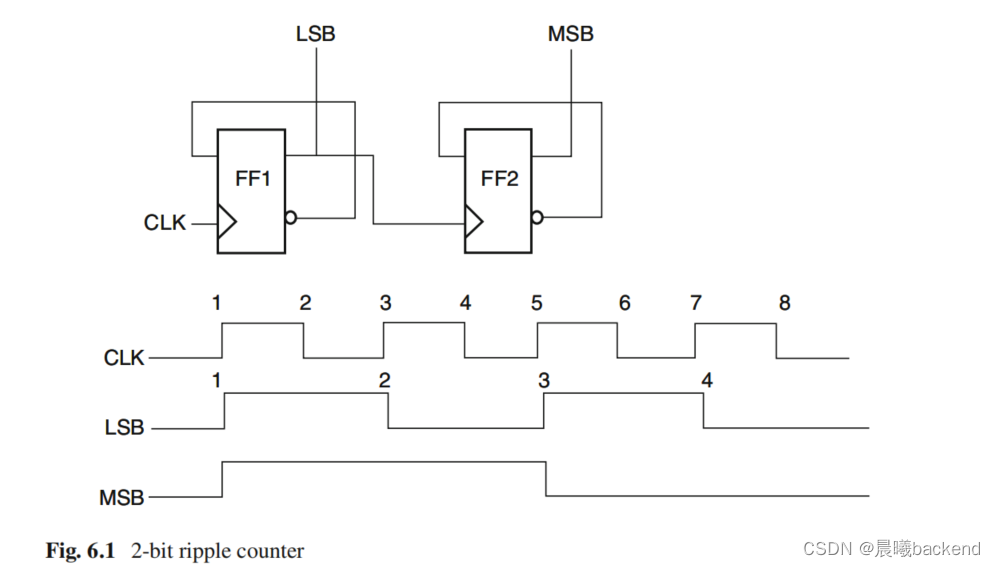

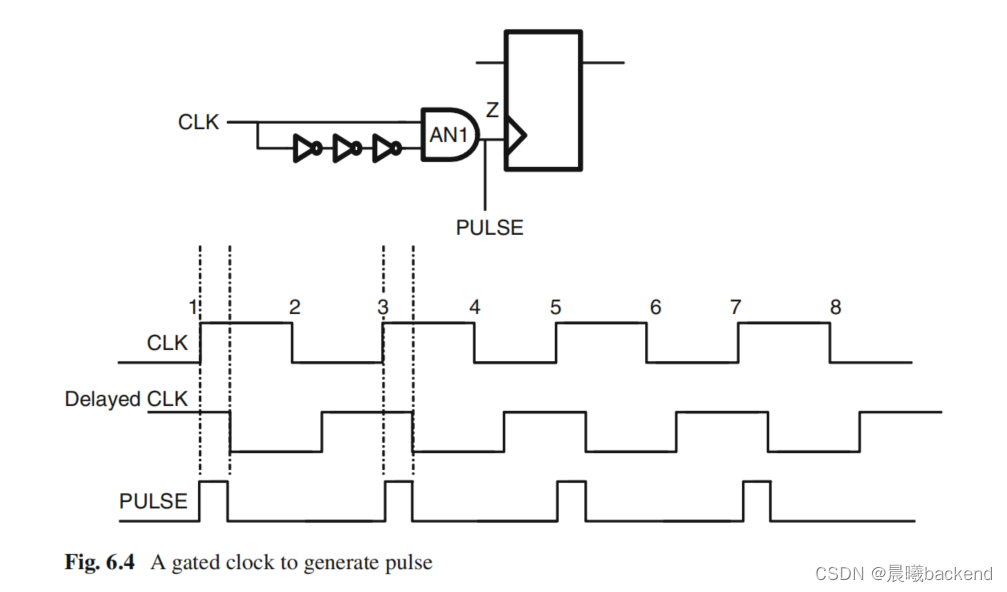

- 在图6.4中产生了一个高电平脉冲,并且脉冲宽度取决于反相器链的延迟。这种情况下,时钟沿1触发脉冲的上升沿和下降沿。其表示为:

create_generated_clock -name PULSE -source [get_ports CLK] -edges { 1 1 3} [get_pins AN1/Z]

- 时钟沿的设定可根据脉冲种类而改变。例如,在图6.4中如果与门换成与非门,则会导致一个上升沿触发低电平脉冲。这种情况表示为:

create_generated_clock -name PULSE_N -source [get_ports clk] -edges { 1 3 3} [get_pins NAND1/Z]

这是因为第一个时钟沿会产生一个低电平脉冲的下降沿和上升沿,-edges则表示上升沿和下降沿的顺序,因此表示为{1 3 3}。这意味着**生成时钟的上升沿将由源时钟的边沿1产生。**生成时钟的下一个下降沿将由源时钟的边沿3产生,之后是同样在源时钟的边沿3上产生下一个上升沿。这个下降沿实际是生成时钟的下一个脉冲。

6.4.5 Shifting the Edges—Shifting the Edges

- 生成时钟的时钟沿可能受时间的影响发生位移。例如,在图6.4中,如果反相器链的延迟为2ns,则高电平脉冲可准确地表示为:

create_generated_clock -name PULSE -source [get_ports clk] -edges { 1 1 3} -edge_shift {0 2 0} [get_pins AN1/Z]

- -edge_shift选项选取一组浮点数来表示在时间单元内每一个时钟沿的位移。该选项必须具有与时钟沿数量相同的参数来表示每一个生成时钟沿的位移。上面的指令意味着,在生成时钟上:

- 在第一个源时钟沿产生上升沿

- 在第一个源时钟沿到达2ns后产生下降沿

- 在第三个源时钟沿产生下一个上升沿

同样,对于低电平脉冲可表示为:

create_generated_clock -name PULSE_N -source [get_ports clk] -edges { 1 3 3}-edge_shift {2 0 2} [get_pins NAND1/Z]

- 这个指令意味着,在生成时钟上:

- 在第一个源时钟沿到达2ns后产生上升沿

- 在第三个源时钟沿产生下降沿

- 在第三个源时钟沿到达2ns后产生下一个上升沿位移可以是正向也可以是反向的。利用-edges和-edge_shift可以对任何复杂的生成时

钟进行建模。

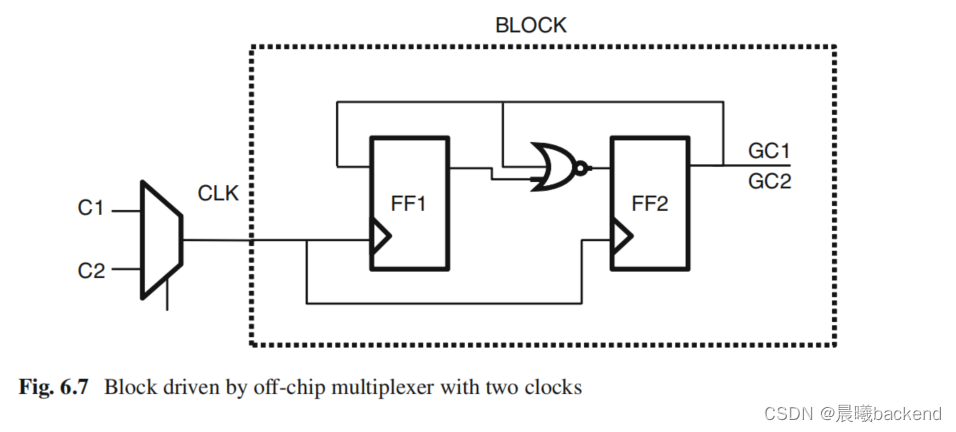

6.4.6 More than One Clock on the Same Source—多个同源时钟

- 由于每个时钟需要定义唯一的名称,所以使用-add选项时必须要使用-name选项。

create_clock -name C1 -period 10 [get_ports CLK]

create_clock -name C2-period 15 [get_ports CLK] -add

# The following generated clock is based on C1’s characteristics

create_generated_clock -name GC1 -divide_by 3 -source [get_port CLK] -master_clock C1 [get_pins FF2/Q]

# The following generated clock is based on C2’s characteristics

create_generated_clock -name GC2 -divide_by 3 -source [get_port CLK] -master_clock C2 [get_pins FF2/Q] -add

6.4.7 Enabling Combinational Path—使能组合电路路径

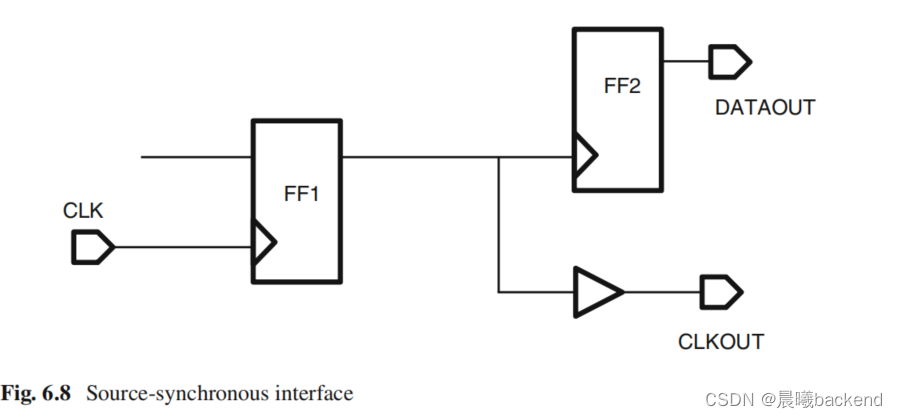

- 图6.8中DATAOUT引脚的延迟应当根据CLKOUT设定。这种情况下,生成时钟需要定义在CLKOUT上。这可利用-combinational选项实现。设定了该选项后,生成时钟与主时钟引脚的周期相同,相当于divide_by 1。这时不可用其他任何选项,其表示为:

create_generated_clock -name CLKOUT -combinational -source [get_pins FF1/Q [get_ports CLKOUT]

6.5 Generated Clock Gotchas—生成时钟相关的注意事项

- 由于时钟可由多种方式生成,所以这通常会造成设计功能与时序规范之间不匹配。对于设定生成时钟,设计者必须注意以下几点:

- 如果定义一个生成时钟,应确保其是由特定源对象所生成的。不过,如果触发器或寄存器是由另一个时钟扇出的时钟信号驱动的,则要确保设定了

create_generated_clock相关的约束。一个遗漏的生成时钟将会产生无约束寄存器。 - 当多个时钟收敛于一个时钟源引脚时,应确保在定义生成时钟时设定了主时钟。

- 如果在一个引脚上存在多个源,你需要设定多个生成时钟约束,应确保使用-add选项。否则,最新设定的约束会覆盖掉其他的约束。

- 避免时钟收敛于多个组合电路路径,否则可能会导致脉冲。如果时钟收敛于多种路径(组合电路和时序电路),则特别要注意禁用时序电路路径。

- 如果定义一个生成时钟,应确保其是由特定源对象所生成的。不过,如果触发器或寄存器是由另一个时钟扇出的时钟信号驱动的,则要确保设定了

- clock在对象上定义相同的特性,而不利用生成时钟。从时序分析的角度来看,只要特性一致,时钟由create_generated_clock还是由create_clock设定并不重要。

- 然而,**若时钟是由另一个时钟派生的,则无论何时都建议使用create_generated_clock,而非create_clock。**这样做更易于维护和改进,因为修改源时钟的特性将直接影响生成时钟的特性。同样,利用正确的约束可更好地模拟设计意图,当修改或改进约束时会减少产生错误的概率------包括移植技术和设计。

2120

2120

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?