Xilinx版本:2021.2

PC系统:Windows10

1、首先准备好一个已完成的工程,打开vivado

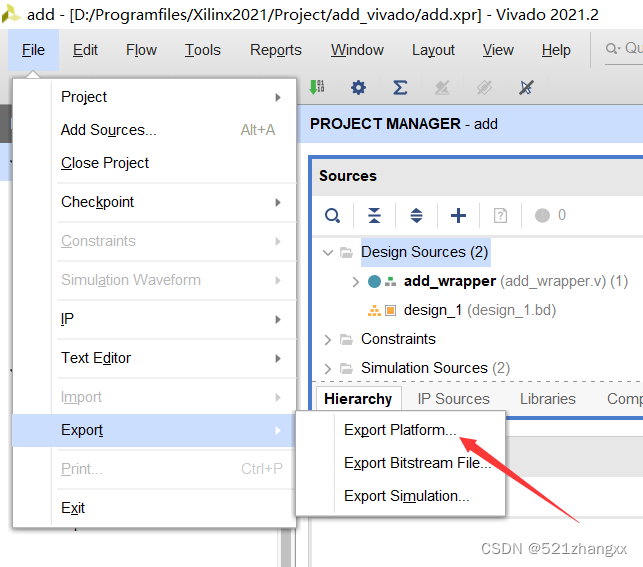

2、打开该工程,导出硬件:export hardware,如图: File->Export->Export Platform

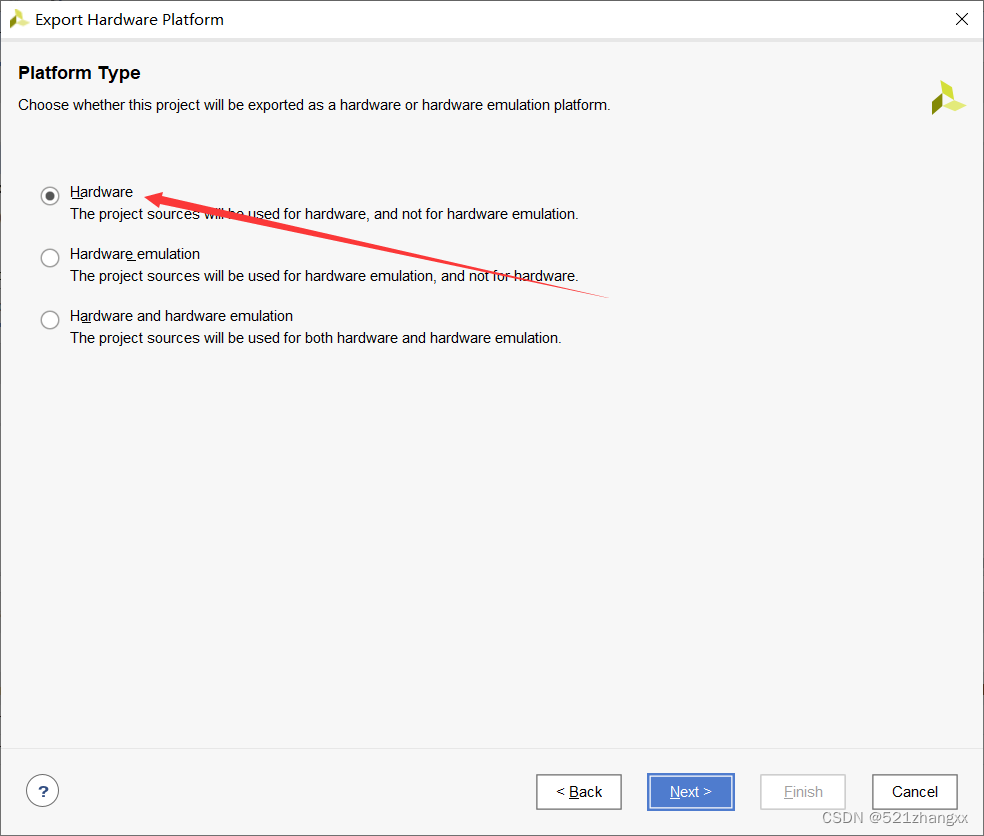

选择hardware

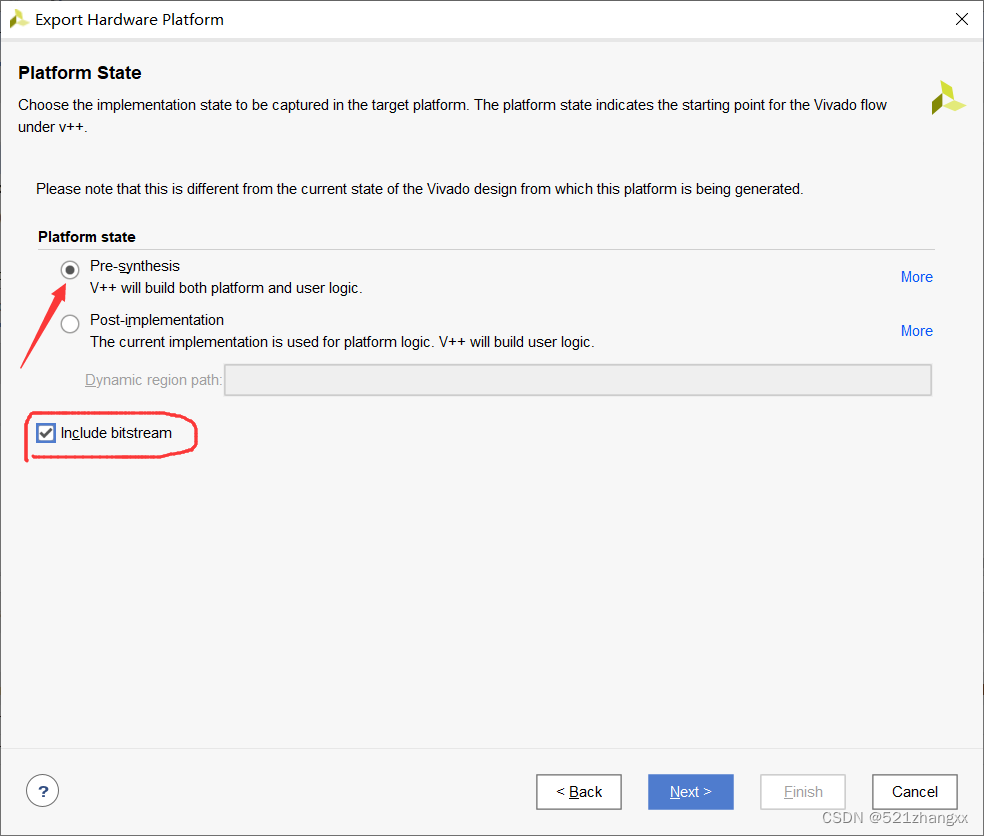

这里必须对include bitstream打勾

点击next

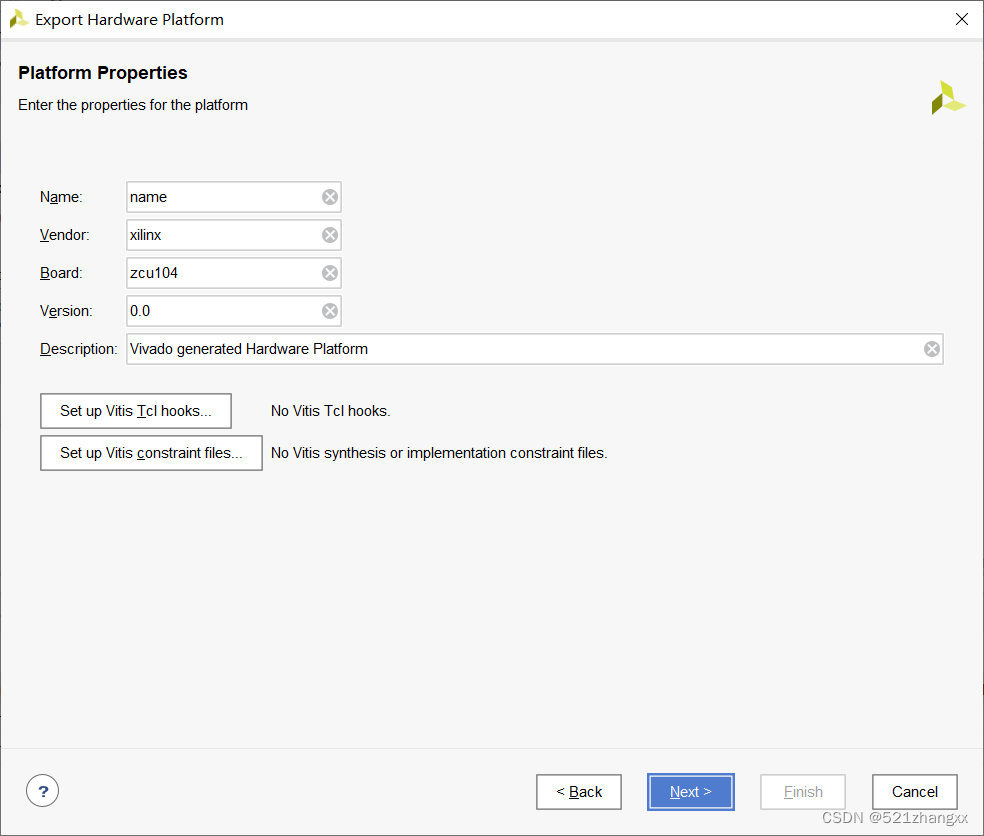

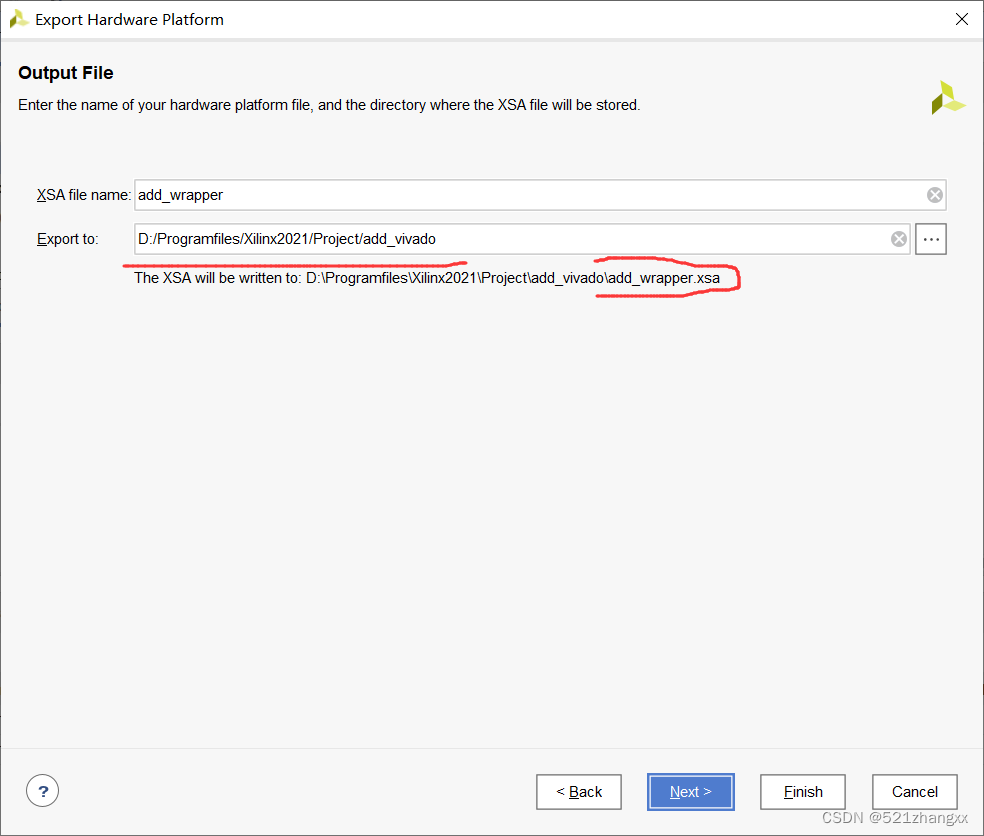

在这里选择导出的文件名称以及导出的位置,完成后会在该文件夹下生成一个.xsa文件

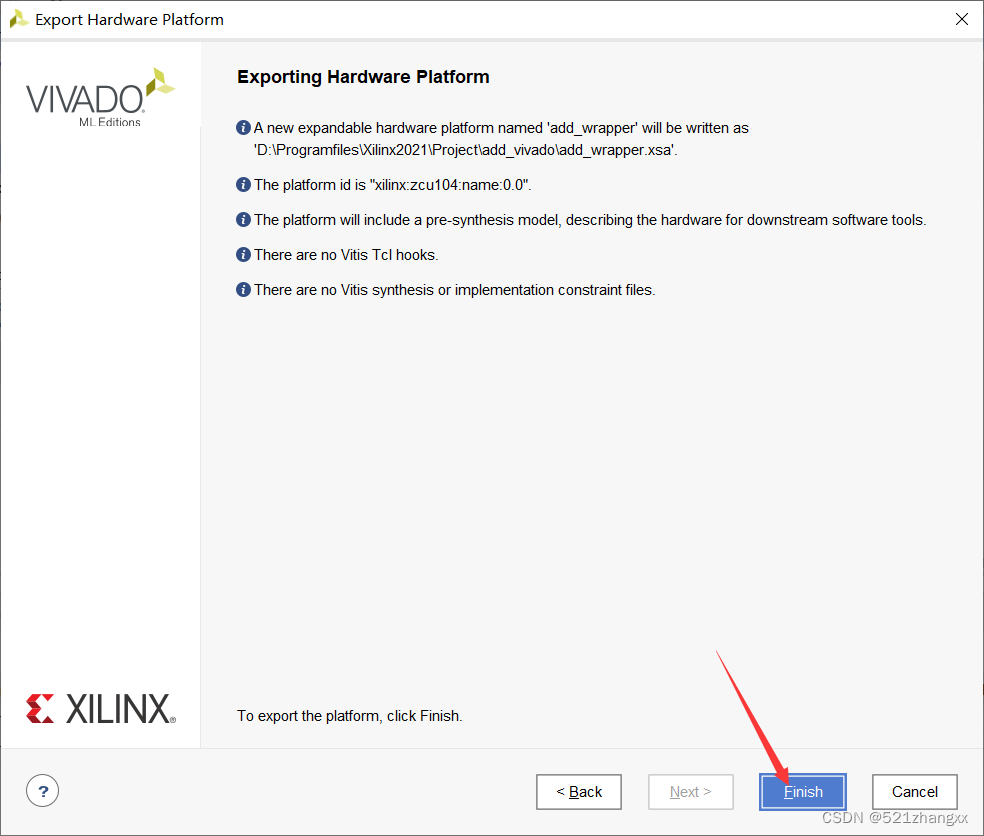

点击finish等待就可以了

最终生成的是这个文件:如图

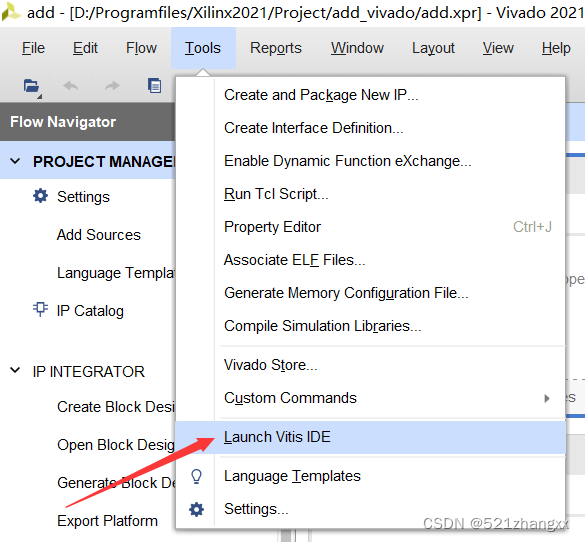

3、打开SDK,方法如图:

之前的版本可能是在file——>launch SDK

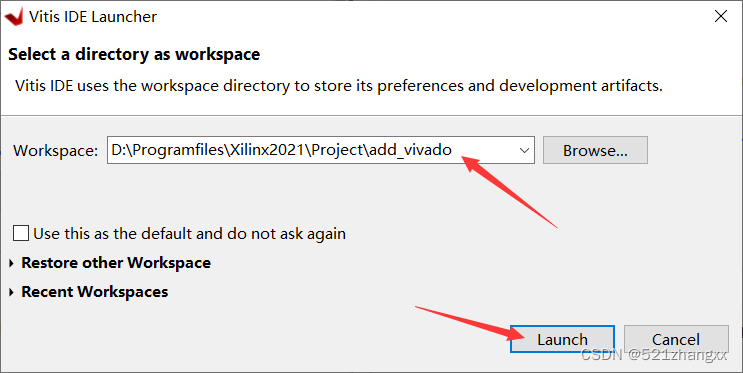

这里的位置选择与导出hardware的位置一样即可,点击launch,等待打开SDK

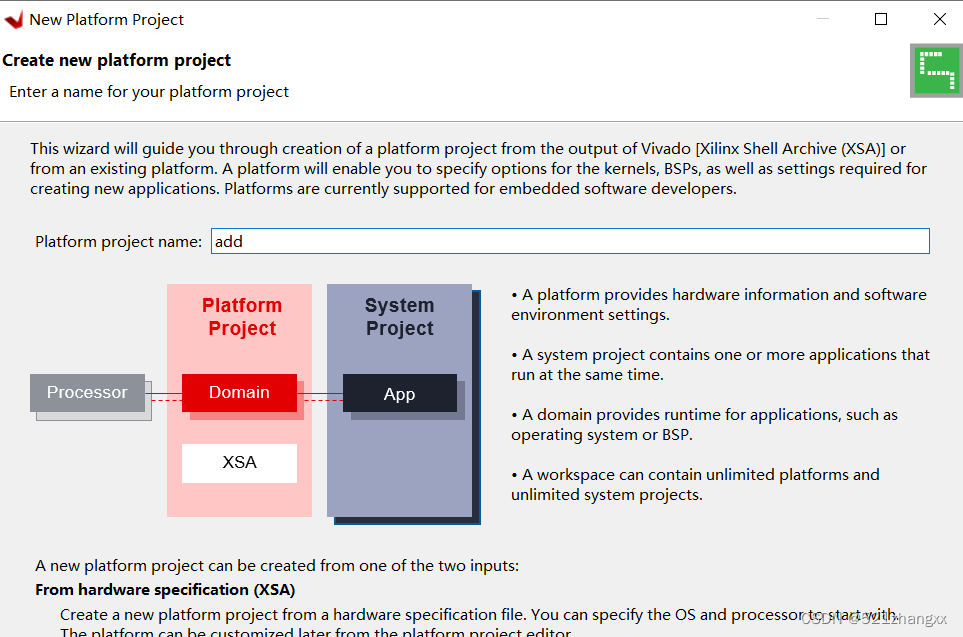

4、打开之后应该会是一个welcome界面,这个时候我们需要如图:New->platform project

输入名称,你的项目名称即可:

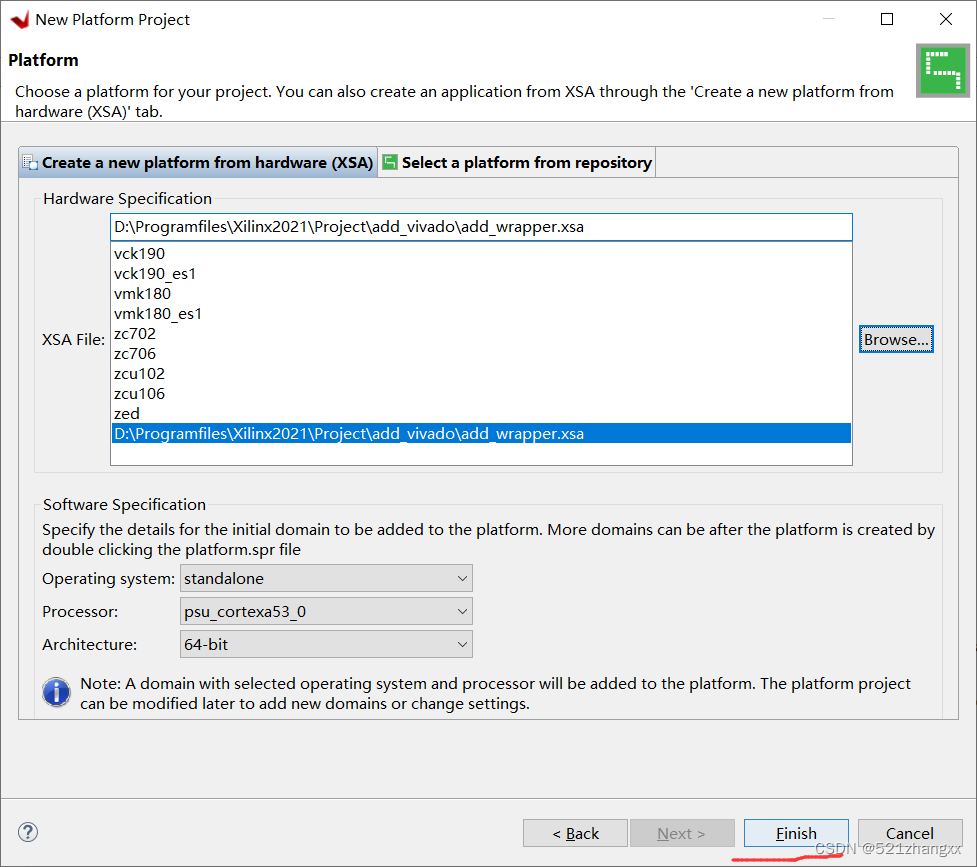

这里应该选择创建一个新的硬件平台,选择Browse,找到你之前生成的.xsa文件,选择它,然后等待,最后选择Finish,然后等待工程的创建

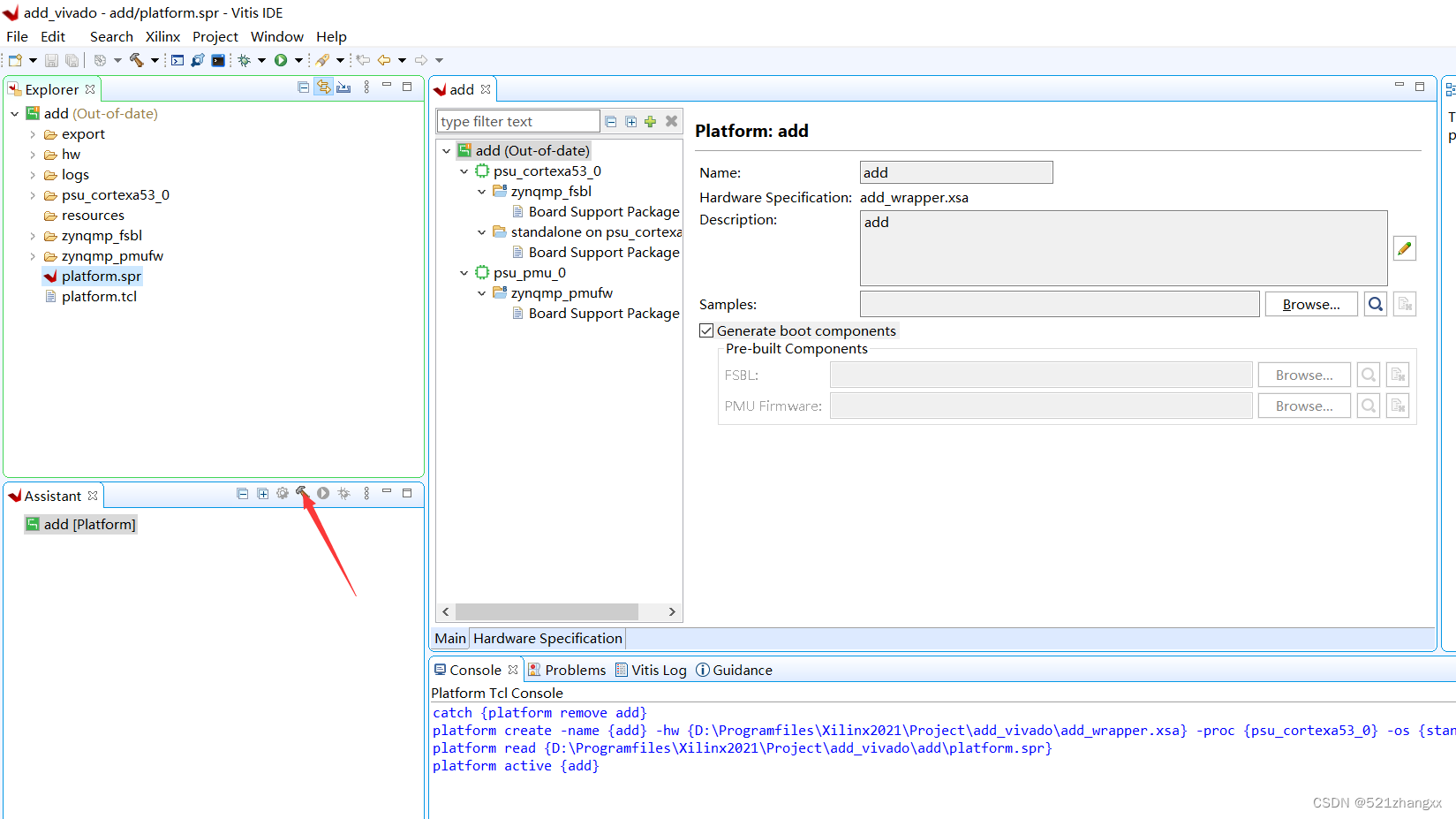

5、工程创建完成后如图:

点击小锤子(build)一下,看看工程是否存在错误,可能需要一定时间

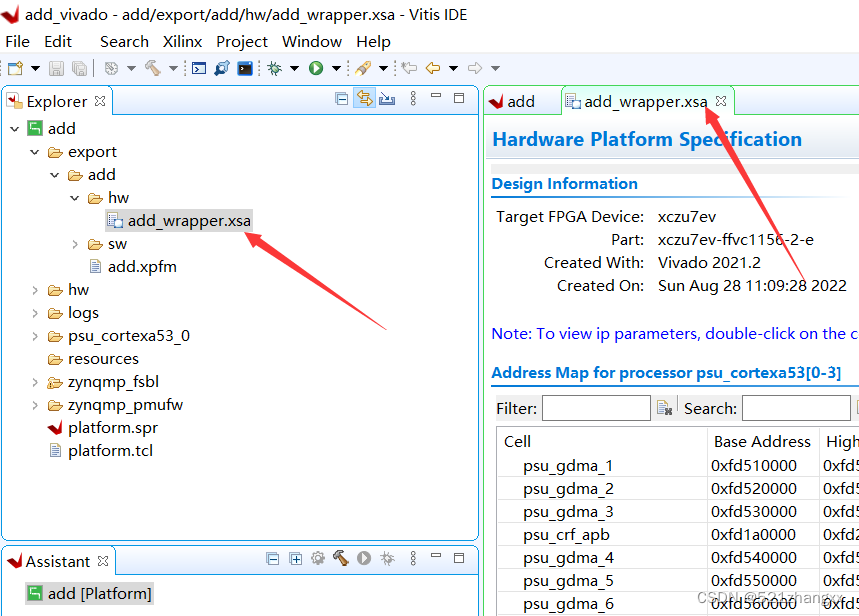

最后,你需要找到你所设计的IP的接口地址,如图:

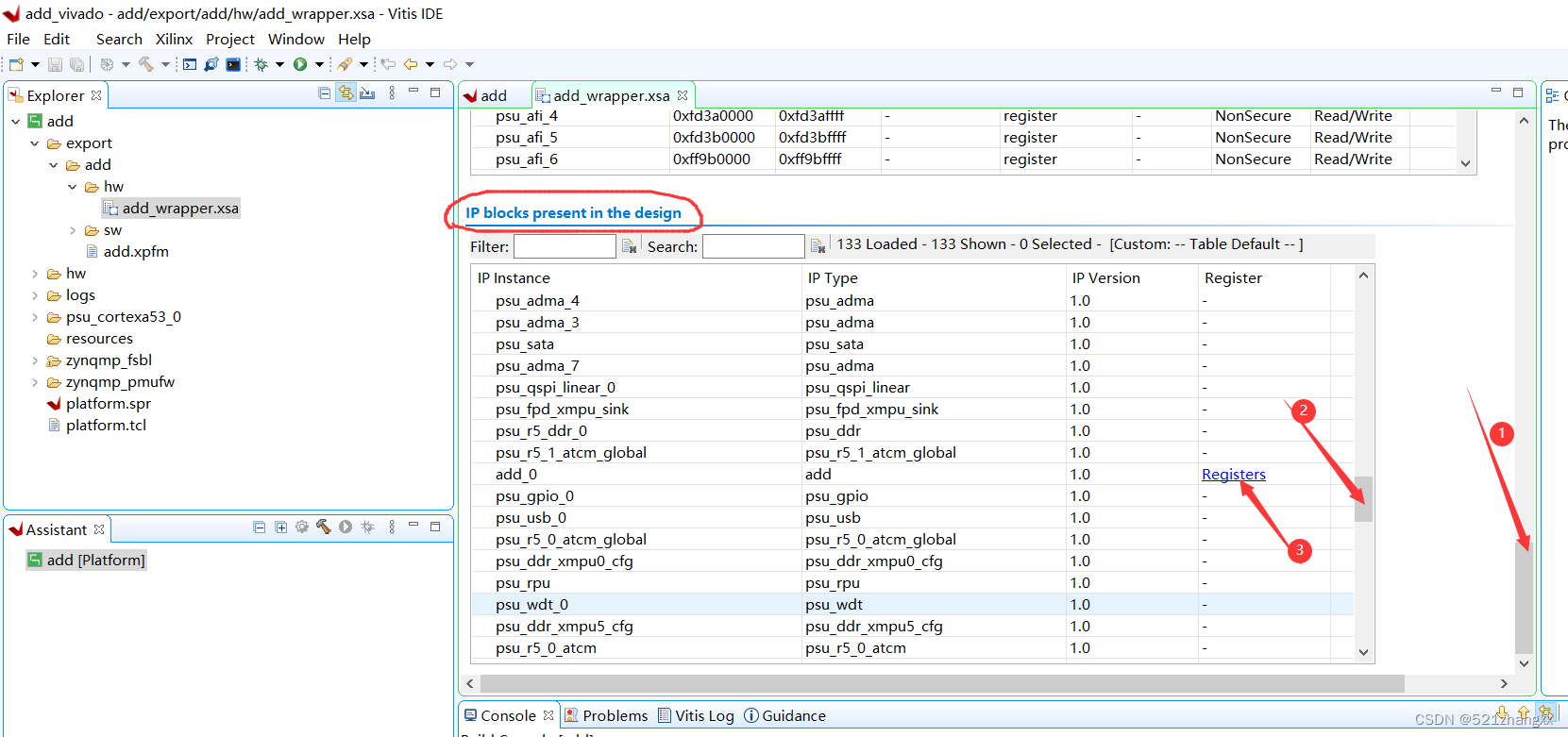

打开.xsa文件,会在右侧发现该文件是一系列的接口映射地址

将最外层滑块滑至最下方,找到IP blocks present in the design,并将该模块滑块向下滑动,寻找到你的IP核的名称,特点是这里有一个可以点击的Registers,并且该IP的名称是你在vitis HLS设计时所使用的名称,我的为add。找到后,点击Registers

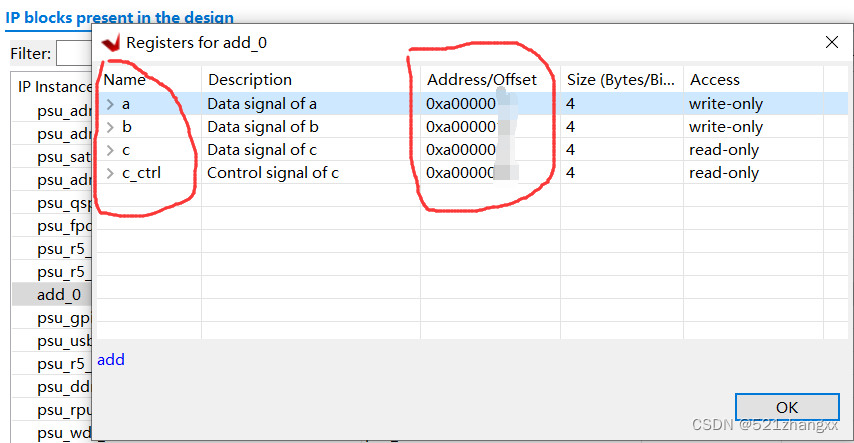

点击后如图,这里时你所设计的IP核各个接口的名称及其地址

里面也有我踩过的坑,创作不易,如有帮助,希望留言点个赞,谢谢。

本文详细介绍了如何在Xilinx 2021.2版本中,使用Vivado进行硬件工程导出,然后在SDK中创建平台项目并进行编译。步骤包括从Vivado导出硬件平台,通过SDK启动新的平台项目,以及查找和查看IP核的接口地址。该教程适用于FPGA开发者进行IP核设计与验证。

本文详细介绍了如何在Xilinx 2021.2版本中,使用Vivado进行硬件工程导出,然后在SDK中创建平台项目并进行编译。步骤包括从Vivado导出硬件平台,通过SDK启动新的平台项目,以及查找和查看IP核的接口地址。该教程适用于FPGA开发者进行IP核设计与验证。

790

790

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?