Xilinx版本:2021.2

PC系统:Windows10

前置要求:你需要有一个IP核,或者自己用vitis HLS生成IP核

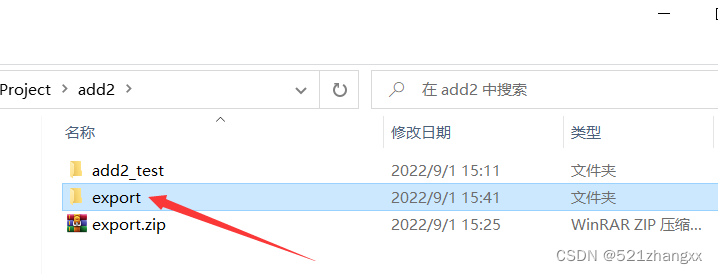

1、首先解压IP核:

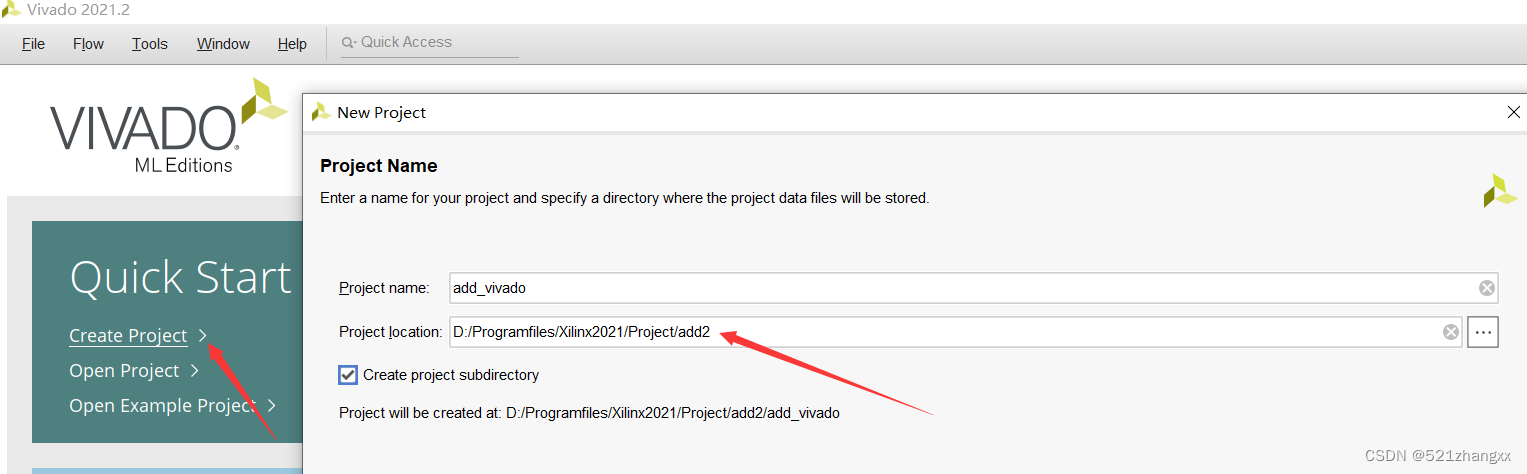

然后打开你的vivado软件,点击Create Project,之后设置项目名称以及项目位置。

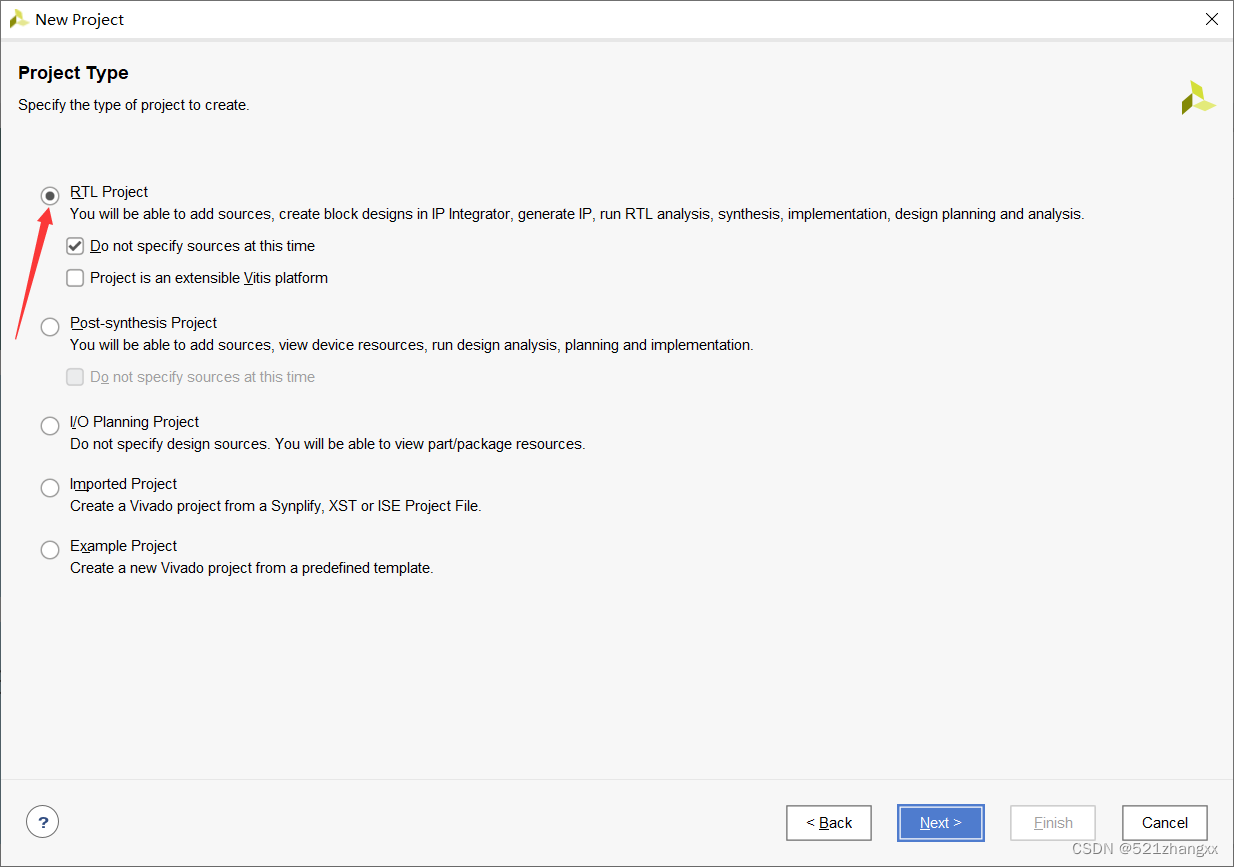

选择RTL 项目

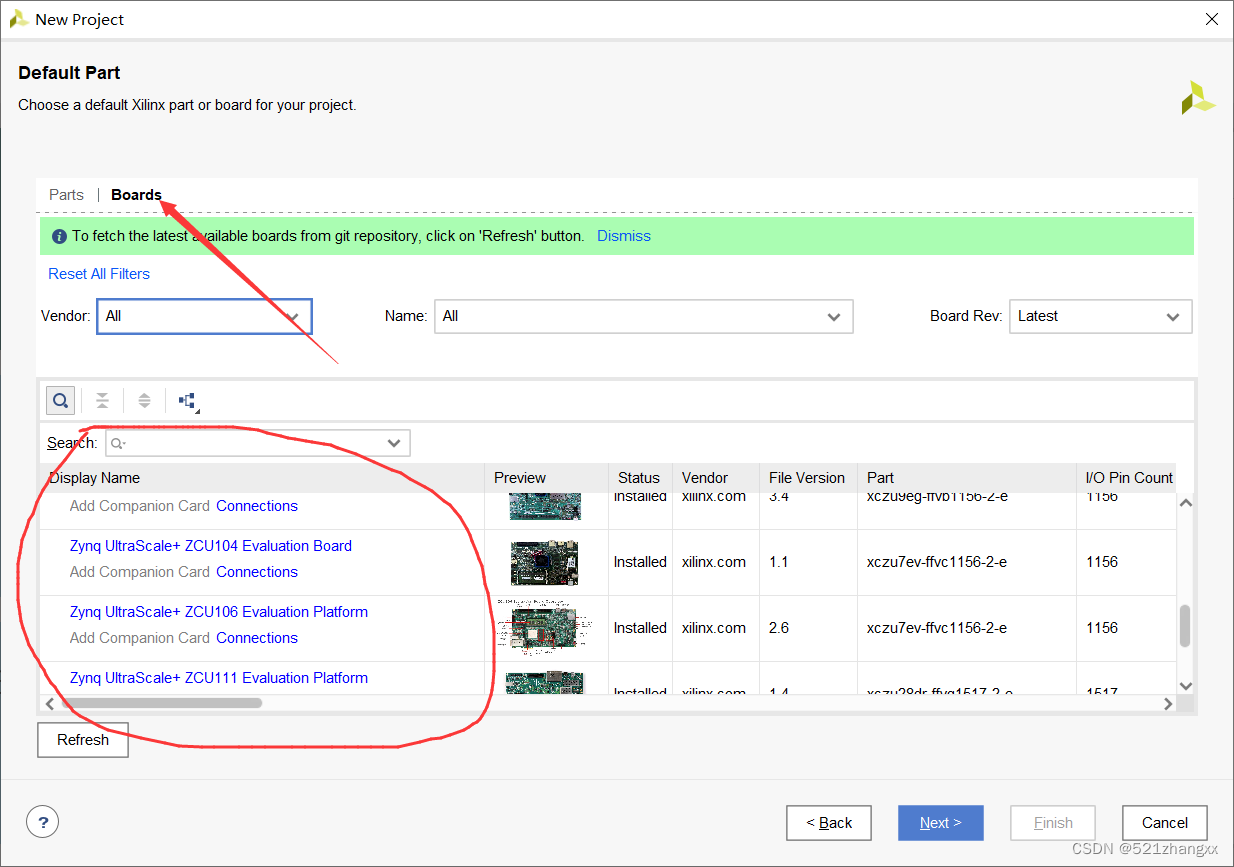

选择你的FPGA板子的型号,最后选择finish,等待工程的创建。

2、导入IP核,选择Create Block Design,并将名字名名为你工程的名字即可,之后点击OK

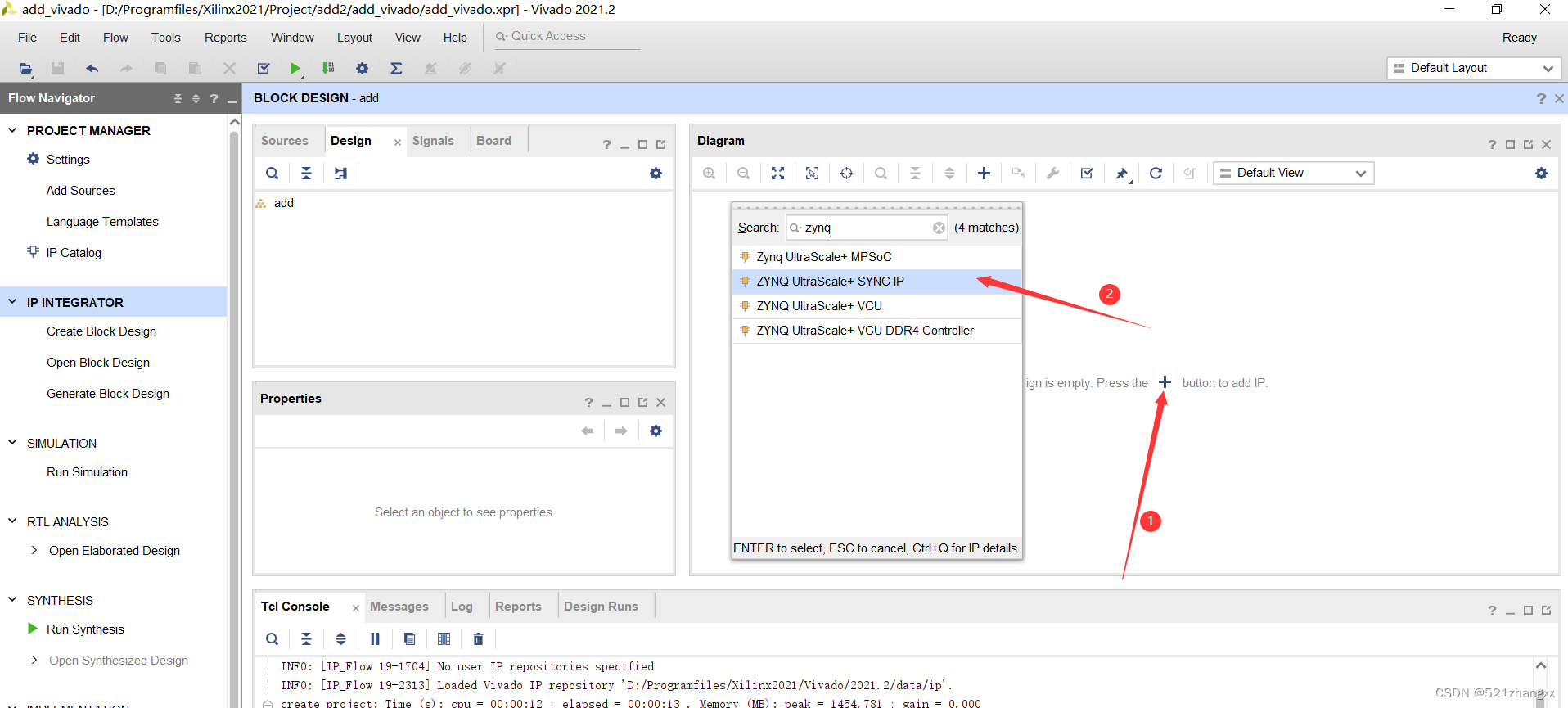

完成之后右侧就会出现大片空白,点击加号,此意为导入硬件IP核。

首先,因为本文所涉及的IP核都是基于zynq的,所以这里需要先添加一个zynq的IP核,本文选择了其中一个

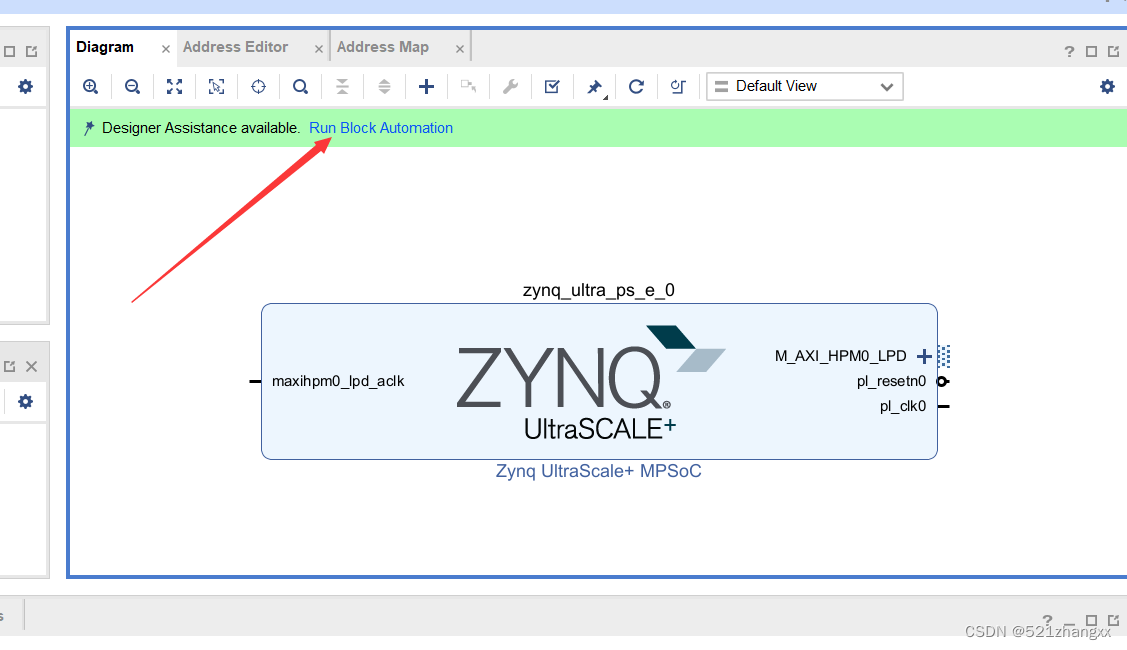

选择完成之后如图所示,如果界面中出现Run Block Automation,点击运行即可,如果没有请忽略。

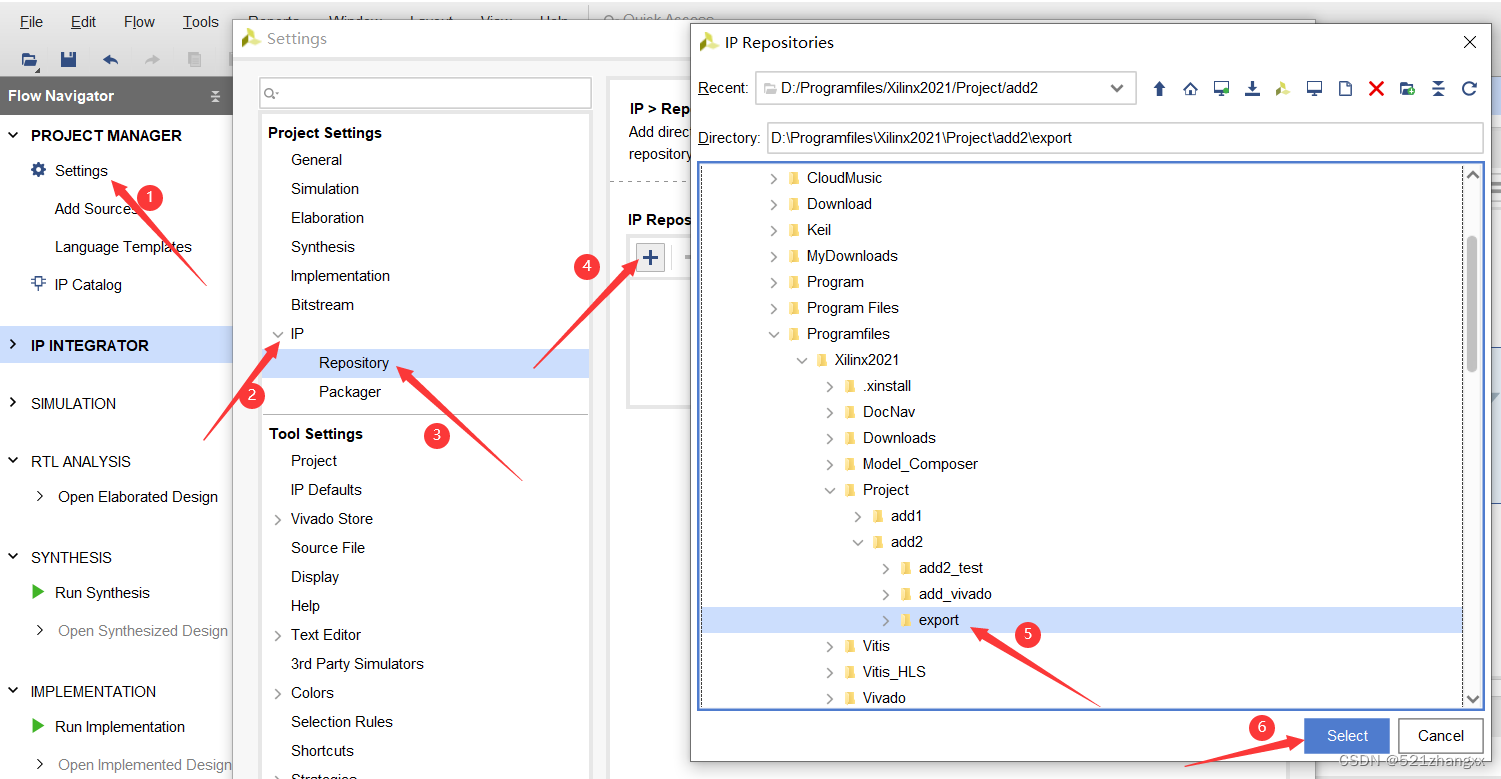

再然后就可以导入我们设计的IP了,如图:点击setting->IP->Repository再点击“加号”,找到你刚刚解压的IP核文件夹(第一张图),选择它

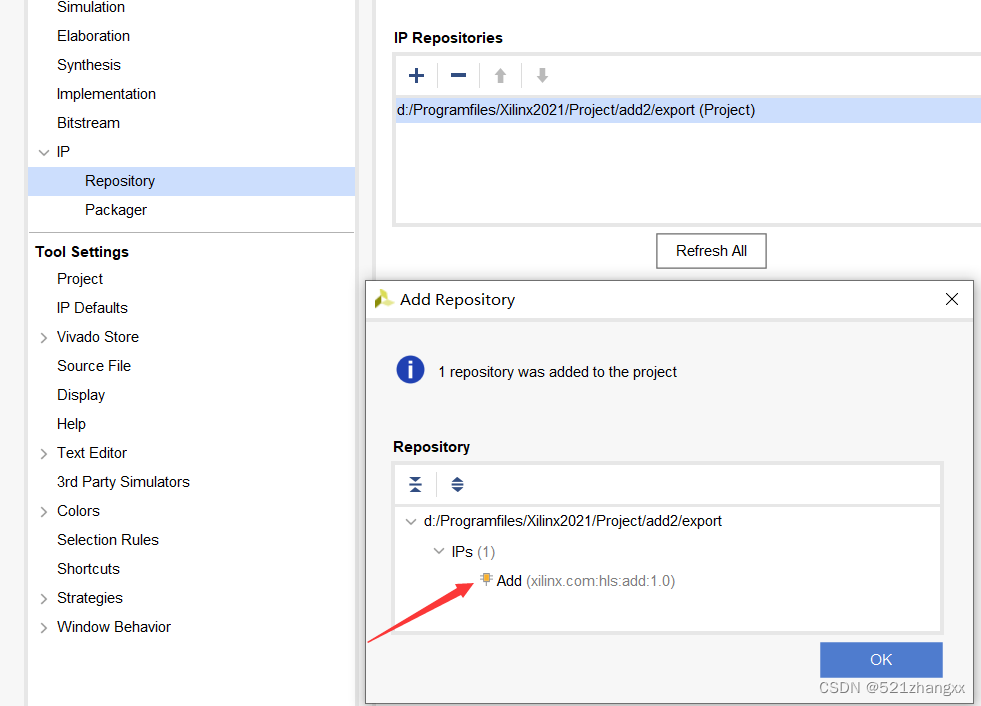

然后这里就会出现你所设计的IP核,点击OK。然后我们就将自己的IP核导入了库。

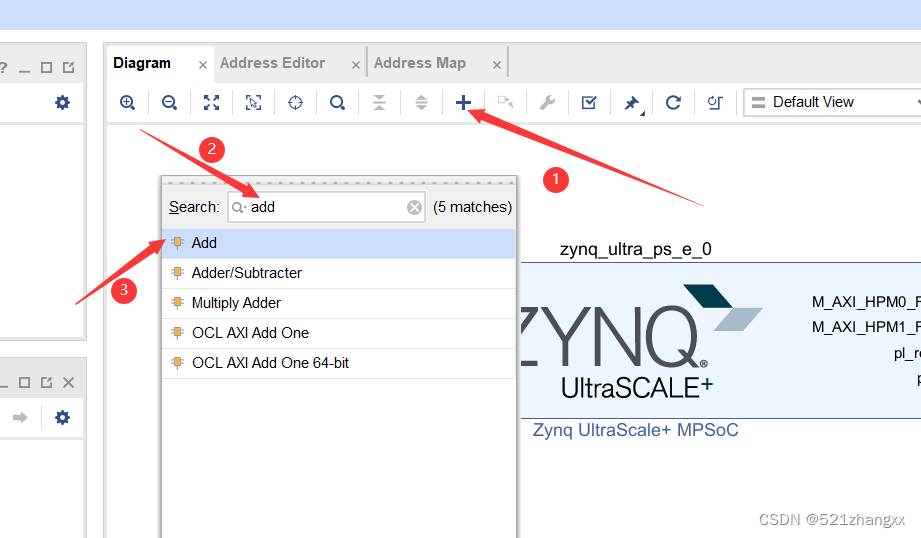

点击加号,搜索自己刚刚添加的IP核名称,并选择它

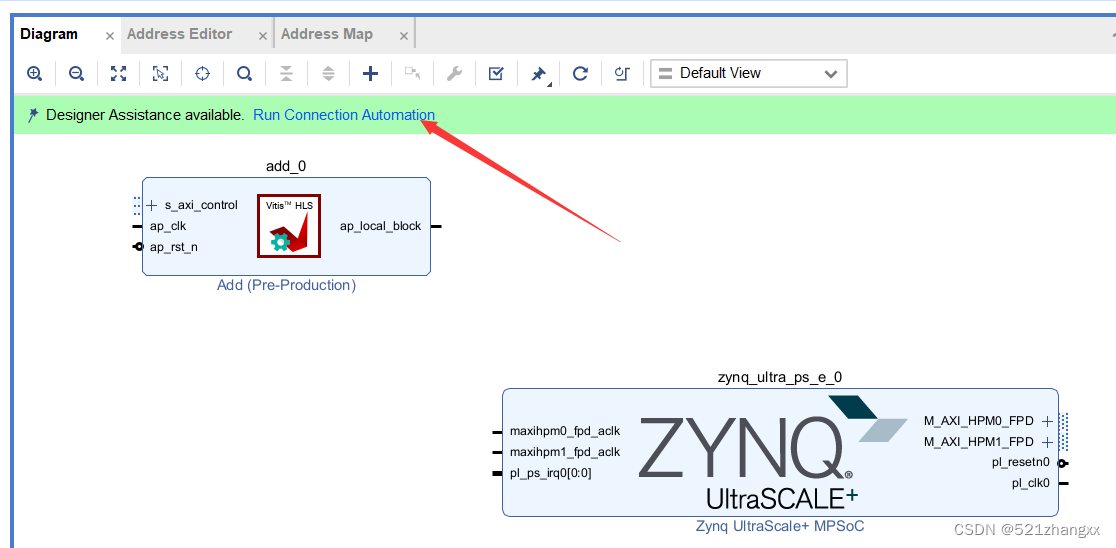

之后你就会发现,你的IP和已经导入了,如图:之后点击Run Connection Avtomation

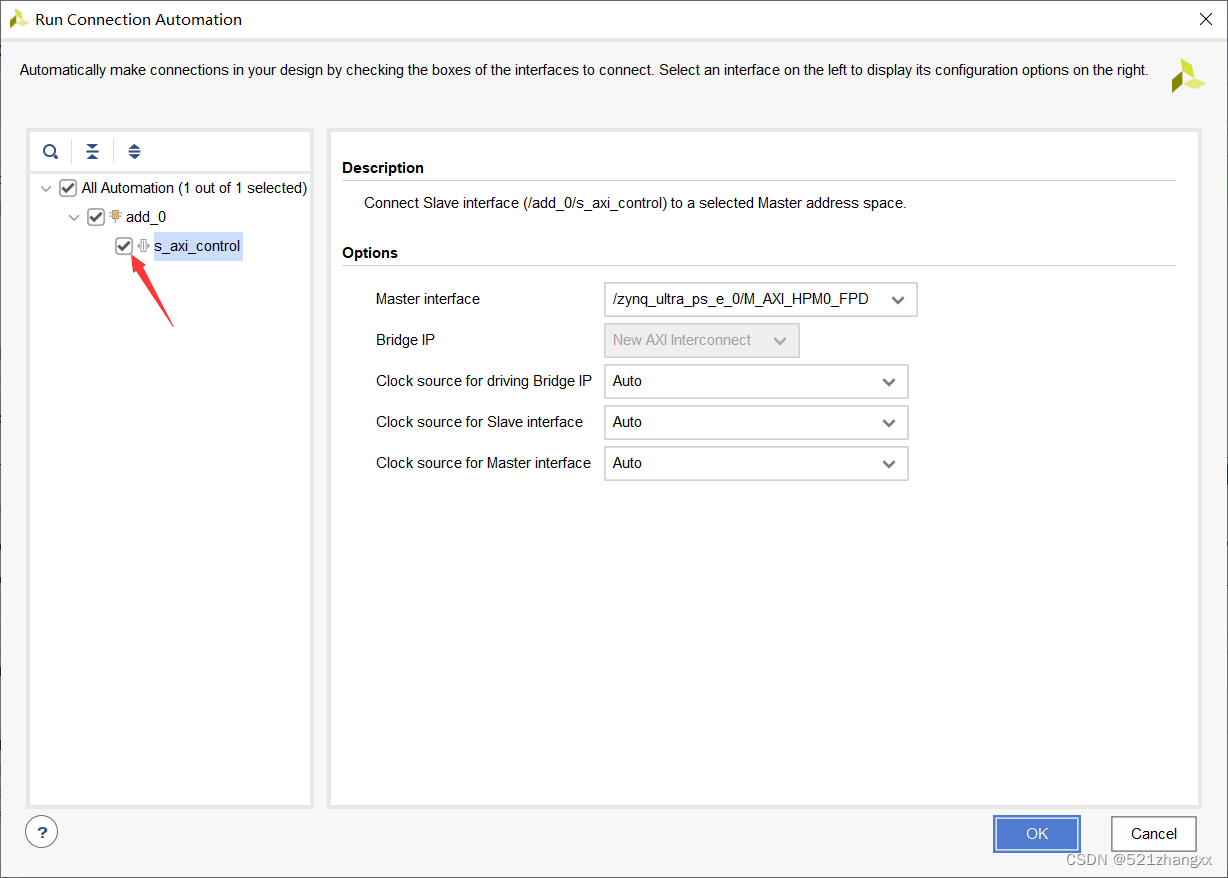

点击OK

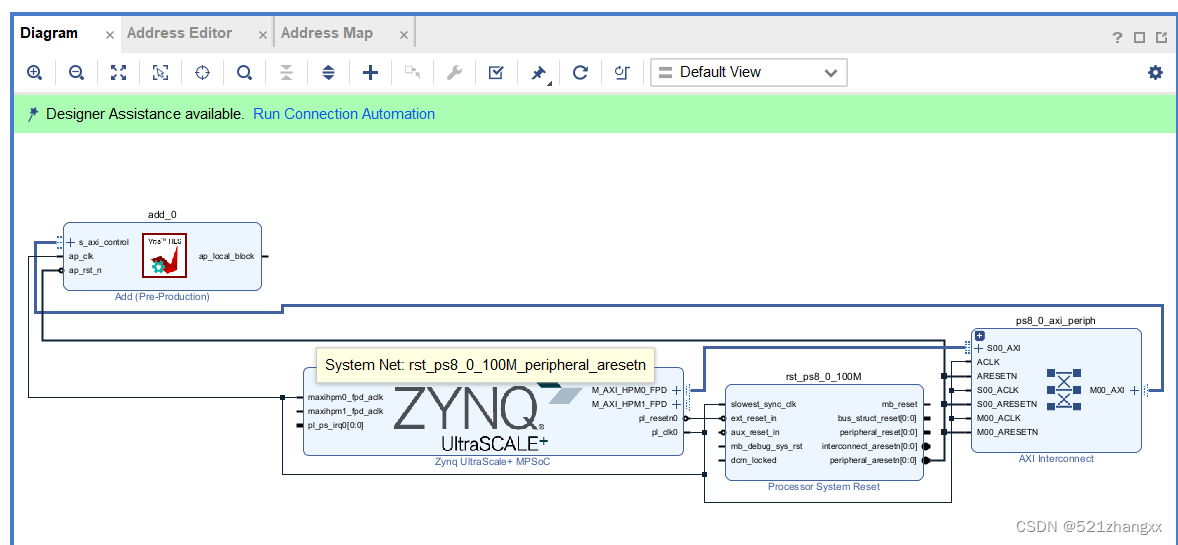

结果如图:我们发现线已经连好

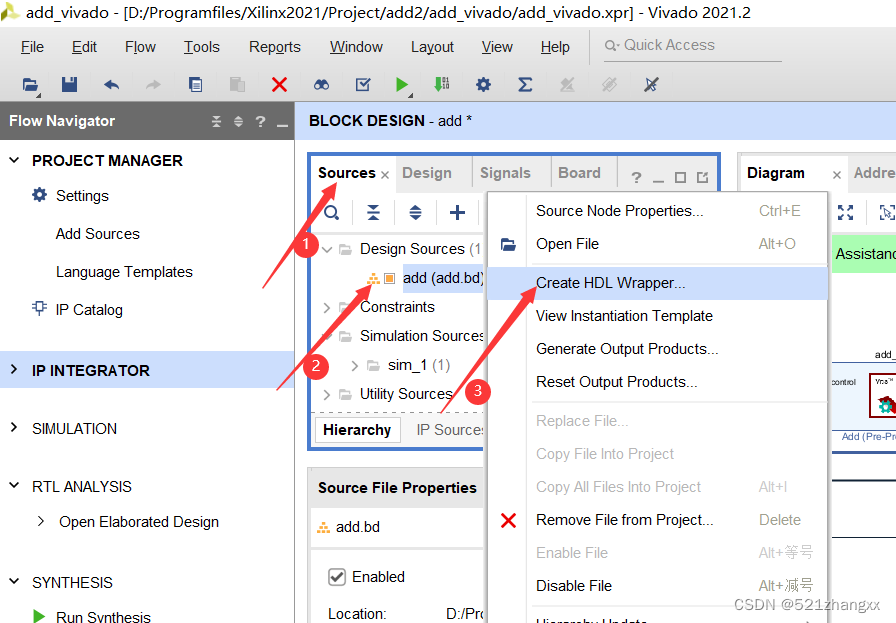

3、创建顶层:Create HDL wrapper

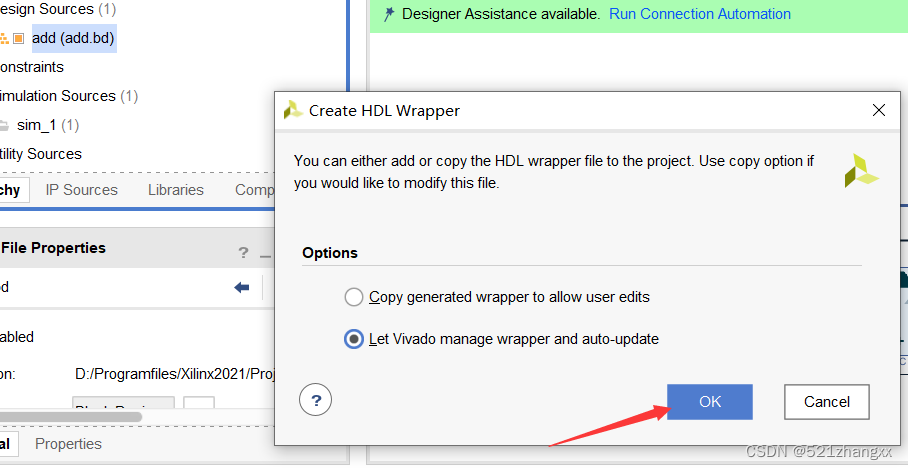

点击OK,保持默认

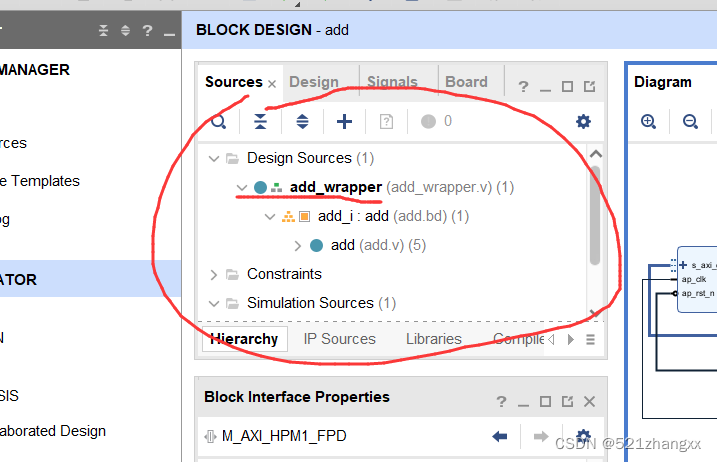

完成之后如图:

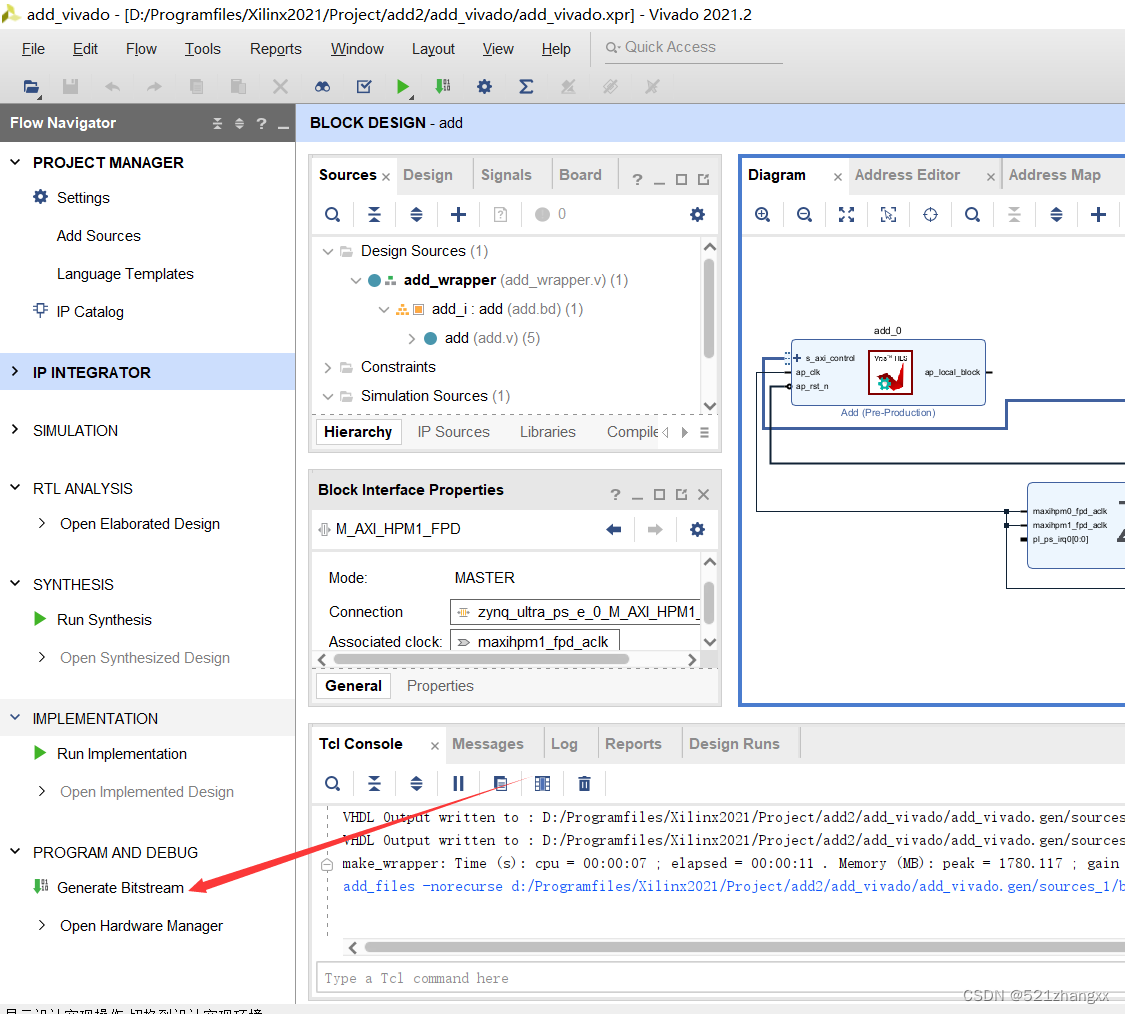

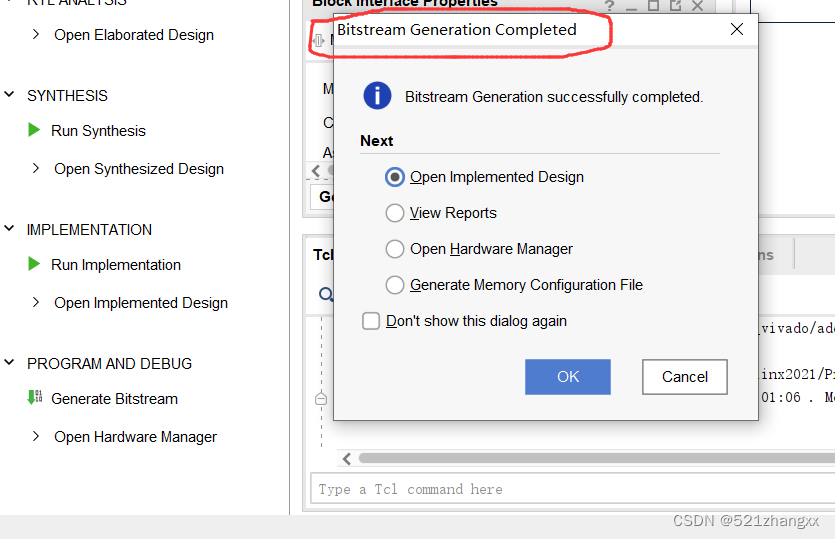

4、生成bit流文件:点击运行Generate Bitstream,其他若无特殊要求,默认即可。这里等的时间比较长,大约十几到三十分钟。如果IP比较大、比较麻烦,可能会更长。

直到出现该弹窗,表示bitstream已经生成

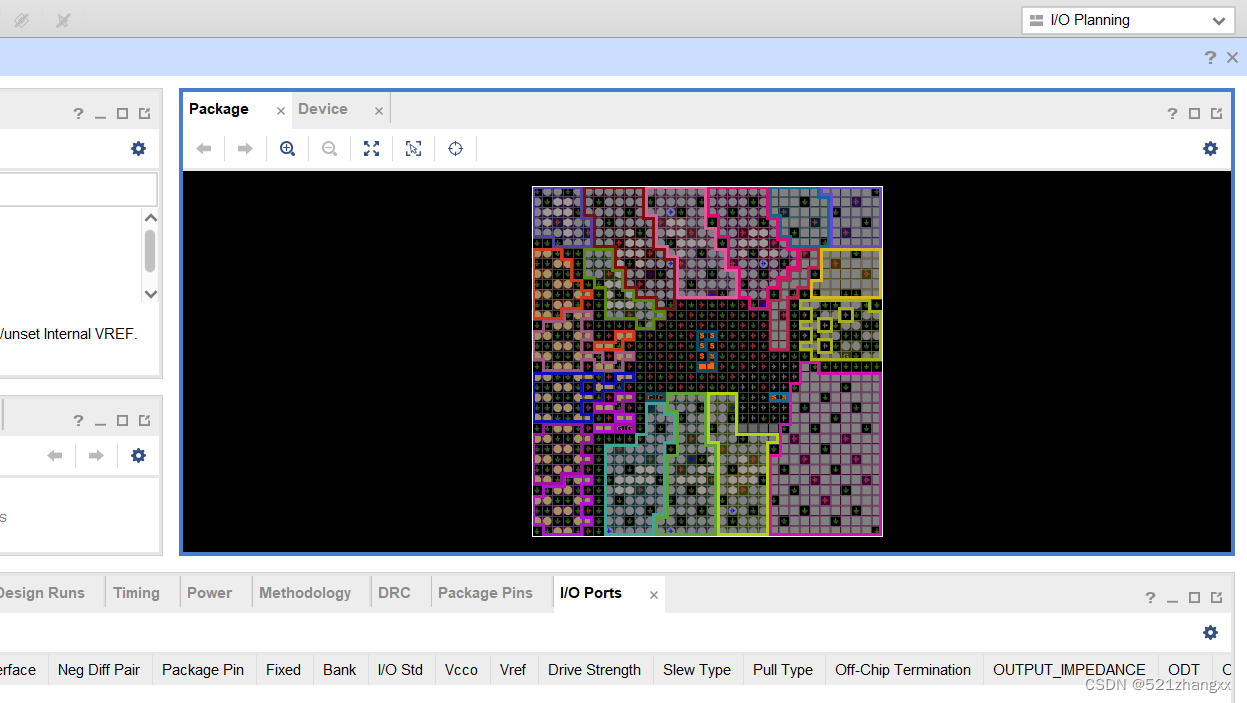

点击OK后如图所示:

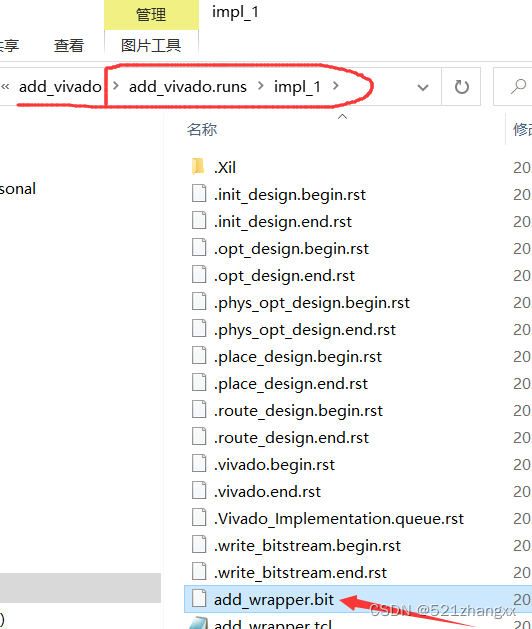

之后在你的项目文件夹中打开add_vivado.runs->impl_1,就可以找到相应的.bit文件

如此,该IP核的bitstream流文件就完成了,就可以拿到FPGA用了。

vivado 导入IP核并生成bit流文件

最新推荐文章于 2025-04-19 12:10:38 发布

1695

1695

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?