Signal Measurement Result

一: Clock_Signal Integrity

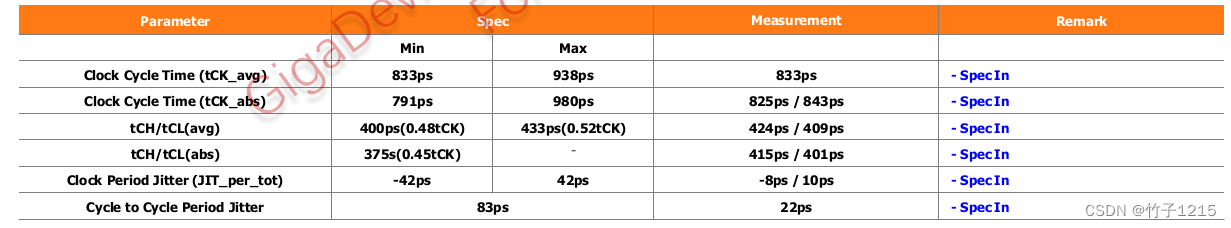

时钟周期(clock period):平均值和绝对值

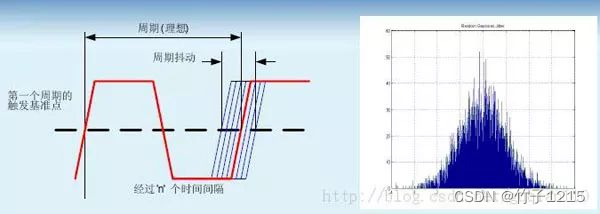

周期抖动(Period Jitter):周期抖动率(Period Jitter)测量时钟输出传输偏离其理想位置的最大偏离。Period Jitter代表周期差抖动的上下边界。

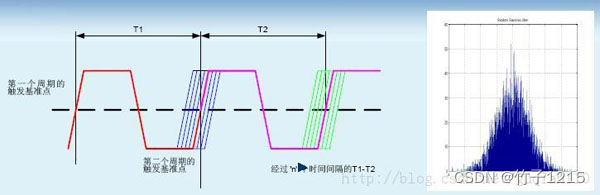

周期差抖动率(cycle-to-cycle jitter)是两个相邻周期的时间偏差。它总是小于周期抖动(period jitter)

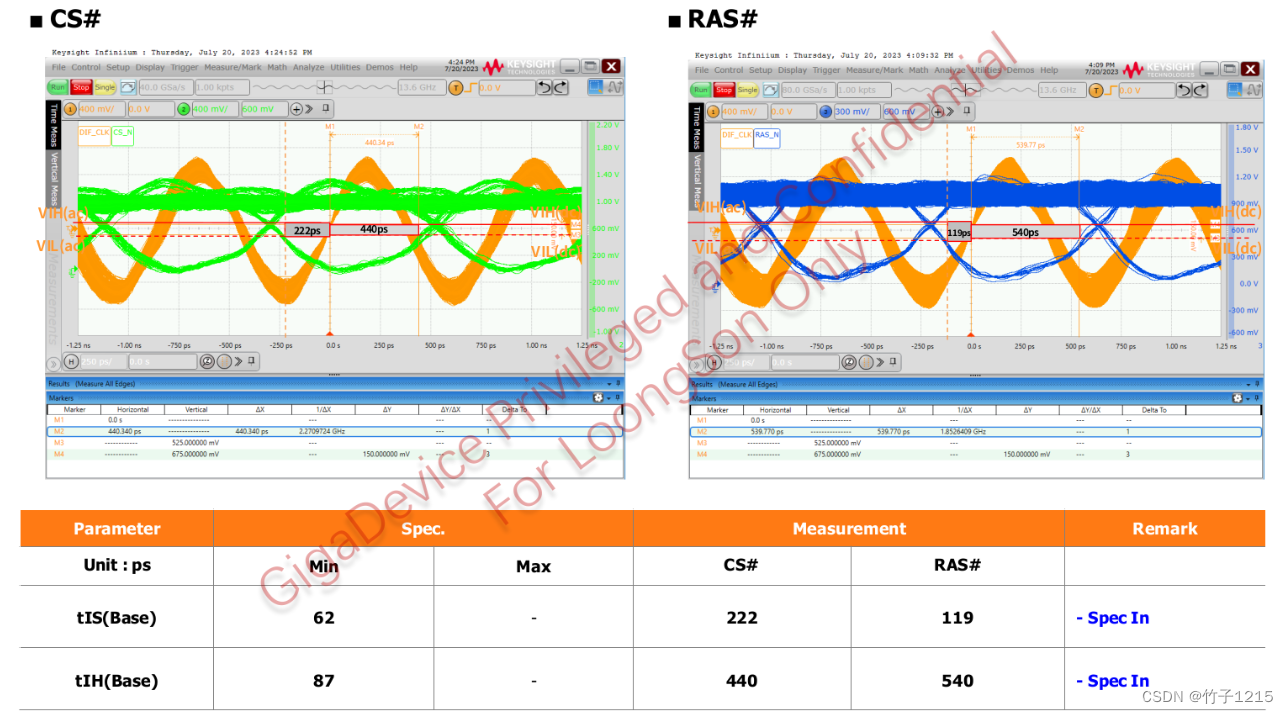

二:Command & Address Signal Integrity Result

Addr/Cmd Bus意思是地址/命令总线,都是时钟的上升沿有效,其中命令由:/CS(片选),/RAS, /CAS,/WE(写使能)决定,比如:“读”命令为:LHLH,“写”命令为:LHLL等。操作命令很多,主要是NOP(空超作),Active(激活),Write,Read,Precharge (Bank关闭),Auto Refresh或Self Refresh(自动刷新或自刷新)等(细节请参考:Jedec规范JESD79)。Data Bus是数据总线,由DQS的上升沿和下降沿判断数据DQ的0与1。

命令信号的波形和时序参数:需要测试/RAS,/CAS,/WE,/CS的信号品质,如Vmax(最大电压值),Vmin(最小电压值),Slew Rate(斜率),Ringback(回沟)等;还需要测试相对于时钟边沿的Setup Time(建立时间)和Hold Time(保持时间)。测试相对于时钟边沿的建立时间和保持时间时,需要注意参考电平的位置和最差情况波形的捕获。如图3的/CS建立时间和保持时间的测试就没有测试出最差的建立时间和保持时间值,为此,我们需要用眼图累积的方式设法找到最差情况下的建立时间和保持时间。

参考波形如下图

2930

2930

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?