问题1

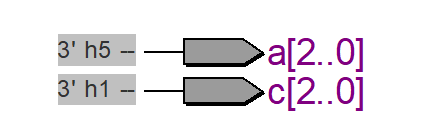

module aa(output [2:0] a,output [2:0] c);

//wire [2:0] a, c; // Two vectors

assign a = 3'b101; // a = 101

assign b = a; // b = 1 implicitly-created wire

assign c = b; // c = 001 <-- bug

endmodule

未定义b直接赋值并不会报错,只会报worning

Warning (10236): Verilog HDL Implicit Net warning at aa.v(4): created implicit net for “b”

Warning (10236): Verilog HDL Implicit Net warning at aa.v(4): created implicit net for “b”

但是Adding default_nettype none would make the bug more visible.然后就报错了。

问题2

assign out[7:0] = in[0:7]; does not work because Verilog does not allow vector bit ordering to be flipped.

问题3

记得位拼接运算,每一个原始数据需要用大括号,乘以倍数后还得再一个大括号。当然,最外层还得大括号。

assign out = {{24{in[7]}},in[7:0]};

问题4

always @(*) begin

case(sel)

2'b00:q=q1;

2'b01:q=q2;

default:q=q3;

endcase

end

2178

2178

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?