这次的案例来源于小编我上周去我司的韩国分部出差的时候遇到的一个问题,那边的仿真同事马冬梅由于失恋心情不好请假一个月调整状态了,那边的仿真的案子就顺理成章的让我去接了。虽然小编我很不愿意做的,主要是不给小编我加money啊,还让我干那么多的事情啊。不过谁让我们是打工的牛马的,吐槽归吐槽,还是要接着做的。

具体的仿真步骤如下所所示:

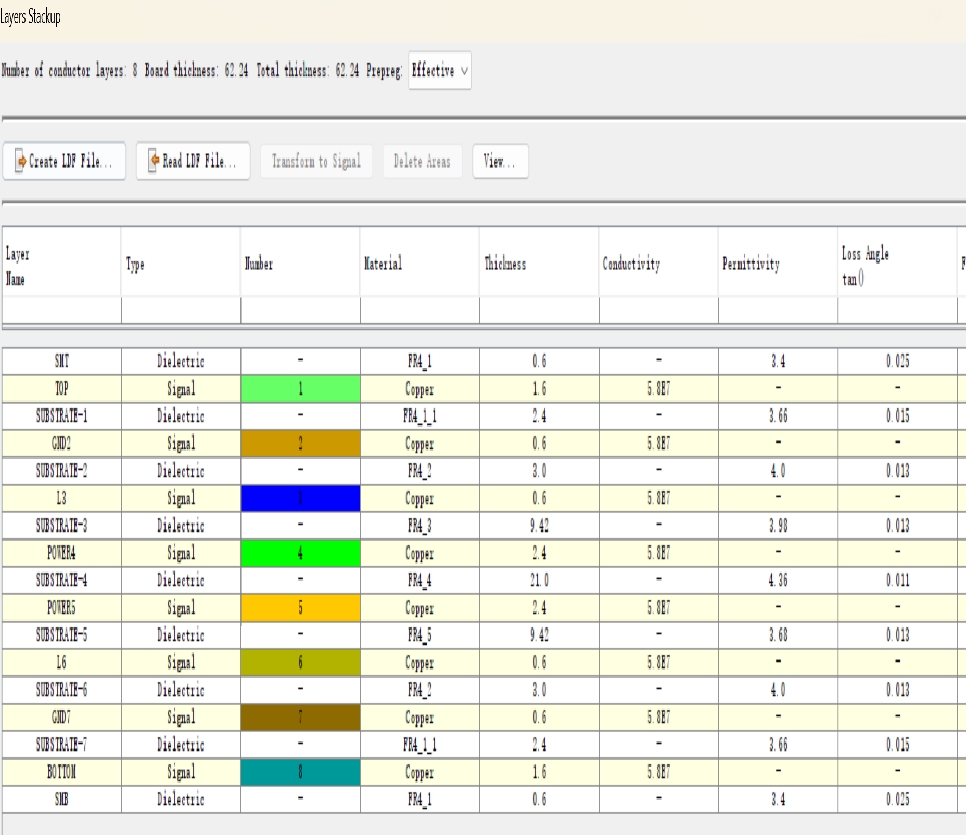

1,Layers –stackup:.

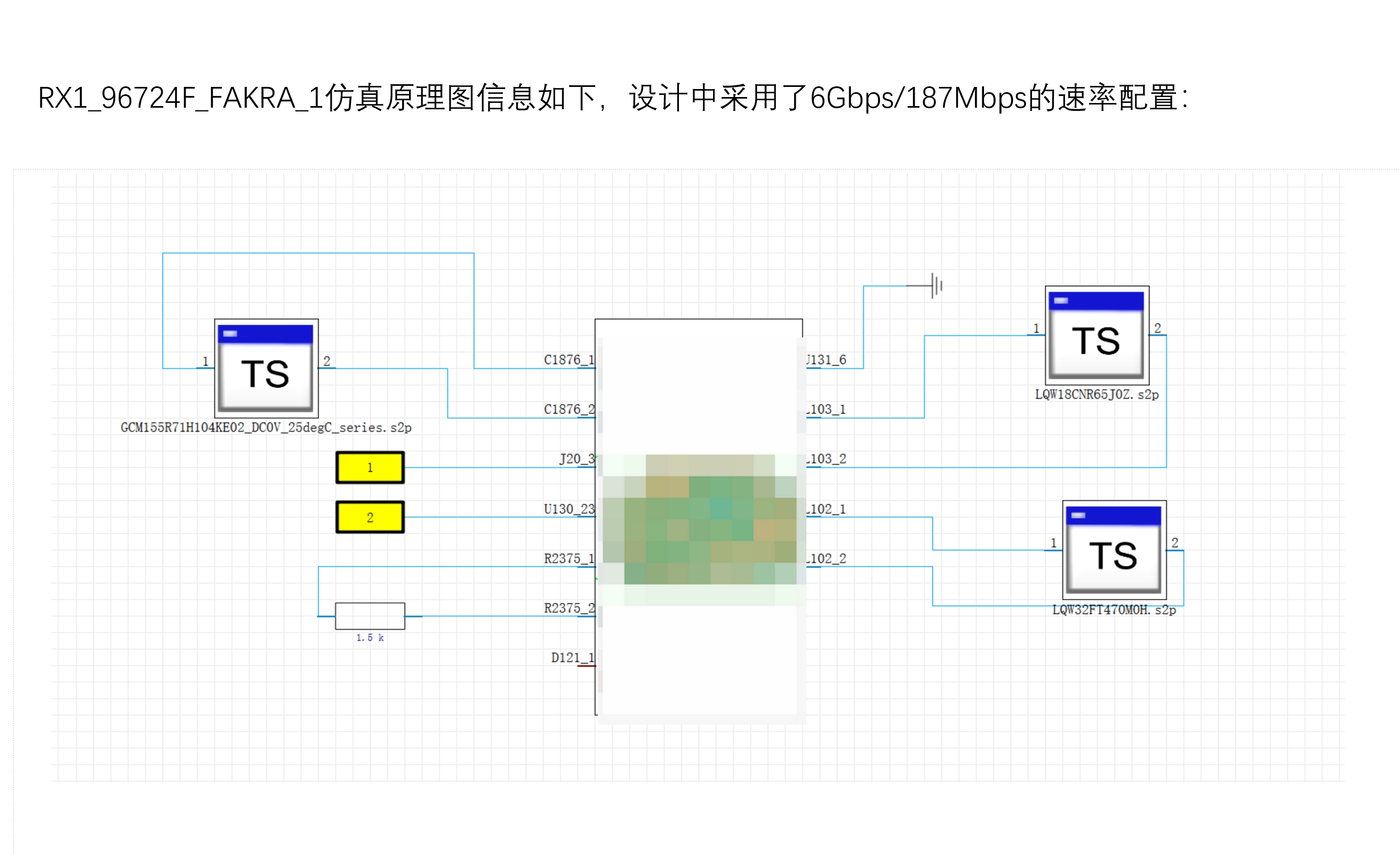

RX1_96724F_FAKRA_1仿真原理图信息如下,设计中采用了6Gbps/187Mbps的速率配置:

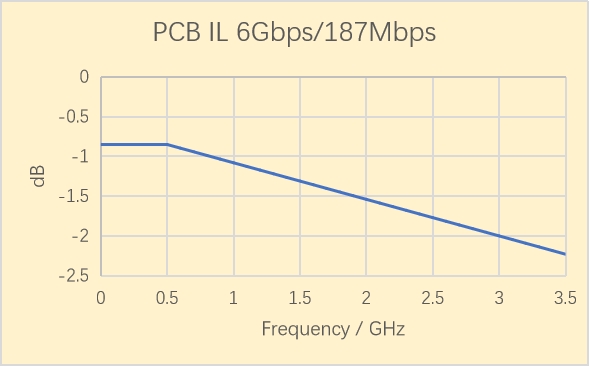

IL的limited:

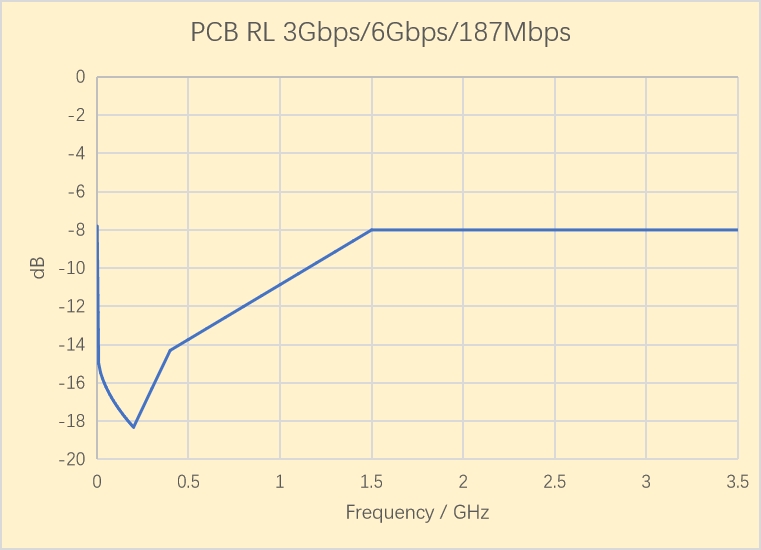

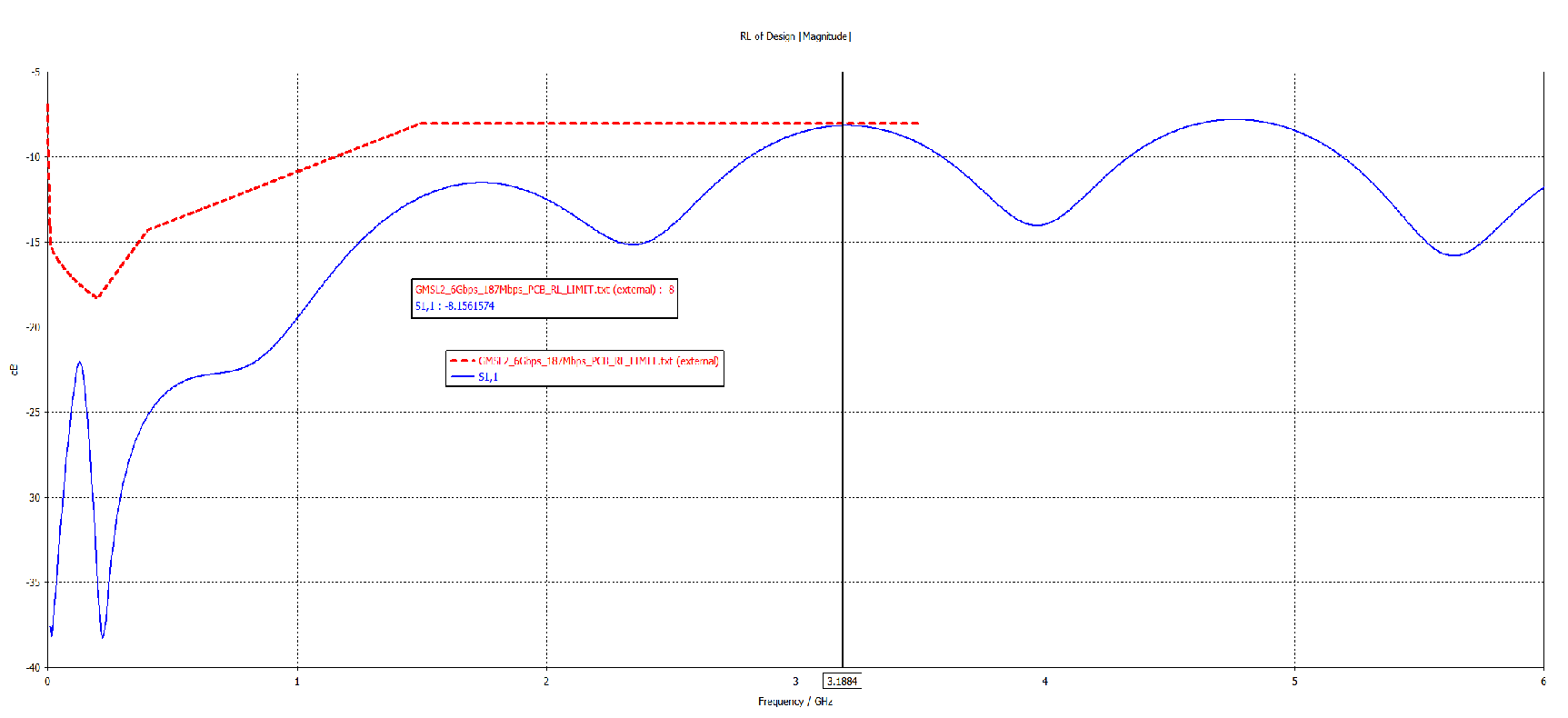

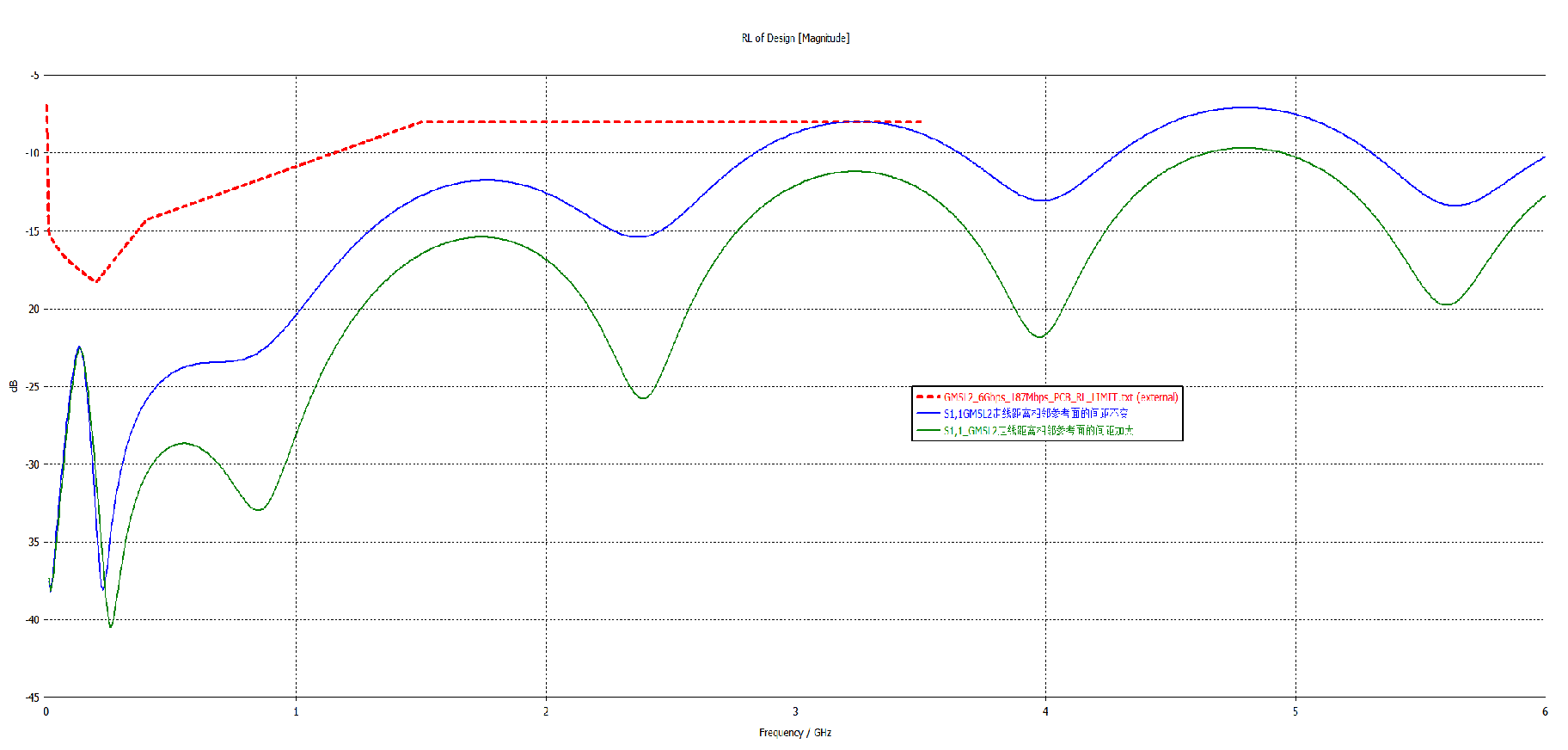

RL的limited:

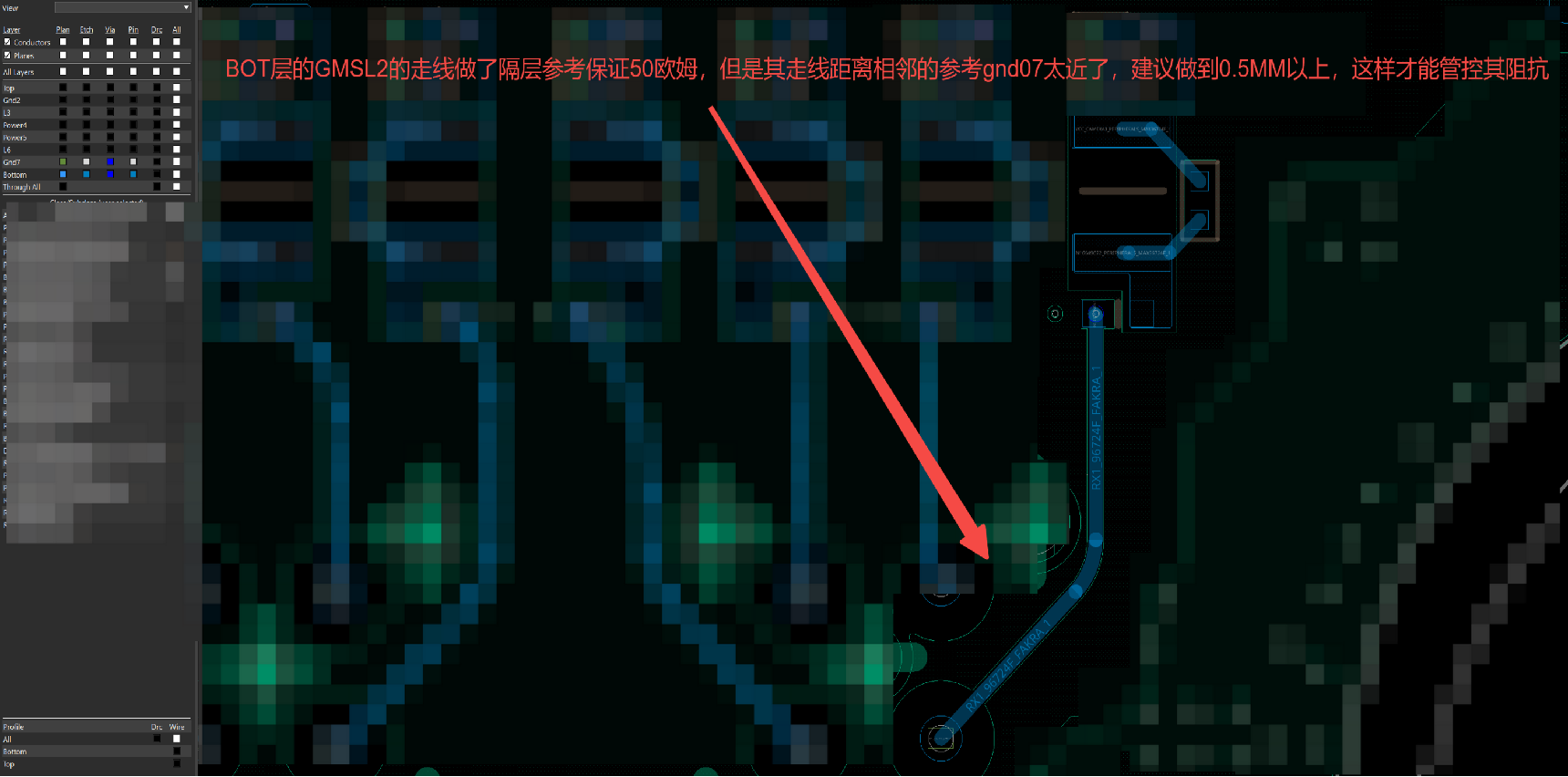

RX1_96724F_FAKRA_1--Return Loss:结果显示,板级设计裕量不是很充足,很接近限值曲线了。

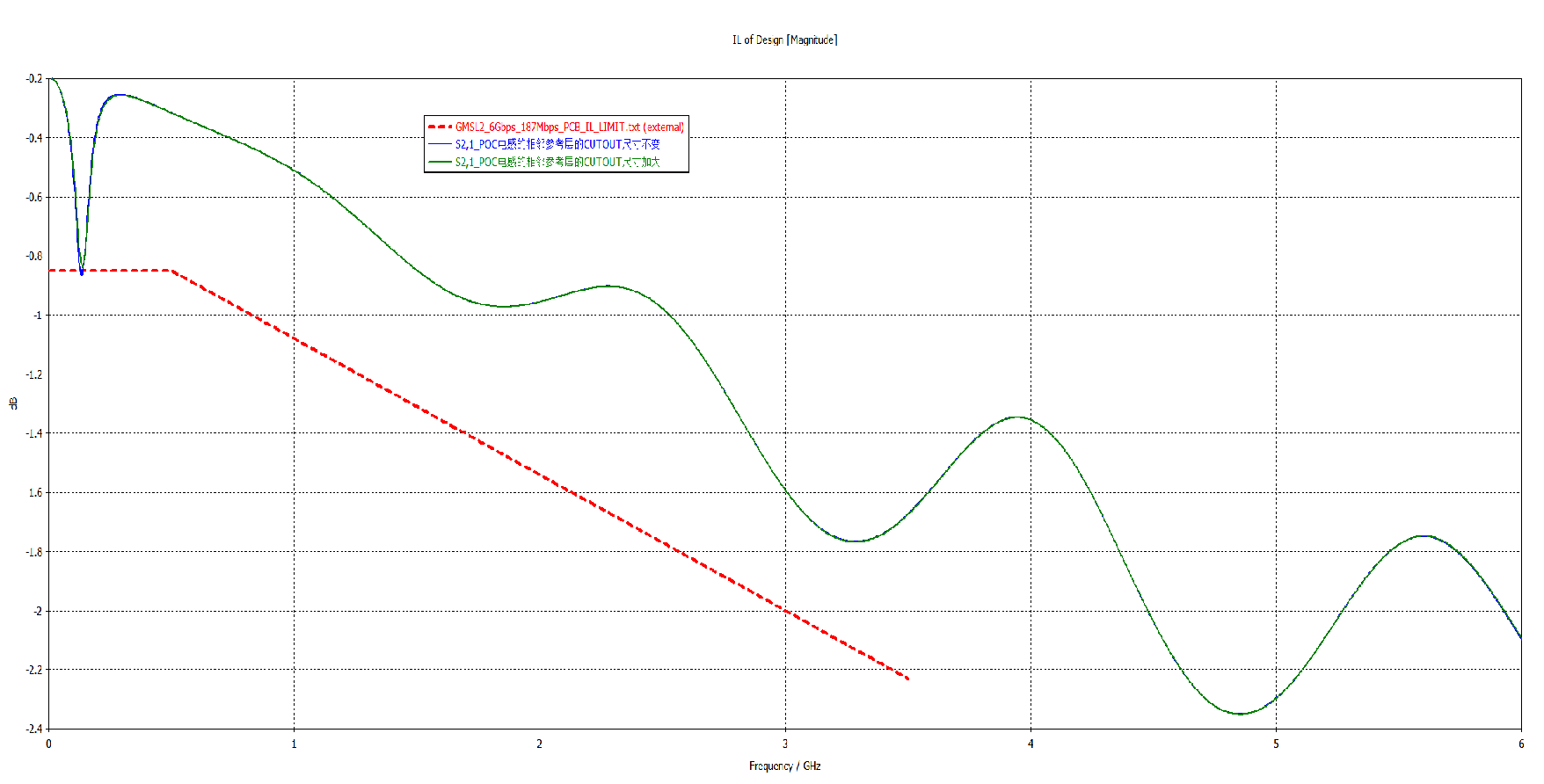

RX1_96724F_FAKRA_1--Insertion Loss:结果显示的是NO PASS ,在低频段的时候是不满足GMSL2手册的要求的

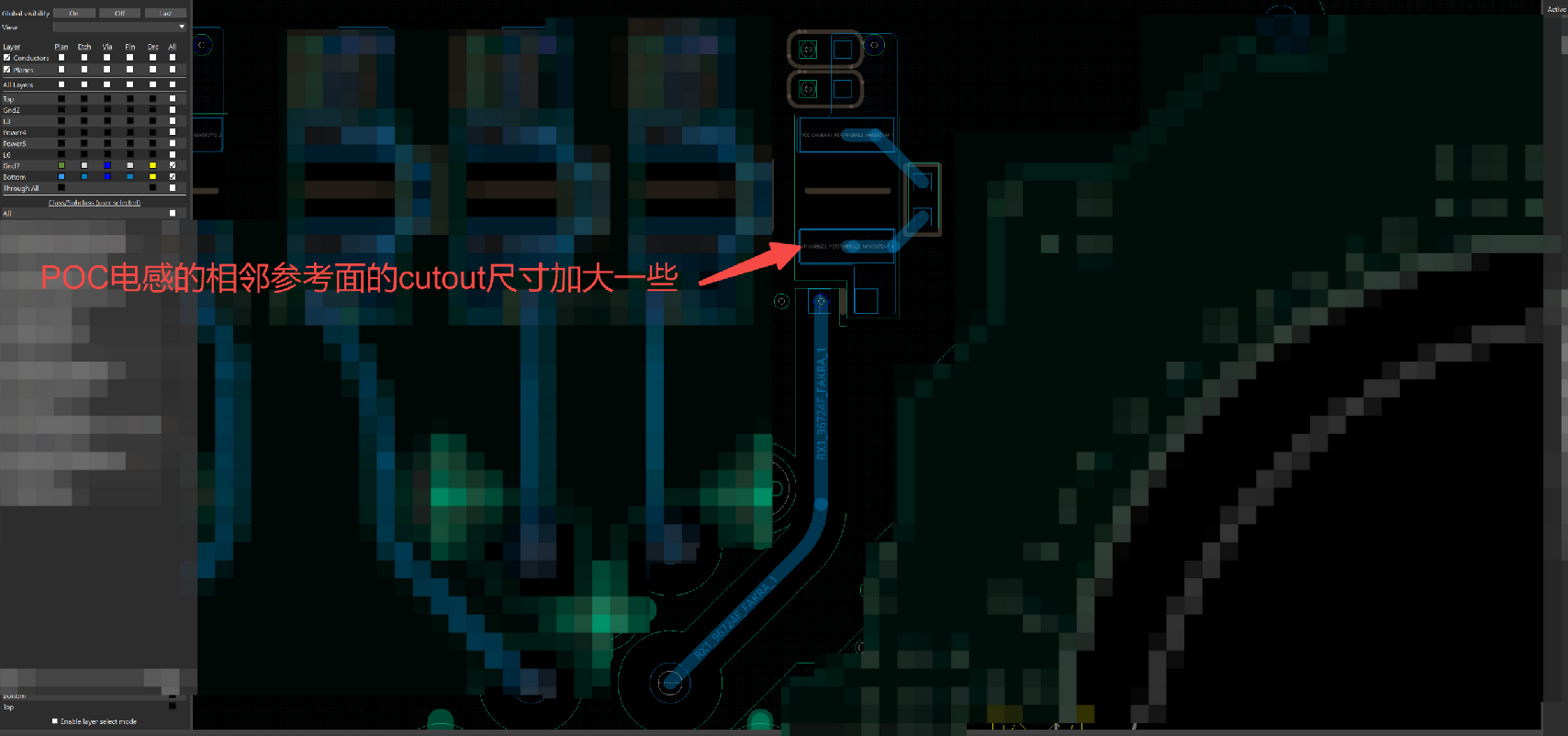

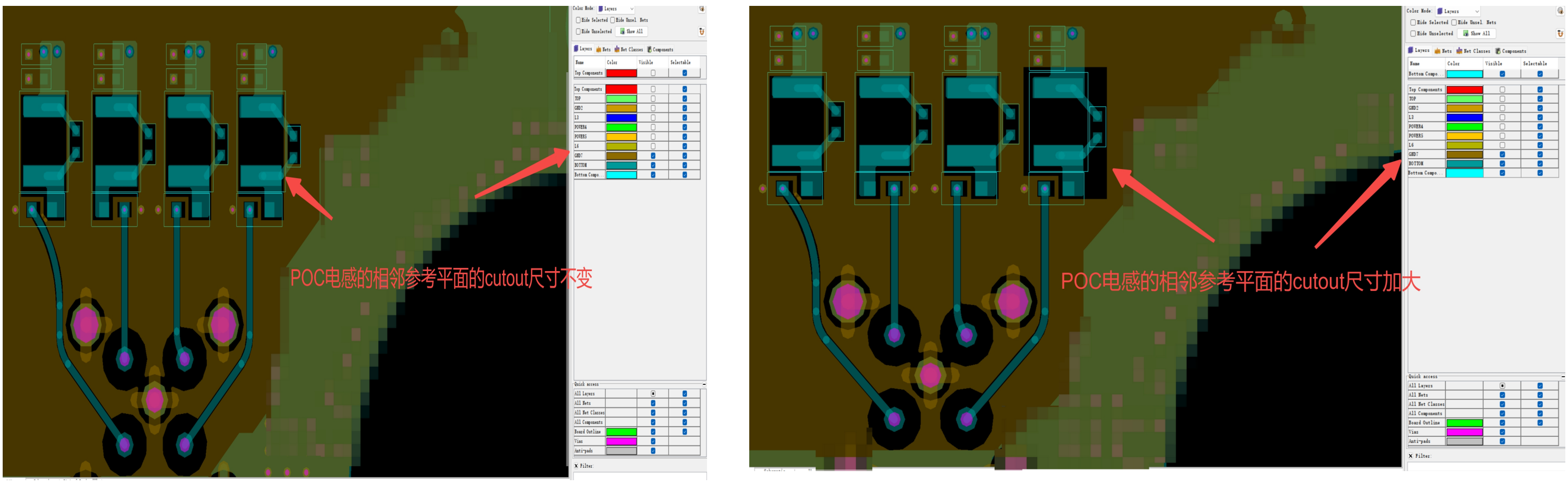

分析原因:低频段IL不满足手册很多可能是由于我们单板POC电路上的二级电感部分PCB设计上没有优化好造成的,例如二级电感的上面的铜皮不能铺铜太多了,还有就是我们需要保证POC电感的挖空尺寸是其焊盘WG值的1.75倍,(村田手册上有推荐值的)

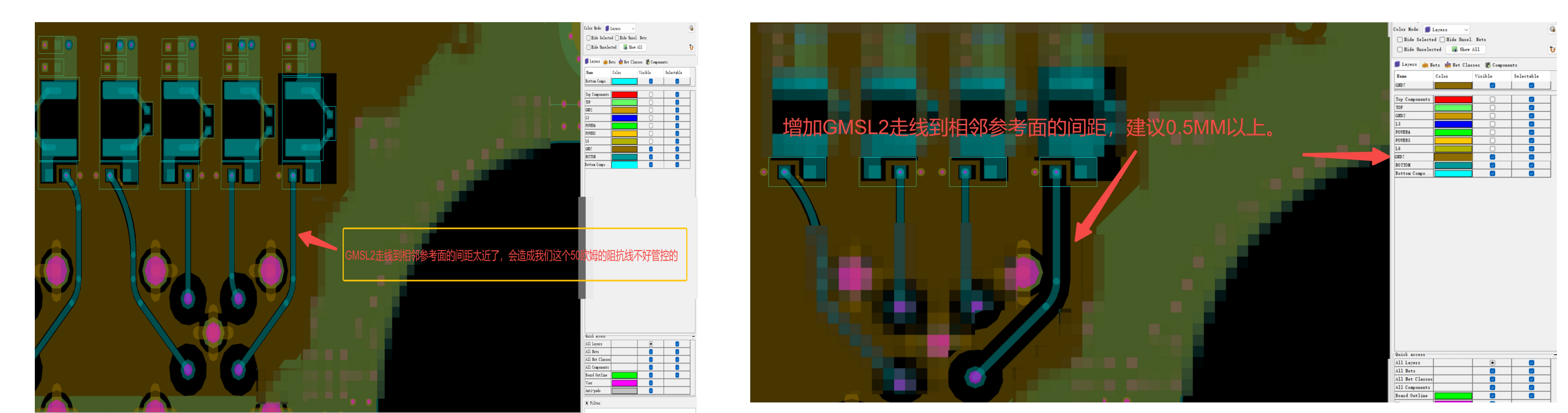

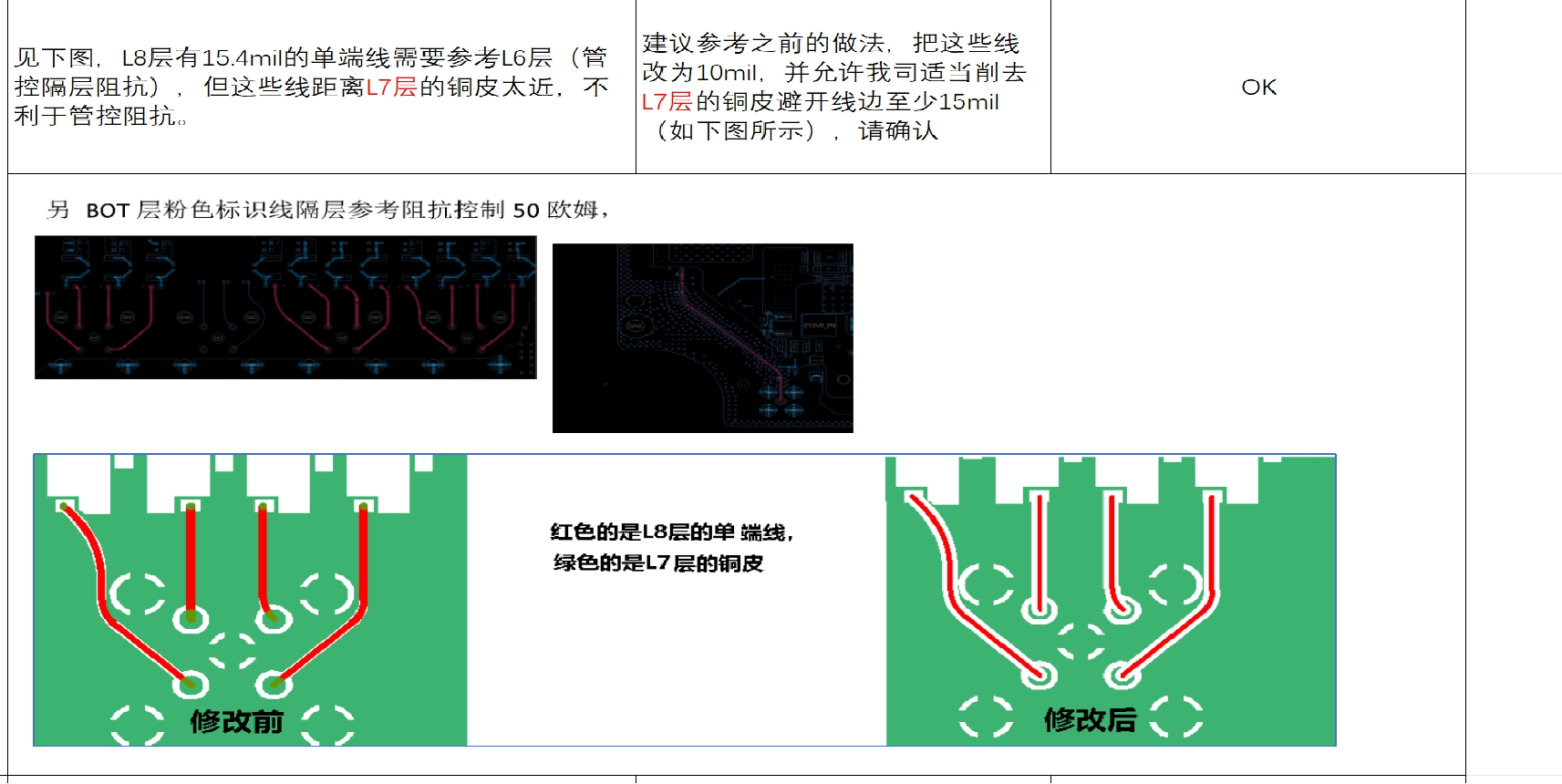

PCB修改的比对结果显示:左边的是之前的初始版本,右边的是优化后PCB版本。

优化后的RX1_96724F_FAKRA_1--Insertion Loss:结果显示的是PASS ,在低频段的时候是已经满足了GMSL2手册的要求的。

分析原因:高频段RL余量不是很多,可能是由于我们单板POC电路上的二级电感部分PCB走线设计上阻抗没有优化好造成的。

PCB修改的比对结果显示:左边的是之前的初始版本,右边的是优化后PCB版本。

优化后的RX1_96724F_FAKRA_1--Return Loss:结果显示,板级设计裕量充足,PASS

单板设计的时候尽量在前期做好优化,不然后期EQ的时候还是需要再去确认一下阻抗的问题。

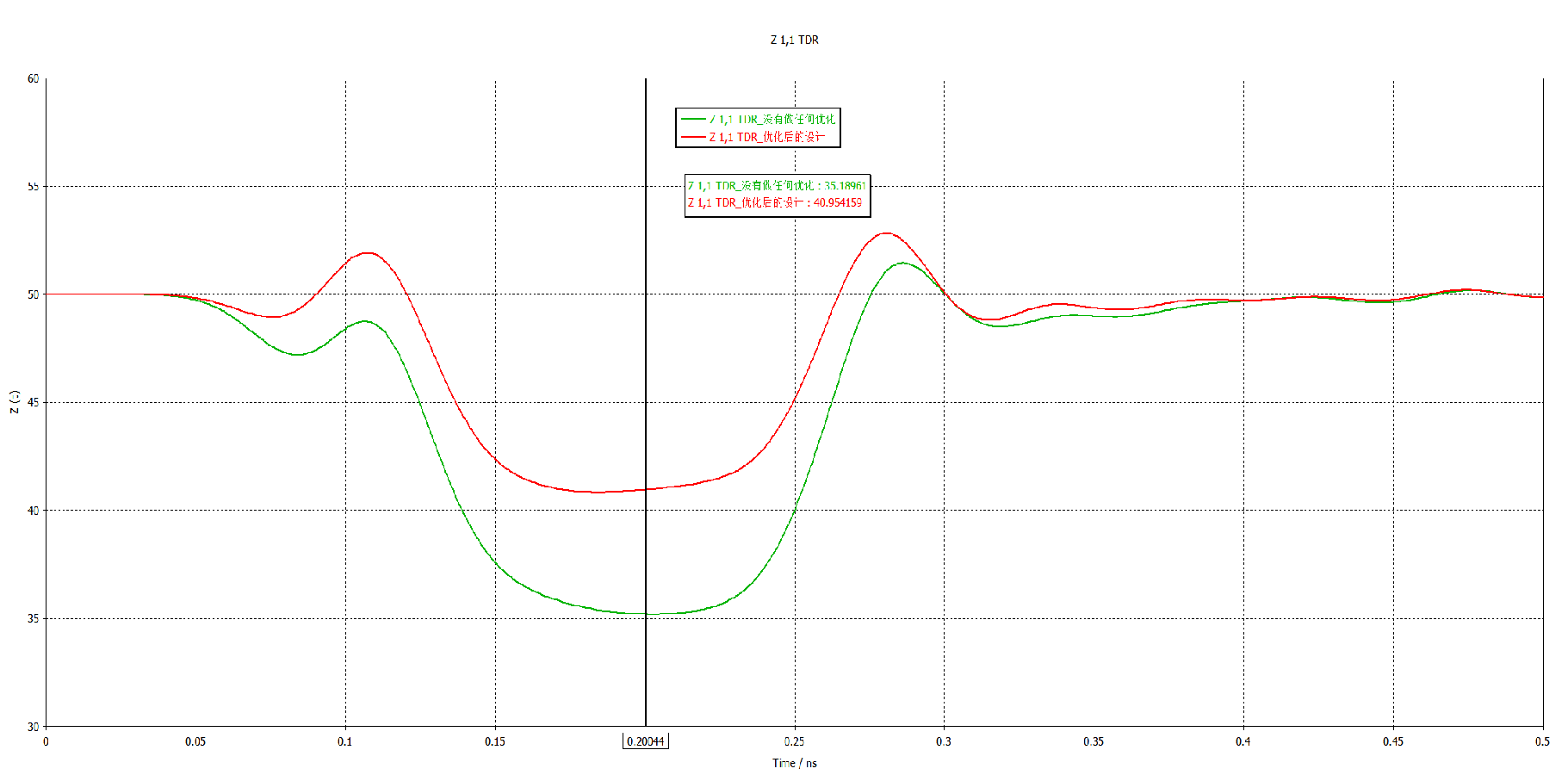

优化后的RX1_96724F_FAKRA_1_TDR曲线:结果显示,阻抗改善大约6欧姆左右。

好了,诸位道友们以上就是本期的所有内容了,我们下期文章不见不散。

--------声明:本文属于小编的原创文章,如需转载请注明来源!

1603

1603

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?