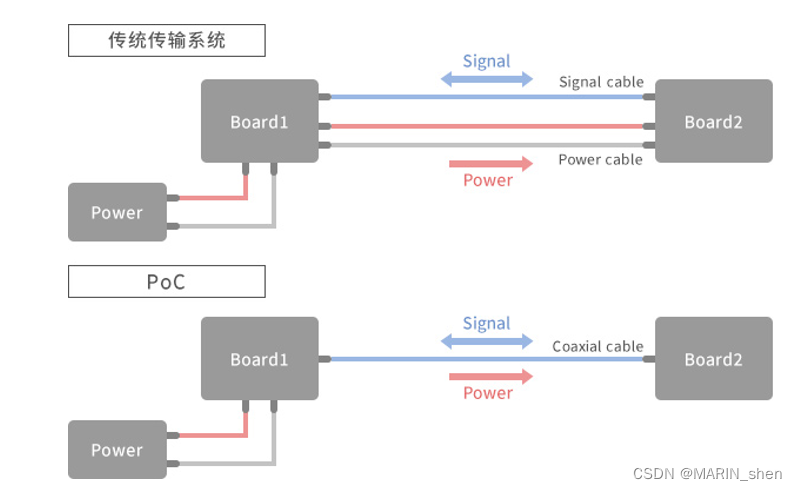

POC(Power Over Coaxia)一种基于同轴线缆传输的视频信号、同轴控制,电源叠加的技术。

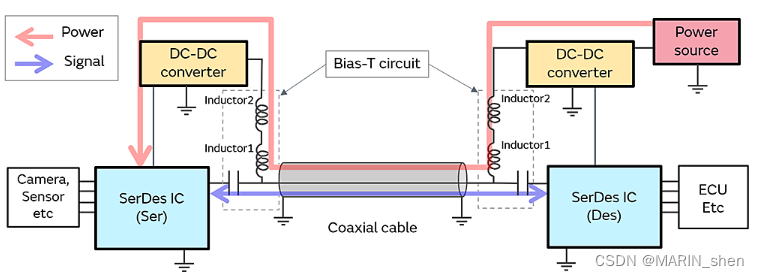

POC电路框图

外部的负载部分,例如相机或者是天线等。 内部的控制器或者是车机。

一,POC的工作原理:

1,直流状态时,电感处于短路状态,电容处于开路状态,因此,接收端的电源能够通过电感注入到信号传输系统中,并在另一端通过电感拾取,然后通 过电感为本地电路供电。

2,而对于高频信号,电容器是低阻抗的,而电感器是高阻抗的,因此,高速信号能够正常进行传输。

3,同时,电感器和电缆的直流电阻应保持足够低,以允许有效的功率分配。

二,POC电路的设计目标:

交流状态下:

1,通过电感器提供足够高的阻抗,以隔离此电路对高速信号的影响。

2, 同时,该高阻抗需要保持足够高的带宽,这样才能支持信号的工作频率(需要包含反向和前向通道的所有工作情况)。

3,电感器需要有高饱和电流,这样才能支持满负荷直流电流通过系统。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2127

2127

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?