小编我正在网上观看LPL的世界赛EDG对战WBG的比赛,虽然前几天早就知道了结果,但是小编我作为一个LPL老粉丝还是去复盘了一下比赛,想看一下哪些人比赛中出现了问题,足以见得小编我在平时的生活和工作中是一个敢于反思和总结问题的人。

正当我准备开始看比赛的时候,发现手机微信上有个提示的短信,一看是来自我们组的一个硬件同事法国好哥们强哥发来的。他主要意思说我的PCB板子上有两组SPI信号的串联匹配电阻位置放置的有问题,明天上午需要修改一下布局。我是真的会谢谢他啊,这都几点啊,下班时候还给我发这种信息。不过为了中法的国际友情可以继续维持下去,我还是出于礼貌地回复他了,说明天早上到公司了再去改布局吧。

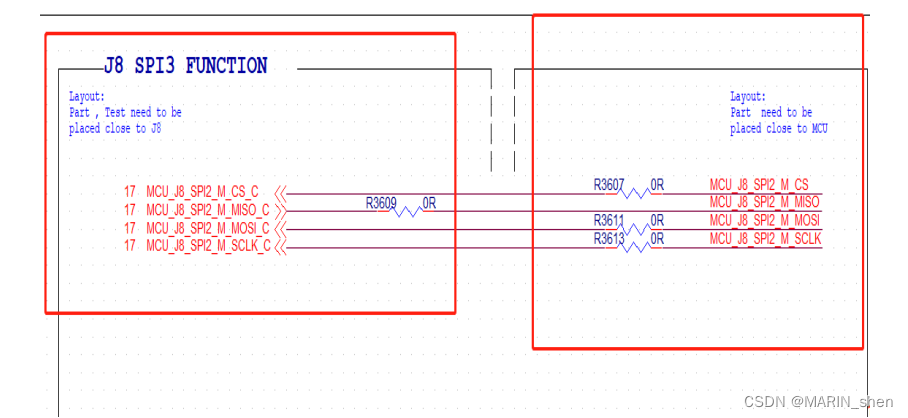

作为一个优秀并且帅气十足颜值赶得上吴彦祖老师的男人,一想到自己设计的板子的布局上居然还有一些问题出现,小编我就看比赛视频看不下去了,立马远程连接我公司的电脑,打开原理图和PCB,通过小编我的仔细检查终于发现了我的问题了,原来我的SPI信号上的MISO信号的串联匹配电阻没有靠近主芯片放置了,而是和SPI其他的三个信号上的串联匹配电阻放置在一起都在MCU芯片这边了。大家做PCB设计的朋友应该都清楚的是在布局的时候串联电阻是需要靠近源端驱动芯片放置的(源端串联越靠近源端越好,末端并联越靠近末端越好),而且电阻的位置不能离芯片太远了,有一个设计经验就是:你串联电阻上的走线长度(信号的延时)要≤信号的上升沿时间1/6,这个也是有仿真数据支撑的,大家感兴趣的可以去CSDN网上自己查阅一下。

探究电阻布局对端接效果的影响 https://blog.csdn.net/edadoc2013/article/details/129285133?ops_request_misc=&request_id=&biz_id=102&utm_term=%E4%B8%B2%E8%81%94%E7%94%B5%E9%98%BB%E9%9D%A0%E8%BF%91%E9%A9%B1%E5%8A%A8%E7%AB%AF&utm_medium=distribute.pc_search_result.none-task-blog-2~all~sobaiduweb~default-3-129285133.142%5Ev92%5EchatsearchT0_1&spm=1018.2226.3001.4187然后我就赶紧快马加鞭的把这个布局修改完了,其实都已经到了布线后期了才发现这个问题属实不应该的,小编我应该立刻自罚三杯酒的。

https://blog.csdn.net/edadoc2013/article/details/129285133?ops_request_misc=&request_id=&biz_id=102&utm_term=%E4%B8%B2%E8%81%94%E7%94%B5%E9%98%BB%E9%9D%A0%E8%BF%91%E9%A9%B1%E5%8A%A8%E7%AB%AF&utm_medium=distribute.pc_search_result.none-task-blog-2~all~sobaiduweb~default-3-129285133.142%5Ev92%5EchatsearchT0_1&spm=1018.2226.3001.4187然后我就赶紧快马加鞭的把这个布局修改完了,其实都已经到了布线后期了才发现这个问题属实不应该的,小编我应该立刻自罚三杯酒的。

当然了这只是一句玩笑话了,既然板子的布局出了问题我们还是需要认真的复盘一下的,虽然LPL的世界赛名额比赛小编我不能去看视频复盘了,这个布局的案例还是需要小编我认真反思复盘一下的,其实出现这个问题主要在与小编我在布局的时候没有认真去看原理图的注释的,其实我那个硬件法国同事在原理图上很贴心的给我备注了布局的要求,但是我还是凭借着自己的所谓的经验去布局了,结果差点就出问题了。

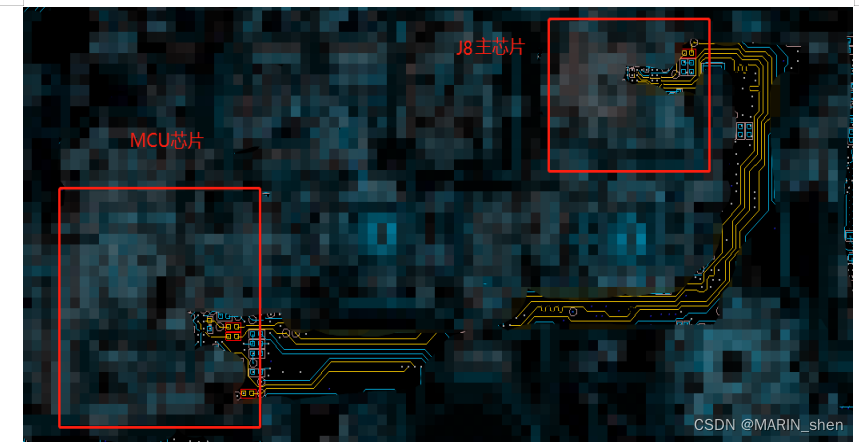

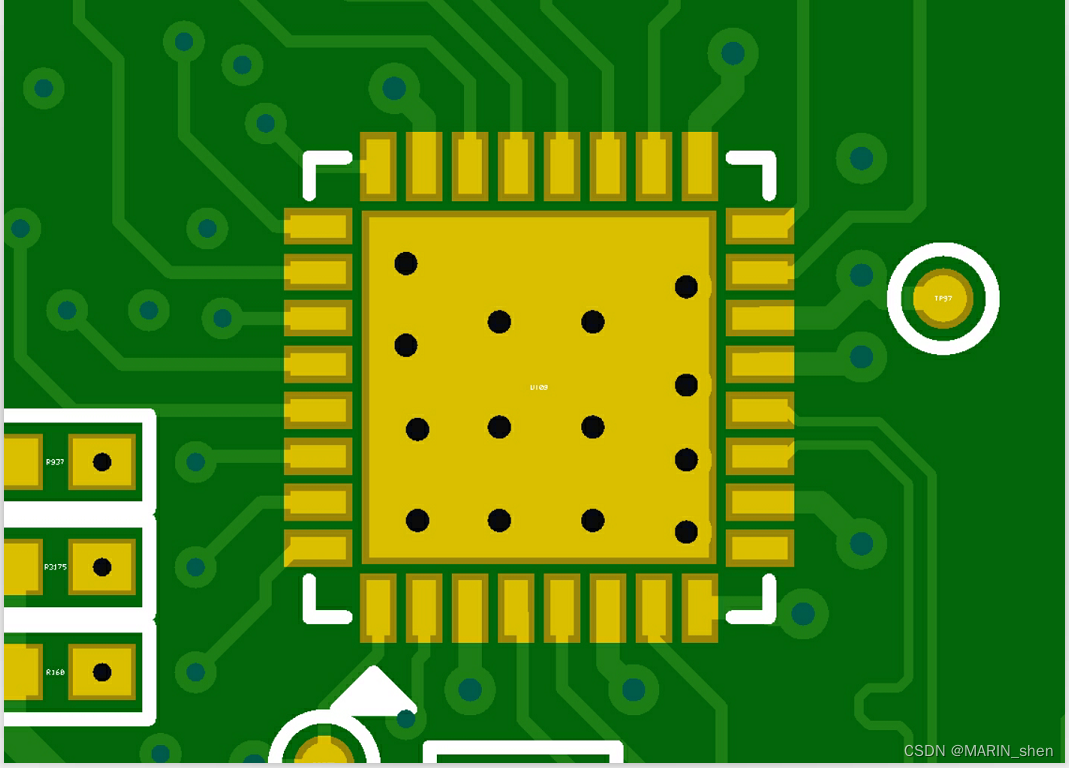

(修改后的布局)

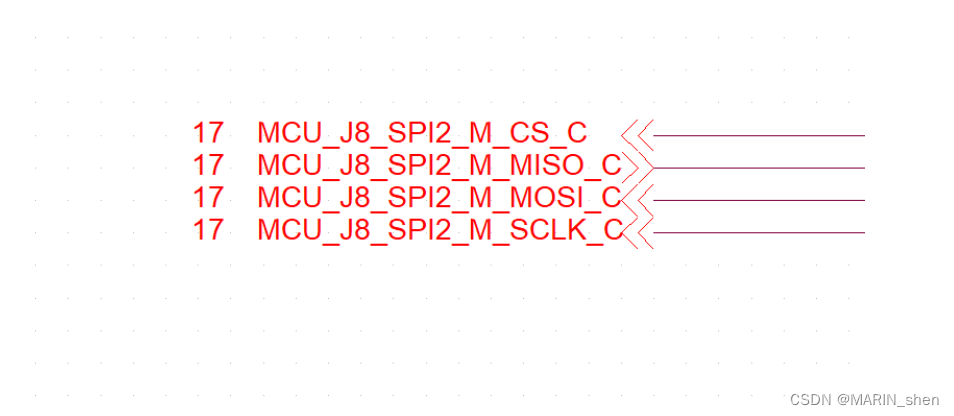

其实大家需要注意一点就是SPI_BUS的线有四个信号,如下图所示:

其中MCU_J8_SPI2_M_MISO_C这个信号线比较特殊一些,其实这个MSIO信号的英文就是master-slave-output需要靠近接收端放置的,换句话说相当于MCU是驱动端(master_device),J8那边是接收端(slave device),所以说MCU_J8_SPI2_M_MISO_C串联的短接电阻是需要靠近接收端J8那边放置的,其他的三个电阻是需要靠近驱动端放置的。当然了也有J8芯片作为master_device,MCU那边的作为slave device,这个时候MCU_J8_SPI2_M_MISO_C串联的短接电阻布局的时候就需要靠近MCU这边放置了。

还有就是关于MCU芯片和主芯片到底谁是SPI-function -slave device或者是SPI-function -master device?这个建议问下你的硬件同事,一般他们都会在原理图上通过网络名字来给你标注出来的,如上图所示的,MCU_J8_SPI0_M_CS等信号就表明MCU在网络名字在J8的前面,MCU芯片就是master device,J8芯片是slave device了。

当然了不是所有的硬件都会给你写备注的,有的时候你遇到了稍微有一些些懒点的硬件(不是吐槽硬件朋友们都很懒啊,你们硬件的大佬们也别开喷小编我,小编很害怕被网暴的。可能每硬件不写备注的也是由于个人的习惯导致的,他们或许认为这个点还需要我硬件来写吗?那些搞PCB设计的人这个都不知道吗?回家种地得了,其实他说的也不是全错吧,但是我很认同我们电子硬件组老大的一句话就是:我们硬件做原理图设计不仅仅是要按照原理图设计规范要求去画图,还要提高原理图的可阅读性。),加上你的设计经验不足的话,你看到原理图上SPI的BUS信号四个串联电阻都画在MCU这边了,你布局的时候也就全部摆在这边了。到了后面布局评审检查的时候还是需要修改这个布局的,所以说这点足以证明一个优秀的硬件同事对于一个Layout工程师的帮忙是有多大。硬件同事和Layout工程师都是一个硬件团队不可或缺的人,大家要是都能够有效沟通,避免反复的工作量和修改,这样对整个项目的质量和交期都是有很好的提升的。俗话说的好独木难成林嘛,换一句话说就是:大家好才是真的好嘛(小编很喜欢的一个女明星代言的广告语),每个人都变的强大了,小组也就越来越好了,做出的项目质量就越高了。好了,我们下期文章不见不散。

1092

1092

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?