1 概念

1、建立时间与保持时间

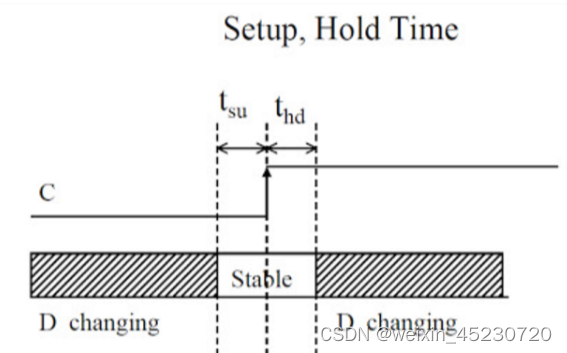

触发器在时钟上升沿来临时对数据进行采样,产生对应的输出。但是实际器件无法瞬时完成数据采样这一过程,需要数据在时钟沿前后均稳定一定时间,即引入了(触发器的)建立时间与保持时间这一概念。

建立时间Tsu:时钟有效沿到来之前数据必须保持稳定的最小时间;

保持时间Th:时钟有效沿到来之后数据必须保持稳定的最小时间;

2、恢复时间与去除时间

恢复时间(Recovery time):与同步电路中的建立时间类似,是指异步控制信号(如寄存器的异步清除和置位控制信号)在“下个时钟沿”来临之前变无效的最小时间长度。这个时间的意义是,异步控制信号在时钟上升沿来临Trecovery时间就要保持稳定,如果保证不了这个最小恢复时间,也就是说“下个时钟沿”来临时,这个异步控制信号不能保证正常执行。

去除时间(Removal time):与同步电路中的保持时间类似,是指异步控制信号(如寄存器的异步清除和置位控制信号)在“有效时钟沿”之后变无效的最小时间长度。这个时间的意义是,异步控制信号在时钟上升沿后仍需保持Tremoval的稳定时间,如果保证不了这个去除时间,也就是说这个异步控制信号的解除与“有效时钟沿”离得太近,那么依旧不能保证这一异步控制信号能正常执行。

3、亚稳态

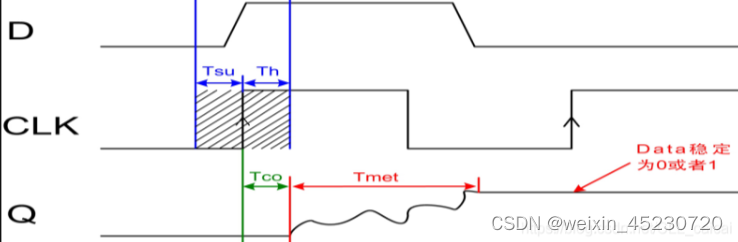

亚稳态是 指触发器无法在某个规定的时间段内到达一个可以确认的状态。(触发器建立时间或保持时间不满足,导致Q端输出电平为介于高电平和低电平之间的第三稳定点。)即:如果触发器的输入电压采样时间过短,则触发器需要花很长时间来实现输出逻辑达到标准电平,在这段时间里输出端在高低电平之间处于振荡状态,而不是等于理想输出值。也就是说,电路处于中间态的时间变长,使得电路“反应”迟钝,这就是“亚稳态”。(例如输入信号在时钟有效沿的建立时间和保持时间之间改变了,导致不满足触发器的建立时间或保持时间,导致输出有一段时间的不稳定态,就是亚态。)

后果:

1、亚稳态中间态时间变长:亚稳态是触发器的一个固有特性,正常采样也会有一个亚稳态时间。当建立时间和保持时间满足时,触发器也会经历采样---亚稳态---随后稳定输出。而出现亚稳态问题时,亚稳态(中间态)时间变长

2、亚稳态的输出不一定正确:正常工作时,触发器经历较短的亚稳态时间,随后会正确输出;而出现亚稳态问题时,触发器经历较长的亚稳态时间,最终输出稳定但无法保证正确(是稳定的标准电平信号,但难以保证是输入对应输出);

物理意义:

数字电路中,对于电平小于电压阈值 VL的称为0,大于电压阈值VL 称之为1,而电平位于电压阈值之间时(无法确定电压为0还是1)叫做系统的亚稳态。

工程意义:

亚稳态是指触发器无法在某个规定的时间内达到可以确认的状态。一旦触发器进入亚稳态,则既无法预测触发器的输出电平,也无法预测什么时候稳定在某个确认的电平上。(稳定所需时间不定、输出结果不定)

2 亚稳态产生的原因

2.1 同步时钟

2.2 异步时钟

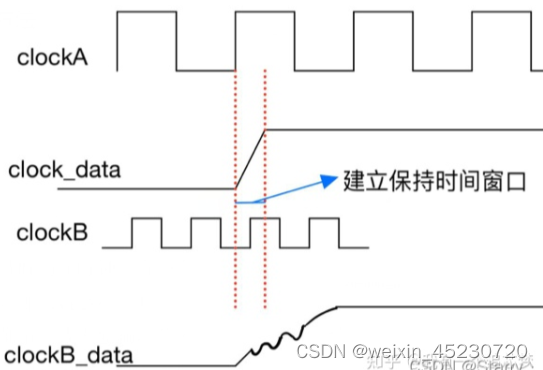

2.2.1 跨时钟域

就是两个触发器用的时钟频率不相同,那么UFF1/CK采样的时候采样或驱动时UFF1/D端不稳定

3 亚稳态的解决办法

如图所示,跨时钟域这么多情形,都可以追溯至电平信号打两拍解决亚稳态问题。例如当单bit跨时钟域不满足“3个沿”条件,即可以稳定采样时,就需要找到一个满足“3个沿”条件的电平信号,因此先使用异或展宽构造一个电平信号。

多bit跨时钟域时若满足“3个沿”,可以稳定采样时,使用Grey码将多bit跨时钟域 转化为单bit电平跨时钟域,之后就可以电平同步了。也可以使用valid作为多bit的等效电平信号,之后直接电平同步即可。

3.1 同步时钟

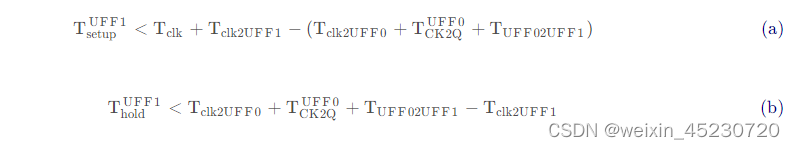

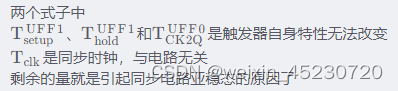

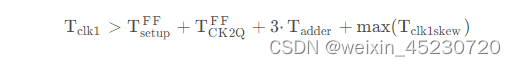

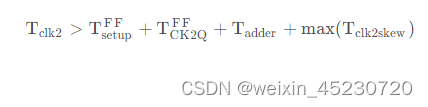

从STA公式( a ) (a)(a)和( b ) (b)(b)就可以看出端倪了,重写如下

3.1.1组合逻辑

从上述公式可以看出,组合逻辑会影响建立时间和保持时间的满足。

不仅如此,在满足建立时间和保持时间的前提下,组合逻辑与时钟频率Tclk 有关联。

真正对右式起关键作用之一的就是组合逻辑T U F F i 2 U F F j

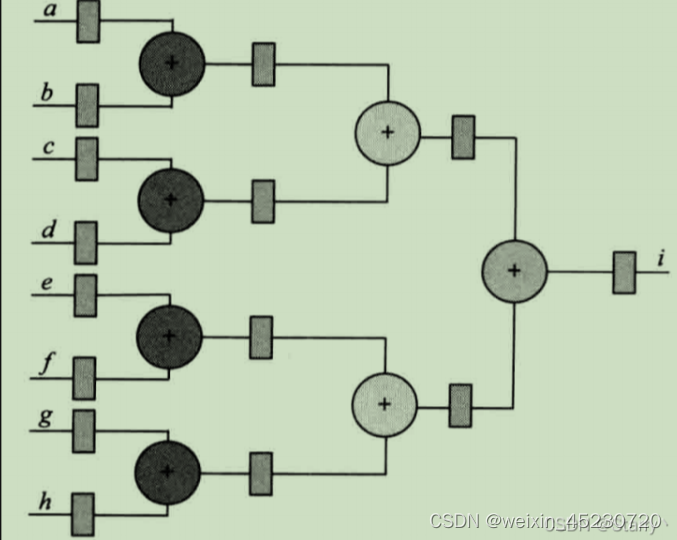

3.1.1.2 流水线设计

也是pipeline,意思非常简单,就是在冗长的组合逻辑中加入多级触发器,这样每个T clk

两个触发器之间走过的组合逻辑路径就会减少,就可以减小Tclk提高系统工作频率。

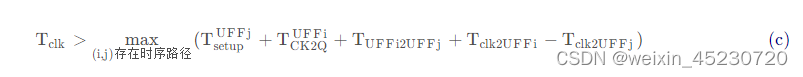

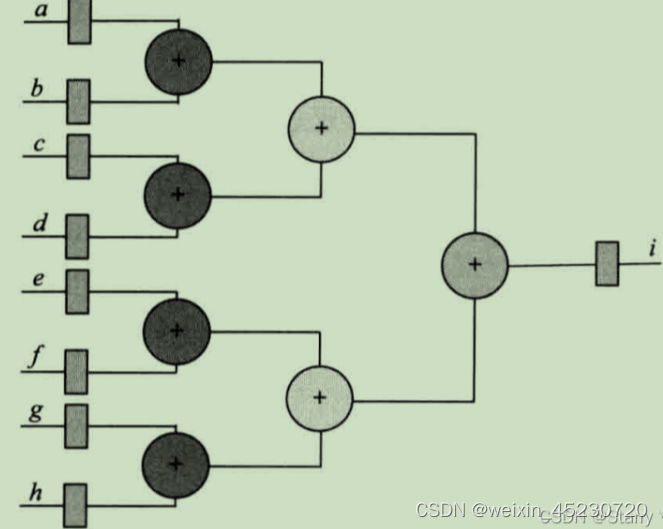

举加法器的例子,我们分别代入(c)式计算

不使用流水时:

使用流水线:

分析一下流水设计带来的变化

● 时钟频率 增加

从公式中可以看出,是用流水后加法器减少了。因为各触发器离得更近了,时钟偏斜也有所减缓,因此系统工作频率可提高。

● 吞吐率 增加

流水线引入后也是每个时钟周期输出一个结果,但是由于时钟频率的增加,使得吞吐率也增加

● 延迟 增加

此处的延迟是指一个数据从输入到输出的总时间

引入流水之前,延迟为T c l k 1 + T C K 2 Q F F ,引入流水之后变成3 T c l k 2 + T C K 2 Q F F 后者更大

● 功耗和面积 增加

毕竟触发器多了嘛,功耗、布局布线都会增加压力

介绍流水线的相关概念

以CPU取指令3ns、分析4ns、执行1ns为例

● 流水线周期: 执行最长操作所花费的时间,也是流水过程中每输出1个结果花费的时间,即4ns

● 操作时间: 只执行1次全部操作花费的时间,即3+4+1=8ns

● n个数据流水线时间: 执行1次流水共执行n次操作花费的时间,公式 操作时间 + (n-1)×流水线周期

● 吞吐率: 输出结果数量 / 流水线时间。n个数据流水线吞吐率为 n / [操作时间 + (n-1)×流水线周期]

● 最大吞吐率: 流水过程中,单位时间内输出的结果数量,为1 / 流水线周期

3.1.2. 时钟偏斜(Clock Skew)

看公式就知道时钟偏斜是啥意思了,就是时钟信号到达不同触发器的时间不同

这个东西在同步电路中必然存在

还有个时钟抖动(Clock Jitter)的概念,是指不同时期时钟周期长短不一

3.1.2.1 解决方法:时钟规划

3.2 异步时钟

3.2.1 单比特信号

信号从源时钟域跨到目的时钟域后,需要在目的时钟的“指挥”下进行操作,这一过程可视为用目的时钟对被处理后的信号进行“采集”,既然是采集,则必须满足奈奎斯特采样定理,也就是说目的时钟频率需要至少是源时钟频率的2倍。

在实际应用过程中,不光需要将慢时钟域信号跨到快时钟域,也需要将快时钟域信号跨到慢时钟域,而后者显然是无法满足采样定理的,所以需要进行一些特定处理。

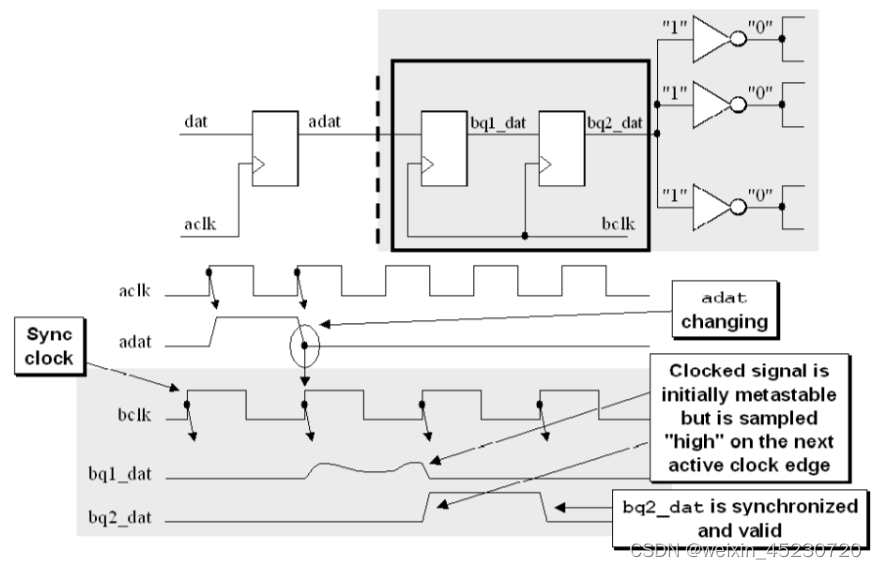

1, 电平信号

如果是电平信号进行CDC,不用考虑时钟快慢,直接用2级或其他级数的同步器就可以,因为总能被采样到。实际上可以将电平型号看做一个频率超级低的脉冲信号

2 ,从慢时钟到快时钟域的脉冲信号

首先需要约定的是,所谓快时钟频率应该至少是慢时钟频率的两倍。若无法满足,则可使用3方法进行处理。在这一前提条件下,是可以保证需要处理的信号能被目的时钟域正确采集到的。

2级同步器进行同步(DFF)是我们最常见的CDC处理方法。这一方法的本质是用触发器将被CDC信号同步到目的时钟域下,但是每一次的同步仍然可能出现亚稳态,随着同步级数的增加,亚稳态出现的概率也会减少。需要注意的是,这一过程并非线性的。实际上,3级同步器以上对亚稳态减小的作用就很小了。通常使用2级或者3级同步器即可将亚稳态发生的概率维持在一个非常小的值。

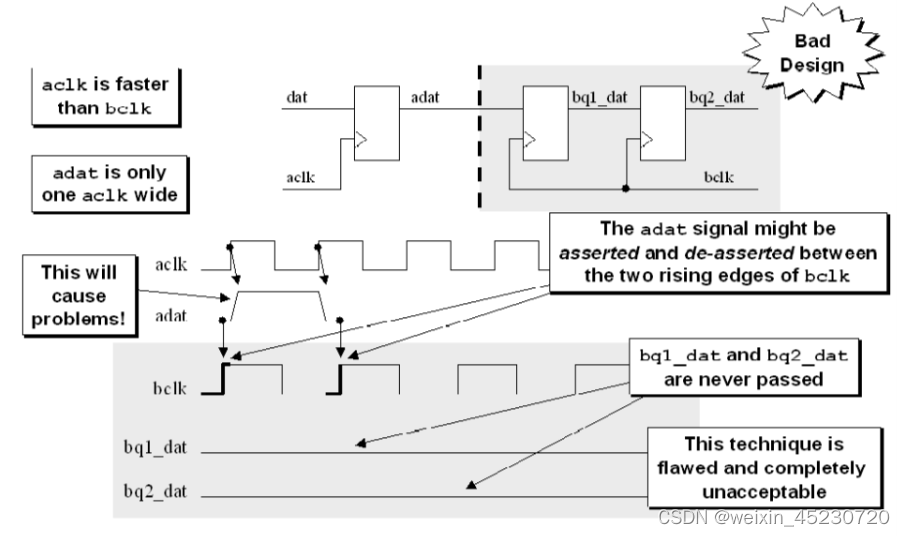

3、从快时钟域到慢时钟域的脉冲信号

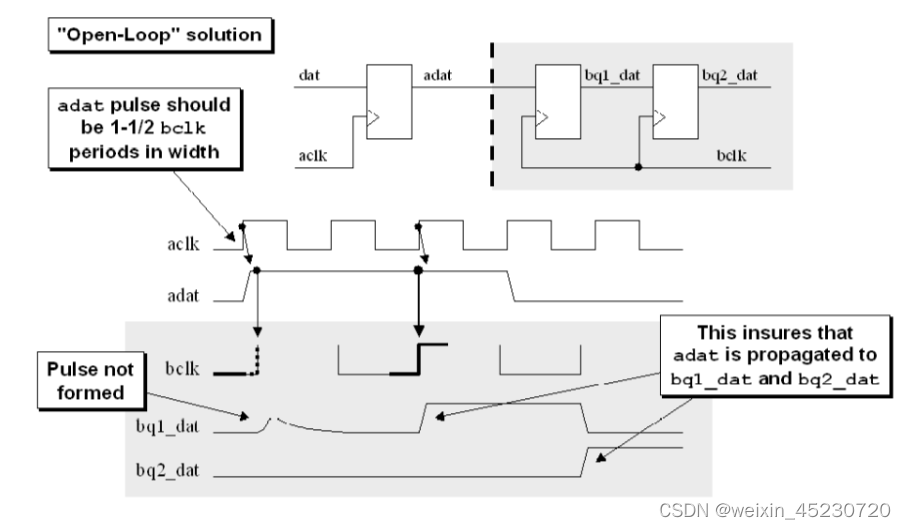

下图中,adat是快时钟域a下的脉冲信号,bclk是目的时钟(慢时钟),很明显,信号adat被同步到目的时钟域后出现了漏采,这是因为adat的频率高于目的时钟。

既然脉冲信号频率高于目的时钟才导致的漏采,那么我将脉冲信号拓宽到一定的程度不就可以保证采集到了吗?这一方法的本质实质上是降频,也就是将问题转换为我们已经能解决的用较快的时钟来采集较慢的时钟。如下图:

将信号adat扩宽为3倍aclk后,脉冲信号成为了一个较慢的信号,而目的时钟成为了一个较快的时钟,这样我们就可以使用2级同步器的方法来对被CDC信号进行同步。

需要注意的是,这一方法具有一定的局限性:

- 若需要同步的两个脉冲信号距离很近,则第一个脉冲信号的扩宽可能会覆盖第二个脉冲信号,从而导致第二个脉冲信号的漏采;

- 脉冲信号的扩宽是以目的时钟为参考的,但是若不知道目的时钟的频率,则该方法可能失效,也就是说该方法不具备普遍性。

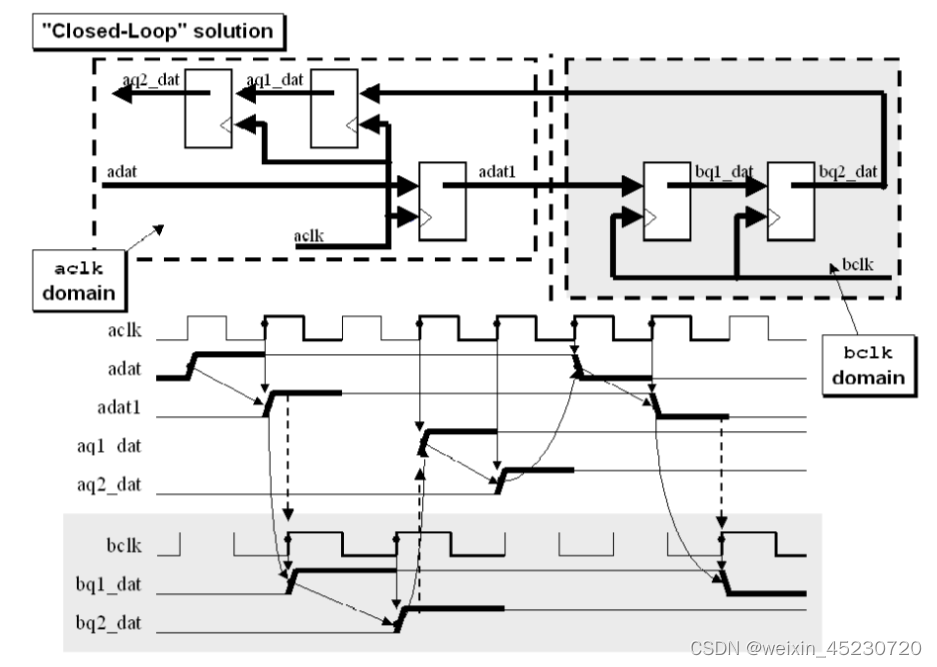

为了探寻一种具备普遍性的方法,我们可以使用握手法来进行CDC。握手法的本质是负反馈,通俗来讲,就是我先将被CDC信号展宽,展宽后将其同步到目的时钟域,在目的时钟域生成指示信号,该指示信号用来指示此时信号已经被目的时钟域接收,然后将指示信号反馈到源时钟域(反馈过程),源时钟域接收到这个反馈信号后将被CDC信号拉低,从而确定了展宽长度,也通过”发送--反馈--操作“这一握手过程完成了一次CDC传输。

上图是典型的握手过程来进行CDC:

源时钟域aclk下的信号adt1信号是要进行CDC的信号;

adt1先是在源时钟域aclk下被展宽,然后通过两级同步器被同步到目的时钟域bclk下,分别为bq1_dat,bq2_dat;

bq2_dat作为指示信号(反馈信号,也可以通过bq1_dat和bq2_dat来生成新的指示信号)又被反馈到了目的时钟域aclk下,并进行同步,分别为aq1_dat,aq2_dat;

aq2_dat的拉高则说明反馈信号的同步完成,此时可以将adt1拉低(结束展宽过程);

adt1拉低(结束展宽过程)后表示一次CDC操作结束。

3.2.2多比特

1、跨时钟域处理方法的分类

跨时钟域处理方法可以分为两个大类:单Bit信号跨时钟域处理、多Bit信号跨时钟域处理。

分类的原因是多bit信号的传递不光只有亚稳态这一个问题,还可能会因为多个信号之间由于工艺、PCB布局等因素导致的信号传输延时(skew)的存在,从而导致信号被漏采或者错采。

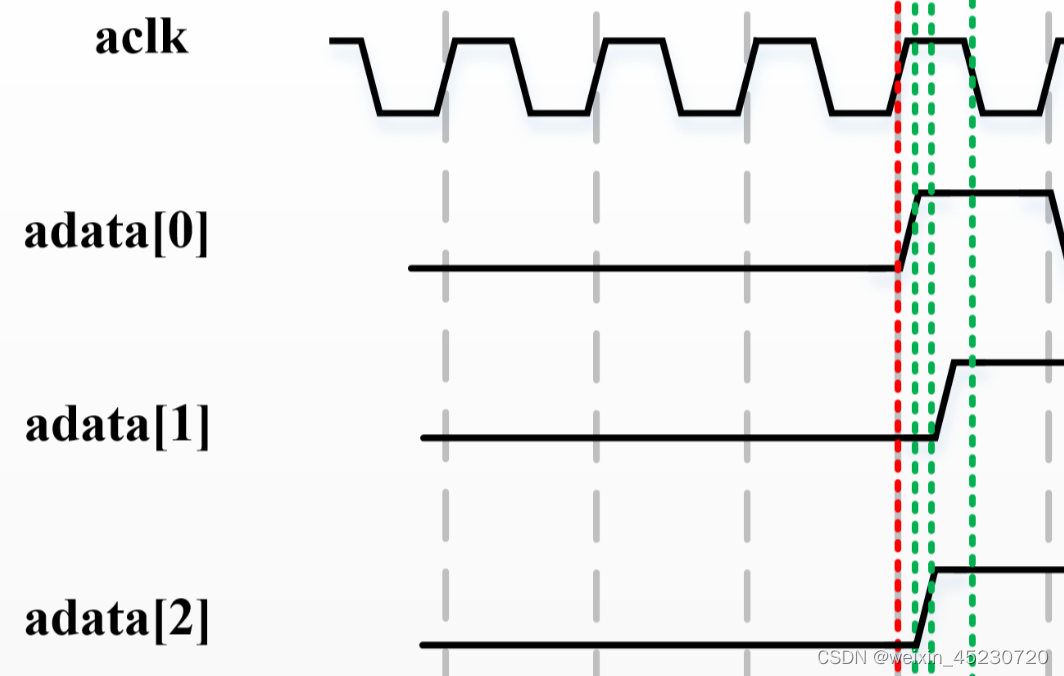

1.1. 时钟偏斜 导致的采样中间值问题

● 时钟偏斜:时钟沿信号到达各触发器CK端的时间不同

这会导致多bit信号的每个触发器值变化不是同时的,有的变得快有的变得慢,如果每个bit都没变完,就被异步时钟采样了,就会出现中间值。

单bit信号电平也好,脉冲也好跨时钟域,采样到了就算有点延迟也没关系。

但是多bit信号要求整个变化过程都是恒定的,中间出现了第三个值就可能对功能产生影响。

红线处adata由000变为111,因为时钟偏斜,该信号每个bit真正开始拉高的时刻不一样。如果异步时钟bclk在不同的时刻采样会对应不同时刻的值,3条绿线分别对应采样到001、101、111。

尽管最终也会采到正确的值,但是中间值的出现会在bclk内存在一拍,思考如何消除这个。

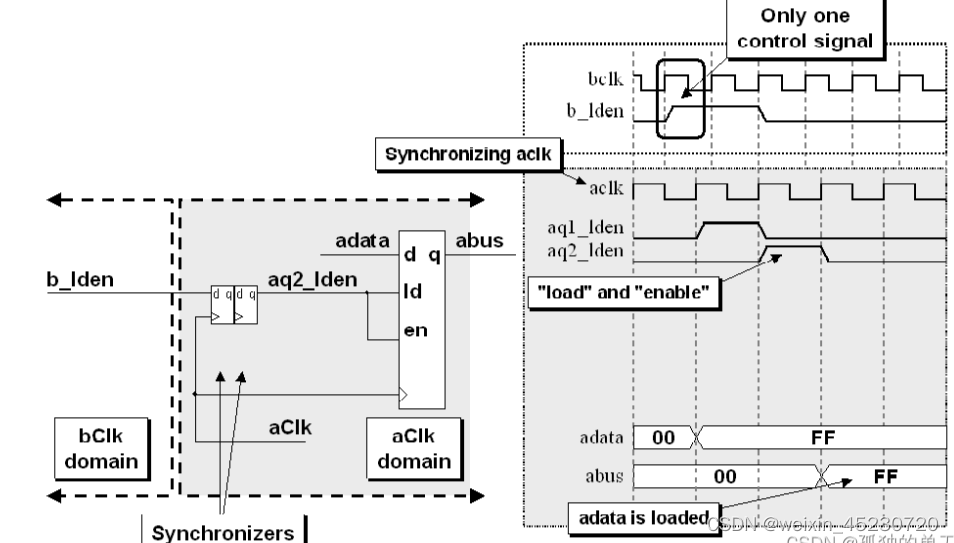

2、合并多个控制信号

在下面的例子中,数据的读取需要载入信号load和使能信号en同时置位,但是这两个信号之间存在一个小偏差(skew),在分别进行单bit的跨时钟域同步时,由于小skew的存在,导致这两个信号在被同步到目的时钟域后有一个时钟周期的偏差,而这个偏差直接导致数据无法被读取。

现在不妨问自己:这两个信号是否都必须传递?实际上不是必须的,应用中我们可以把两个信号合并为一个控制信号,这样就将多bit信号的跨时钟域传递转换成了单bit信号的跨时钟域传递。如下:

3 格雷码

下表给出了3bit自然二进制码、3bit典型格雷码(无特殊说明,典型格雷码即格雷码)与4bit十进制整数的对照:

从格雷码的性质,我们可以发现其虽然是多bit信号的CDC,但是由于每次只有相邻的一位不同,实际上就是1bit信号的CDC,好家伙,又把问题转化成了我们熟悉的单bit信号的跨时钟域问题。

相邻信号只有1bit翻转,且满足"3个沿"条件 可直接 电平同步实现多bit信号的跨时钟域传输。

其实就是将多bit信号跨时钟域问题转化为单bit信号的跨时钟域问题

然后给出一个Gray码与二进制码的转换方式

assign gray = (binary >> 1) ^ binary; //binary code to gray code

integer i;

for(i=0;i<DATA_WIDTH;i=i+1) //gray code to binary code

binary[i] = ^(gray >> i);

但是格雷码的应用也有局限:

格雷码只有相邻的两位之间存在只有1bit的改变,这就意味着数据的改变必须要连续(相邻),也就是说其只适用连续变化的数据,例如计数器,这无疑限制了格雷码的应用场景;

格雷码传递的数据个数必须为2的N次幂----由于最大数与最小数之间也仅一位数不同,即“首尾相连”,因此格雷码又称循环码。若格雷码个数不为2的N次幂,则无法实现“首尾相连”,即最后一位传递到初始位时,就不止变化1bit了,这无疑违背了我们使用格雷码的初衷。

4、握手法

握手法的本质是负反馈,通俗来讲,就是先将被CDC信号展宽,展宽后将其同步到目的时钟域,在目的时钟域生成指示信号,该指示信号用来指示此时信号已经被目的时钟域接收,然后将指示信号反馈到源时钟域(反馈过程),源时钟域接收到这个反馈信号后将被CDC信号拉低,从而确定了展宽长度,也通过”发送--反馈--操作“这一握手过程完成了一次CDC传输。

上图是典型的握手过程来进行CDC:

源时钟域aclk下的信号adt1信号是要进行CDC的信号;

adt1先是在源时钟域aclk下被展宽,然后通过两级同步器被同步到目的时钟域bclk下,分别为bq1_dat,bq2_dat;

bq2_dat作为指示信号(反馈信号,也可以通过bq1_dat和bq2_dat来生成新的指示信号)又被反馈到了目的时钟域aclk下,并进行同步,分别为aq1_dat,aq2_dat;

aq2_dat的拉高则说明反馈信号的同步完成,此时可以将adt1拉低(结束展宽过程);

adt1拉低(结束展宽过程)后表示一次CDC操作结束。

握手法是一种很保险的方法,但是缺点也很明显:需要的时序开销很大。

5、异步FIFO

毫无疑问异步FIFO是多bit信号来跨时钟域处理的最好的、也是最常用的方法。异步FIFO通过先进新出的缓存机制,将两端数据的读写都控制在各自的时钟域内,时钟域之间通过指针+格雷码形式来指示数据的空、满。

关于异步FIFO可以参考:

异步FIFO的设计_weixin_45230720的博客-CSDN博客

335

335

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?