题目:High Performance 3.3KV 4H-SiC MOSFET with a Floating Island and Hetero Junction Diode

阅读日期:2023.6.24

受到的启发:

The gate-drain charge can be obtained through a plateau region of the gate charge. As the gate-drain charge (QGD) caused by the gate-drain parasitic capacitance increases, the switching time increases [24]. Therefore, the reduction of QGD plays an important role in reducing the switching time and loss.

研究了什么

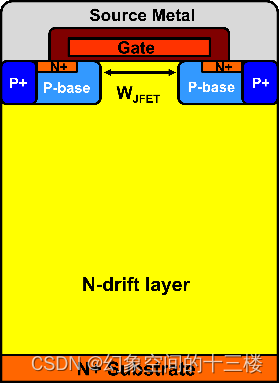

本文研究了一种拟议的3.3 kV 4H-SiC MOSFET结构,该结构具有浮岛和内置异质结二极管(FIHJD-MOSFET),并使用TCAD模拟器对其进行了分析。该研究旨在通过电荷平衡改善器件的静态性能,并保护P+多晶硅区域免受高电场的影响。内置的异质结二极管还改善了反向恢复电荷和开关损耗。研究发现,与传统的扩散MOSFET(C-DMOSFET)相比,FIHJD-MOSFET的B-FOM提高了67.4%,反向恢复电荷和总开关损耗分别提高了72.7%和66.4%。

文章创新点

这篇文章的创新点是:

-提出一种带有浮岛和内置异质结二极管(FIHJD-MOSFET)的 3.3 kV 4H-SiC MOSFET 结构。 -使用 TCAD 模拟器分析建议的结构。

-通过电荷平衡和保护 P+ 多晶硅区域免受高电场的影响,改善器件的静态性能。

-通过内置异质结二极管改善反向恢复电荷和开关损耗。

-与传统的扩散 MOSFET (C-DMOSFET) 相比,B-FOM、反向恢复电荷和总开关损耗方面取得了显著改善。

研究方法

使用TCAD仿真器分析了拟议的具有浮岛和内置异质结二极管(FIHJD-MOSFET)的3.3 kV 4H-SiC MOSFET结构。通过仿真评估了该器件的静态性能、体二极管和动态特性。

得出的结论:

文章的结论是,拟议的带有浮岛和内置异质结二极管(FIHJD-MOSFET)的3.3 kV 4H-SiC MOSFET结构可能是构建3.3 kV功率模块系统的非常有吸引力的器件之一。与传统的扩散MOSFET(C-DMOSFET)相比,FIHJD-MOSFET显著改善了B-FOM、反向恢复电荷和总开关损耗,这要归功于漂移区域和浮岛的电荷平衡以及内置的异质结二极管。仿真结果表明,即使在高电压下,FIHJD-MOSFET 也能稳定运行,浮岛可有效保护器件的多晶硅区域免受高电场的影响。

478

478

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?