一、DDR基本介绍

DDR(Double Data Rate) 是一种 动态随机存取存储器(DRAM) 技术,全称为 双倍数据速率同步动态随机存储器(Double Data Rate Synchronous Dynamic Random-Access Memory)。它的核心特点是 在每个时钟周期的上升沿和下降沿都传输数据,从而实现比传统 SDRAM(单数据速率)更高的带宽。

DDR 的核心原理

* 双倍数据速率:

在时钟信号的 上升沿 和 下降沿 均传输数据,因此实际数据传输速率是时钟频率的 2 倍。

公式:

有效数据传输率=2×时钟频率×数据宽度

例如:DDR4-3200 的时钟频率为 1600 MHz,但数据传输速率为 3200 MT/s(百万次传输/秒)。

* 同步设计:

与 CPU 或内存控制器同步工作,通过差分时钟信号(CK/CK#)确保时序一致性。

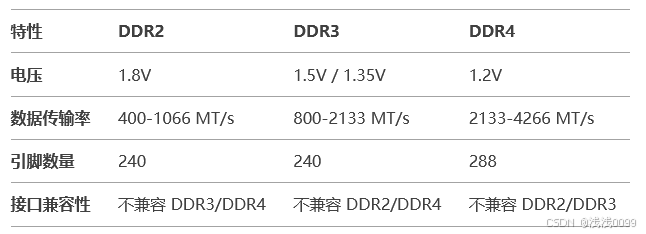

1. 各DDR基本参数对不:

注:

DDR3 中的 1.35V,一般会写成 DDR3L

DDR2、DDR3、DDR4 不能兼容

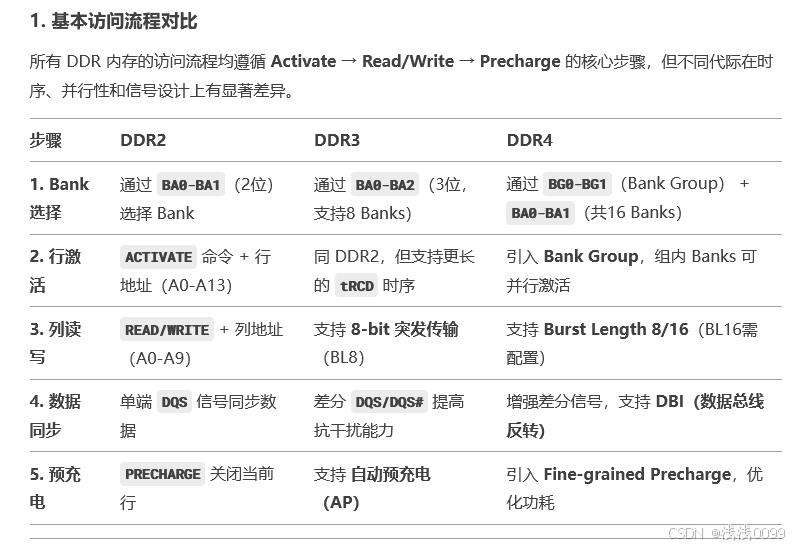

2. 常规DDR数据写入或读取整体流程:

注:Bank行 与 Bank列 共用一套地址,通过 RAS (行地址选通) 和 CAS (列地址选通) 来进行选择。

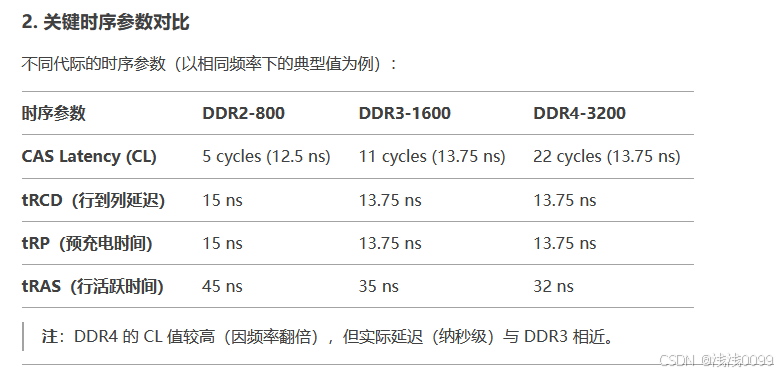

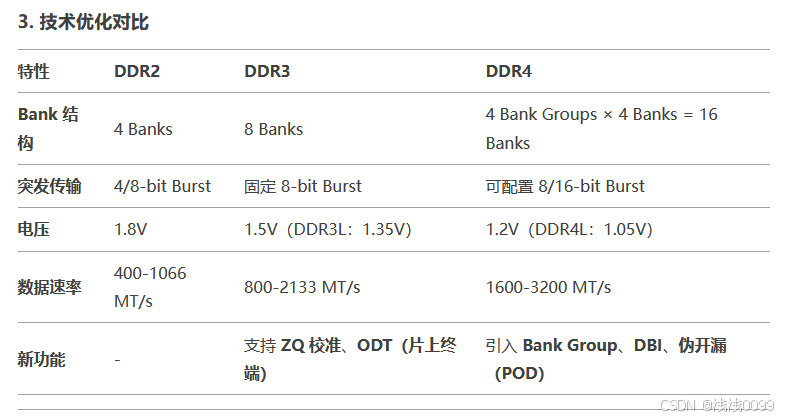

二、各DDR详细对比

注:

tRCD为行到列延迟的时间。

8-bit 突发传输(BL8) 是读取/写入 连续8列的数据,BL16同理。优势:减少列地址切换开销,提高带宽利用率。

4. 选项建议

谢谢观看

END

1989

1989

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?