一、SPI定义

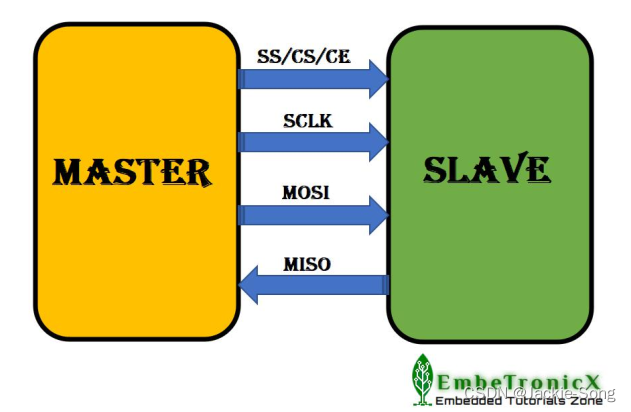

SPI(serial peripheral interface)是一种同步串行通信协议, 由一个主设备和一个或多个从

设备组成, 主设备启动与从设备的同步通信, 从而完成数据的交换。 SPI 是一种高速全双工

同步通信总线, 标准的 SPI 仅仅使用 4 个引脚, 主要应用在 EEPROM, Flash,实时时钟(RTC),

数模转换器(ADC),数字信号处理器(DSP)以及数字信号解码器之间。

SPI就是串行外围设备接口,它是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,这四根线的定义分别是:

MISO:(master input slave output)主设备数据输入,从设备数据输出;

MOSI:(master output slave input)主设备数据输出,从设备数据输入;

SCLK:(时钟是master给的)时钟信号,由主设备产生;

CS :从设备片选信号,由主设备控制。

二、SPI的四种模式

通过CPOL(时钟极性)和CPHA(时钟相位)来控制我们主设备的通信模式。

时钟极性(CPOL)定义了时钟空闲状态电平:

CPOL=0,表示当SCLK=0时处于空闲态,所以有效状态就是SCLK处于高电平时

CPOL=1,表示当SCLK=1时处于空闲态,所以有效状态就是SCLK处于低电平时

时钟相位(CPHA)定义数据的采集时间。

CPHA=0,在时钟的第一个跳变沿(上升沿或下降沿)进行数据采样。,在第2个边沿发送数据

CPHA=1,在时钟的第二个跳变沿(上升沿或下降沿)进行数据采样。,在第1个边沿发送数据

工作模式0:CPOL=0,CPHA=0,当空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在上升沿(准备数据),(发送数据)数据发送是在下降沿。

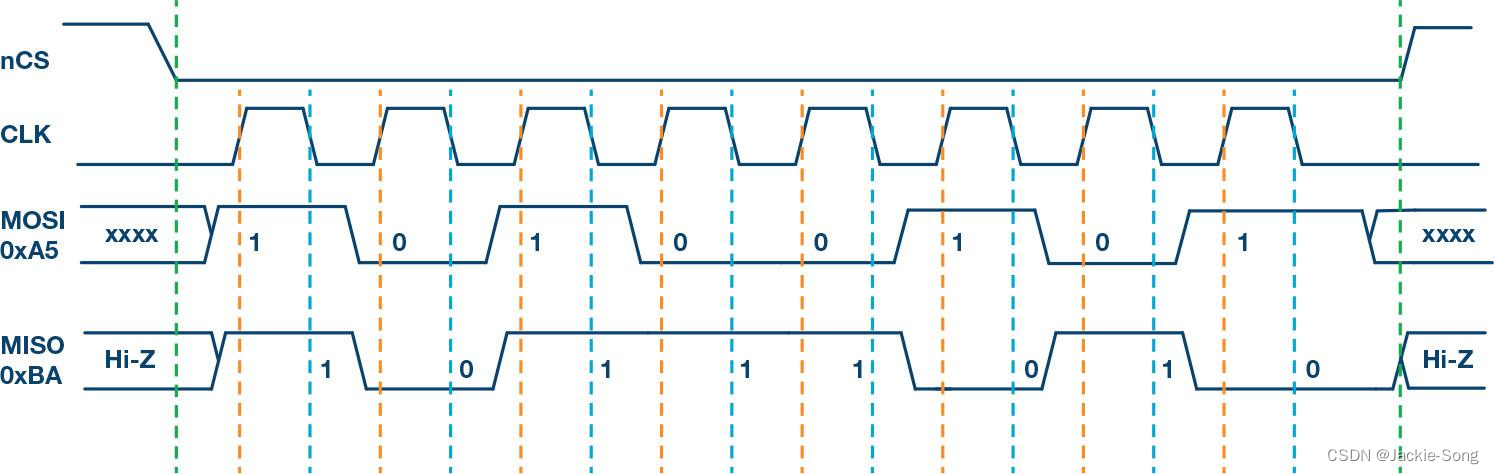

模式0图例:

图中,黄色为数据采样边沿,蓝色为数据发送边沿。当为空闲状态时,SCLK为低,CS片选信号为高。

三、SPI master设计

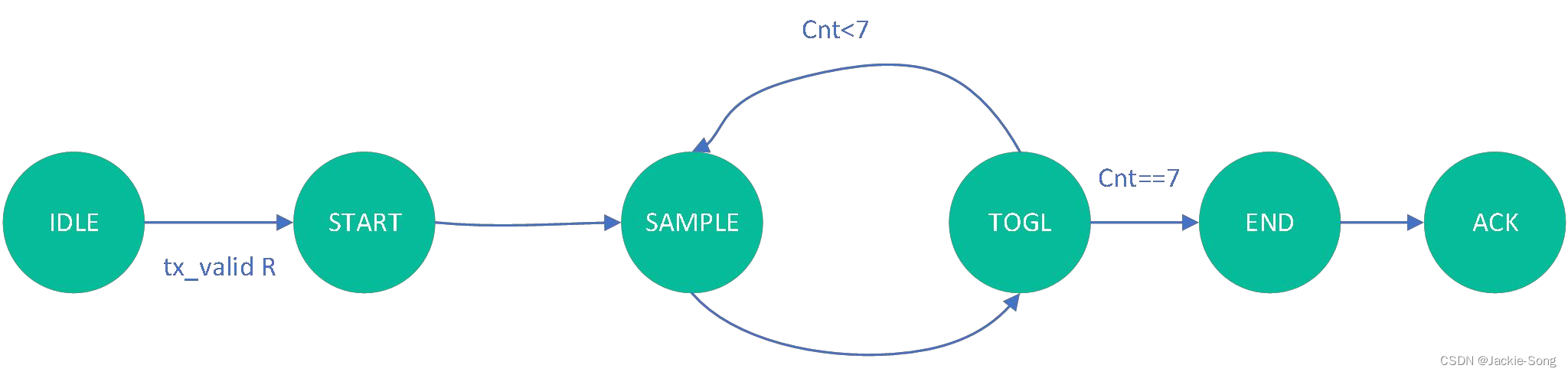

在进行SPI的代码设计时,使用状态机完成

1、发送一个字节

- SAMPLE状态:

if (current_state==SAMPLE) begin

rx_data_reg<={rx_data_reg[6:0],miso};

endSAMPLE状态下,将input端的miso数据送入寄存器当中,即为收数据过程

- TOGL状态:

if(current_state==TOGL) begin

mosi_temp<=tx_data_reg[tx_index];

endTOGL状态下,将寄存器中的数据进行发送,即发数据的过程

由此可完成一次数据的收发过程,在下面状态机下设置cnt的目的是完成一次8bit数据的收发

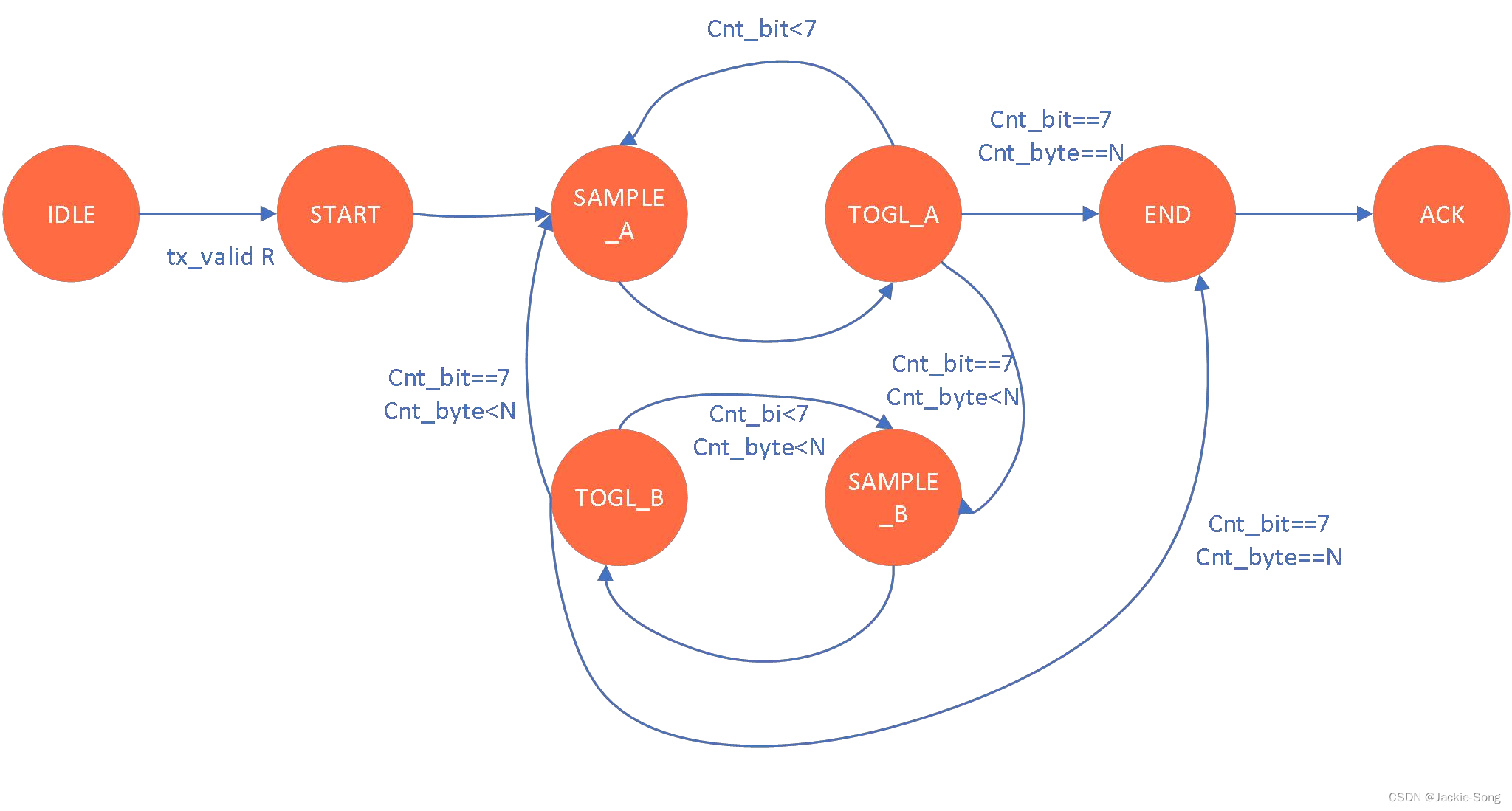

2、发送多个字节(乒乓操作)

原理同发送一个字节

7万+

7万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?