相关阅读

静态时序分析![]() https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

生成时钟

上一节中,我们讨论了理想时钟和传播时钟的创建和使用,本节将讨论生成时钟及其与理想时钟和传播时钟的关系。

图1所示的是一个简单的例子,两个级联的D触发器使用一个分频时钟作为它们的时钟。

图1 简单的例子

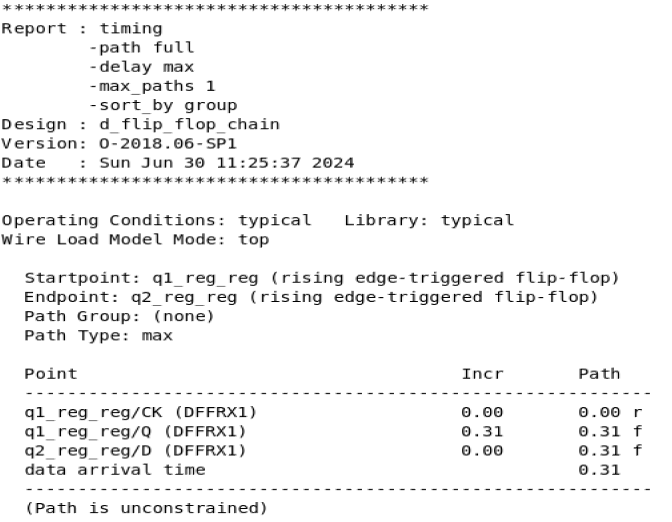

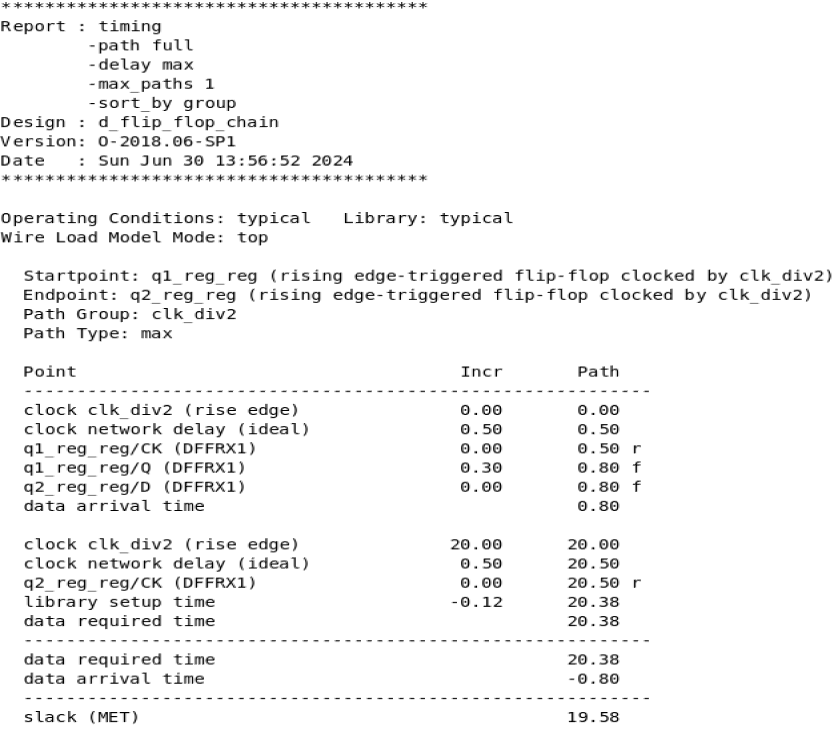

下面使用create_clock命令在输入端口clk处创建一个理想时钟,图2是此时的建立时间时序报告。

create_clock -period 10 [get_clock clk]

图2 建立时间时序报告

可以看出此时显示时序路径尚未约束,这是因为输入端口clk处的时钟,无法从一个分频D触发器的时钟端,传播至其输出端。这种情况下,需要在分频D触发器的输出端定义一个生成时钟(当然直接定义一个时钟也可以,但这是有缺陷的)。

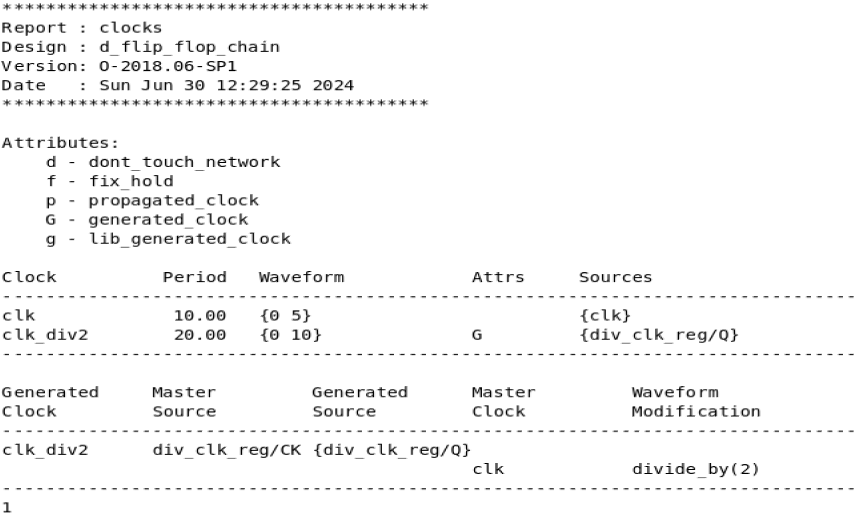

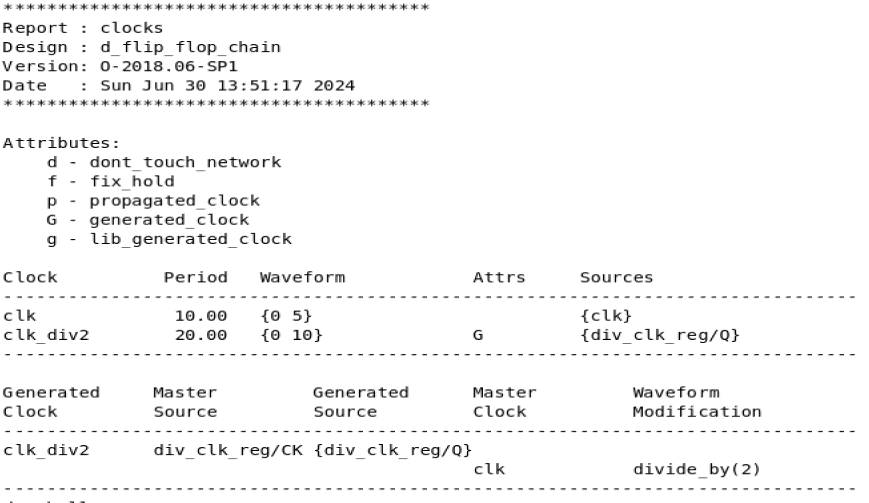

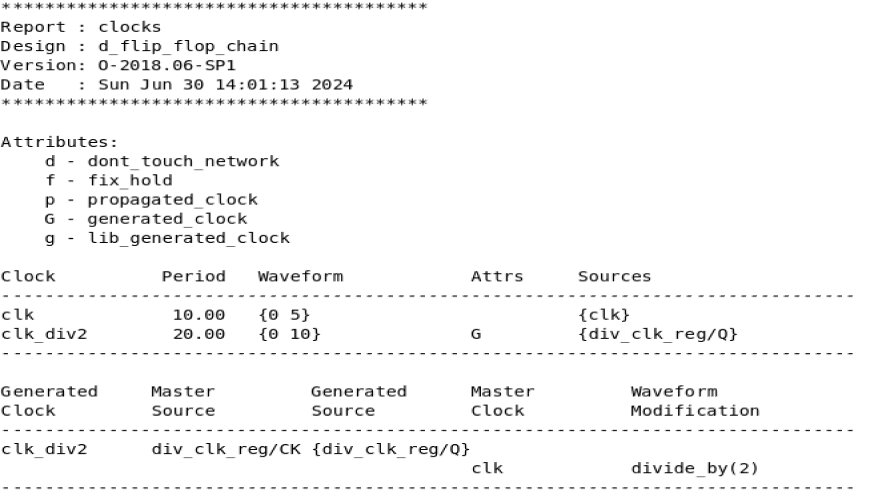

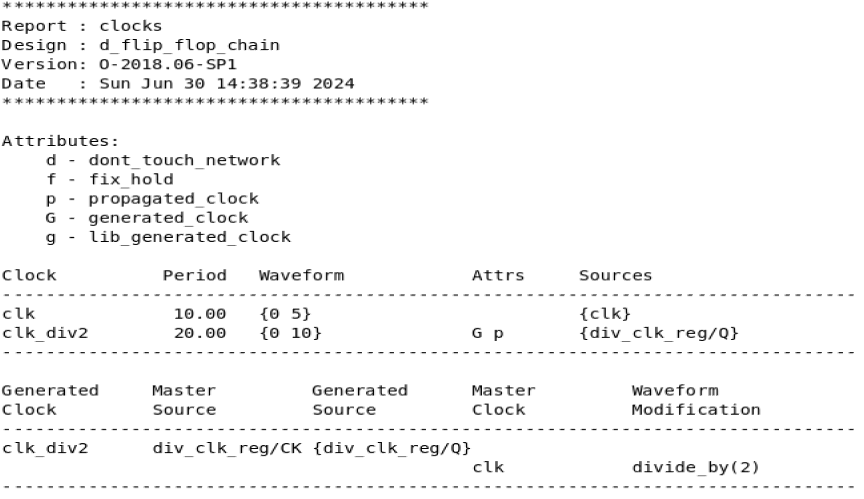

下面使用create_generated_clock命令创建一个二分频的生成时钟,指定的源引脚应该是主时钟的一个扇出引脚,此处指定为分频D触发器的时钟端;指定的源对象为分频D触发器的输出端。图3是此时的时钟报告。

create_generated_clock -divide_by 2 [get_pin div_clk_reg/Q] -source [get_pin div_clk_reg/CK] -name clk_div2

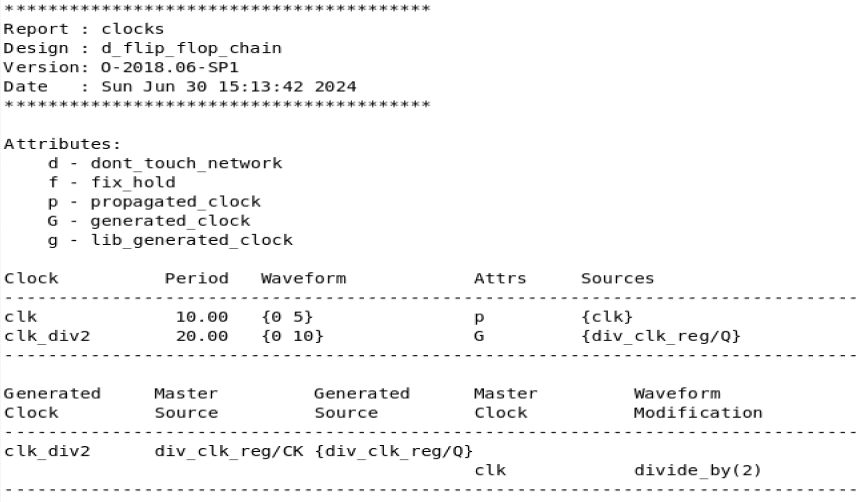

图3 时钟报告

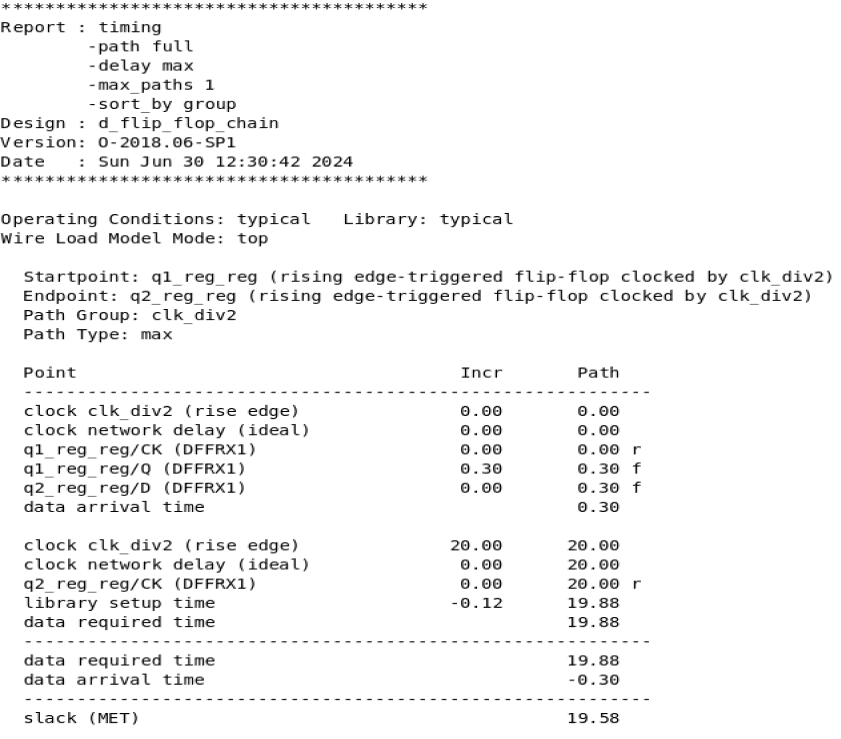

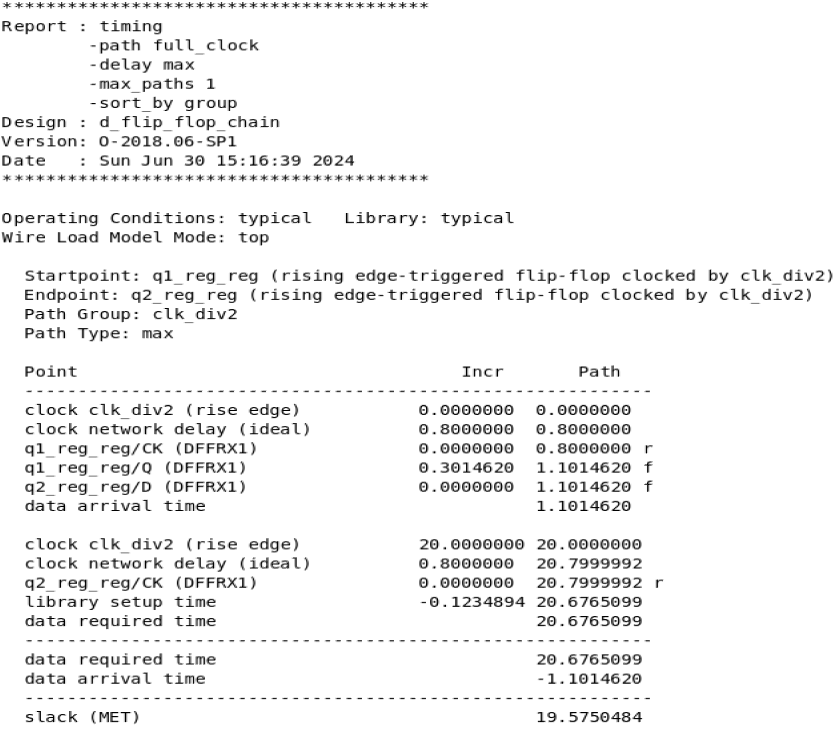

此时的建立时间时序报告如图4所示,可以看到这里已经成功用二分频时钟进行约束了。

图4 建立时钟时序报告

需要注意的是,使用create_generated_clock命令创建的生成时钟和使用create_clock命令创建的时钟一样,也是一个理想时钟,它拥有自己独立的源延迟和网络延迟,它们都是使用set_clock_latency命令进行设置的。

可以使用set_propagated_clock命令,将一个理想的生成时钟转化为一个传播的生成时钟。

考虑三者之间的组合

在已经了解三种时钟后,下面考虑这三者之间的组合,组合情况详见下表。

| 主时钟 | 生成时钟 | 生成时钟是否指定源延迟 | 总延迟(不包含在其中的延迟都会被忽略) |

| 理想 | 理想 | 否 | 生成时钟网络延迟(如有指定) |

| 理想 | 理想 | 是 | 生成时钟源延迟+生成时钟网络延迟(如有指定) |

| 理想 | 传播 | 否 | 生成时钟网络延迟(真实) |

| 理想 | 传播 | 是 | 生成时钟源延迟+生成时钟网络延迟(真实) |

| 传播 | 理想 | 否 | 主时钟源延迟(如有指定)+主时钟网络延迟(真实,由主时钟源对象到生成时钟源对象的时钟路径计算得出)+生成时钟网络延迟(如有指定) |

| 传播 | 理想 | 是 | 生成时钟源延迟+生成时钟网络延迟(如有指定) |

| 传播 | 传播 | 否 | 主时钟源延迟(如有指定)+主时钟网络延迟(真实,由主时钟源对象到生成时钟源引脚的时钟路径计算得出)+生成时钟网络延迟(真实) |

| 传播 | 传播 | 是 | 生成时钟源延迟+生成时钟网络延迟(真实) |

下面将对以上情况分别举例说明,以图1为例,且各自独立。

理想主时钟+理想生成时钟+生成时钟不指定源延迟

使用以下命令进行约束,此时的时钟报告如图5所示,建立时间时序报告如图6所示。

create_clock -period 10 [get_port clk]

create_generated_clock -divide_by 2 [get_pin div_clk_reg/Q] -source [get_pin div_clk_reg/CK] -name clk_div2

set_clock_latency 0.5 [get_clock clk_div2]

图5 时钟报告

图6 建立时间时序报告

理想主时钟+理想生成时钟+生成时钟指定源延迟

使用以下命令进行约束,此时的时钟报告如图7所示,建立时间时序报告如图8所示。

create_clock -period 10 [get_port clk]

create_generated_clock -divide_by 2 [get_pin div_clk_reg/Q] -source [get_pin div_clk_reg/CK] -name clk_div2

set_clock_latency 0.5 [get_clock clk_div2]

set_clock_latency -source 1 [get_clock clk_div2]

图7 时钟报告

图8 建立时间时序报告

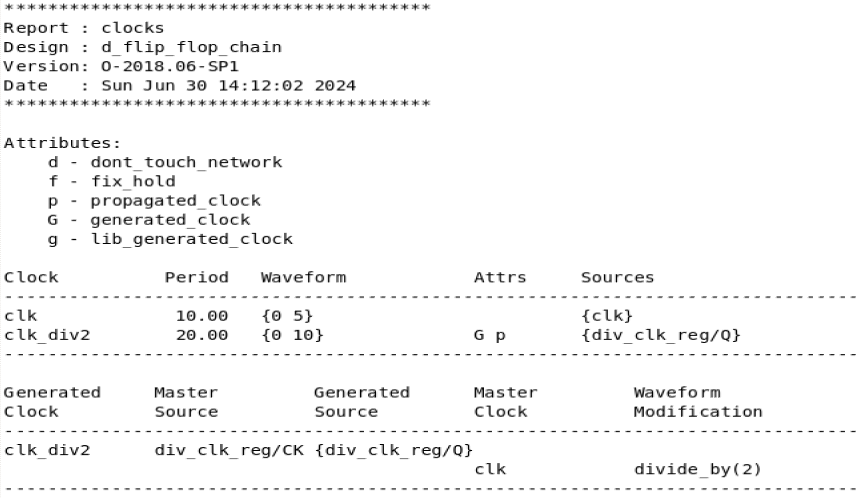

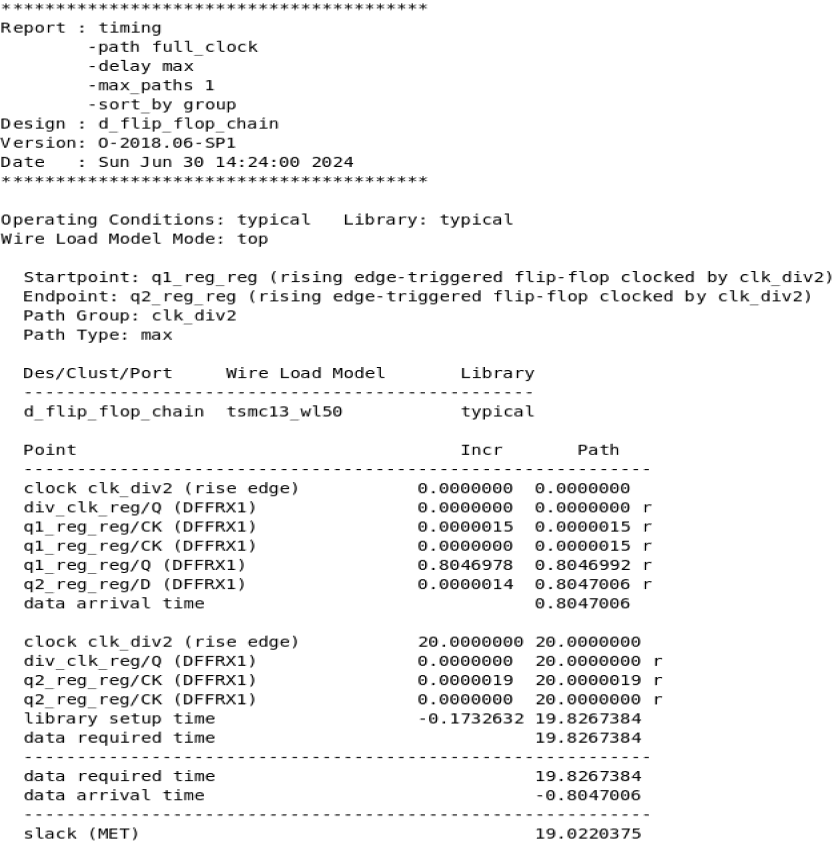

理想主时钟+传播生成时钟+生成时钟不指定源延迟

使用以下命令进行约束(注意,为了引入线延迟,使用了非理想的线负载模型),此时的时钟报告如图9所示,建立时间时序报告如图10所示,此处使用了-path full_clock选项和-significant_digits 7选项,便于观察细节,可以看出总延迟为从div_clk_reg/Q引脚到q1_reg_reg/CK引脚的线延迟0.0000015ns。

create_clock -period 10 [get_port clk]

create_generated_clock -divide_by 2 [get_pin div_clk_reg/Q] -source [get_pin div_clk_reg/CK] -name clk_div2

set_propagated_clock [get_clock clk_div2]

set_wire_load_model -name tsmc13_wl50 -library typical

图9 时钟报告

图10 建立时间时序报告

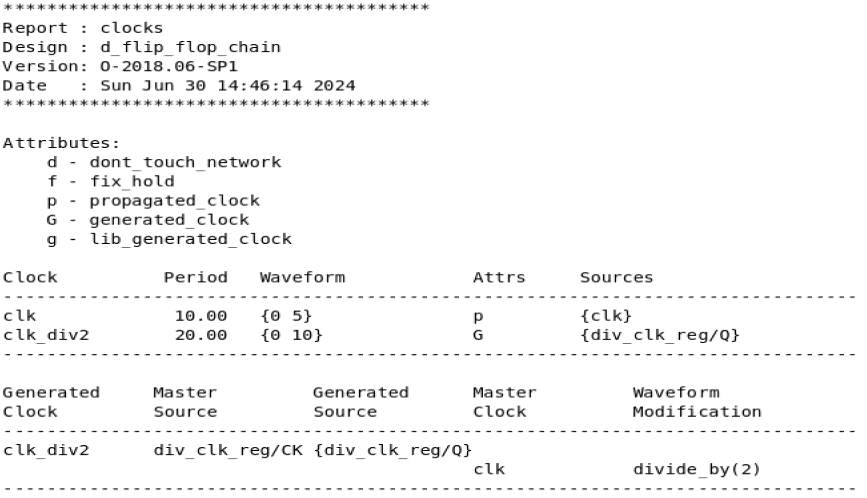

理想主时钟+传播生成时钟+生成时钟指定源延迟

使用以下命令进行约束(注意,为了引入线延迟,使用了非理想的线负载模型),此时的时钟报告如图11所示,建立时间时序报告如图12所示,此处使用了-path full_clock选项和-significant_digits 7选项,便于观察细节,可以看出总延迟为从div_clk_reg/Q引脚到q1_reg_reg/CK引脚的线延迟0.0000014ns(与上例不同是因为四舍五入)加上生成时钟指定源延迟1ns(被统计在生成时钟的clock source latency中)。

create_clock -period 10 [get_port clk]

create_generated_clock -divide_by 2 [get_pin div_clk_reg/Q] -source [get_pin div_clk_reg/CK] -name clk_div2

set_propagated_clock [get_clock clk_div2]

set_clock_latency -source 1 [get_clock clk_div2]

set_wire_load_model -name tsmc13_wl50 -library typical

图11 时钟报告

图12 建立时间时序报告

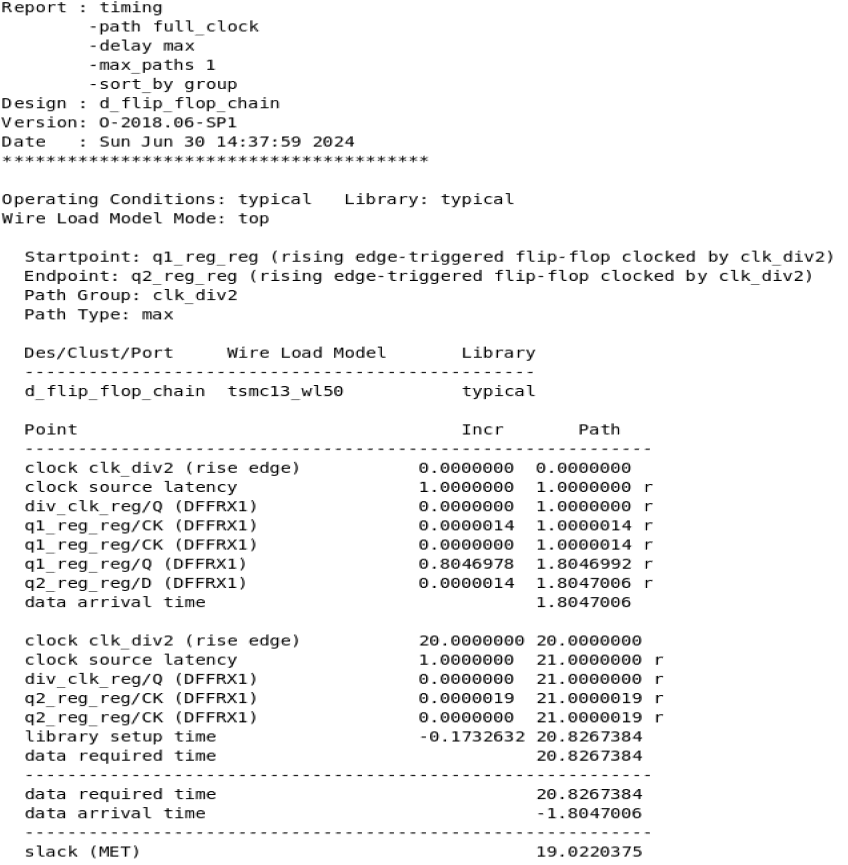

传播主时钟+理想生成时钟+生成时钟不指定源延迟

使用以下命令进行约束(注意,为了引入线延迟,使用了非理想的线负载模型),此时的时钟报告如图13所示,建立时间时序报告如图14所示,此处使用了-significant_digits 7选项,便于观察细节,可以看出总延迟为主时钟源延迟1ns加上从输入端口clk到div_clk_reg/D引脚的线延迟0.0000014ns加上从div_clk_reg/D引脚到div_clk_reg/D引脚的单元延迟0.7710956ns加上生成时钟指定网络延迟0.5ns,总计2.2710972ns。

create_clock -period 10 [get_port clk]

create_generated_clock -divide_by 2 [get_pin div_clk_reg/Q] -source [get_pin div_clk_reg/CK] -name clk_div2

set_propagated_clock [get_clock clk]

set_clock_latency 0.5 [get_clock clk_div2]

set_clock_latency -source 1 [get_clock clk]

set_wire_load_model -name tsmc13_wl50 -library typical

图13 时钟报告

图14 建立时间时序报告

传播主时钟+理想生成时钟+生成时钟指定源延迟

使用以下命令进行约束,此时的时钟报告如图15所示,建立时间时序报告如图16所示,此处使用了-significant_digits 7选项,便于观察细节,可以看出总延迟为生成时钟源延迟0.3ns加上生成时钟网络延迟0.5ns,总计0.8ns。

create_clock -period 10 [get_port clk]

create_generated_clock -divide_by 2 [get_pin div_clk_reg/Q] -source [get_pin div_clk_reg/CK] -name clk_div2

set_propagated_clock [get_clock clk]

set_clock_latency 0.5 [get_clock clk_div2]

set_clock_latency -source 0.3 [get_clock clk_div2]

图15 时钟报告

图16 建立时间时序报告

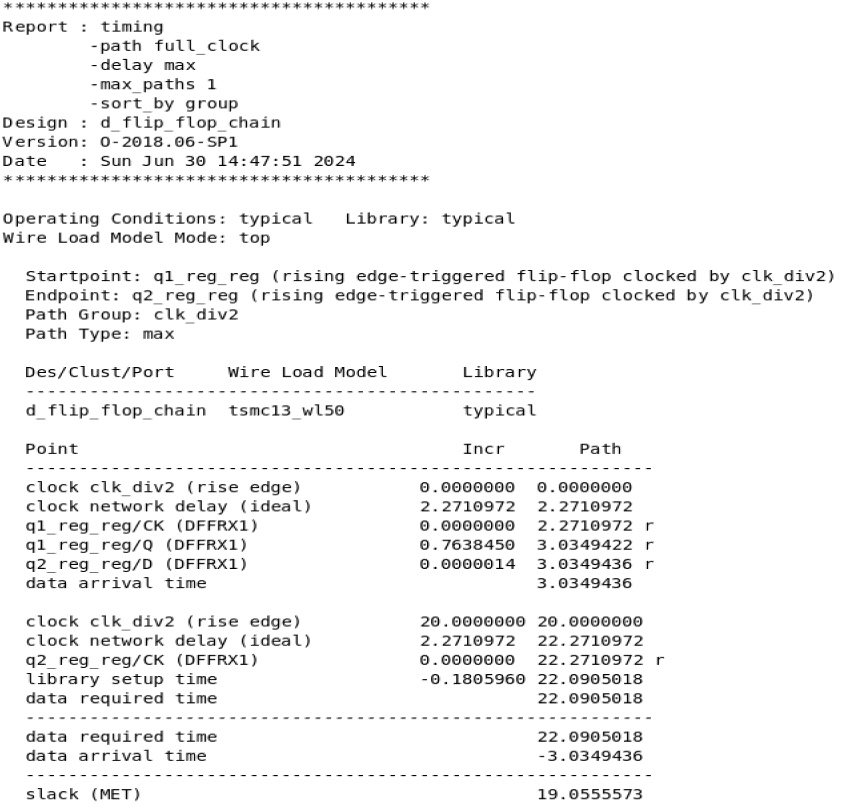

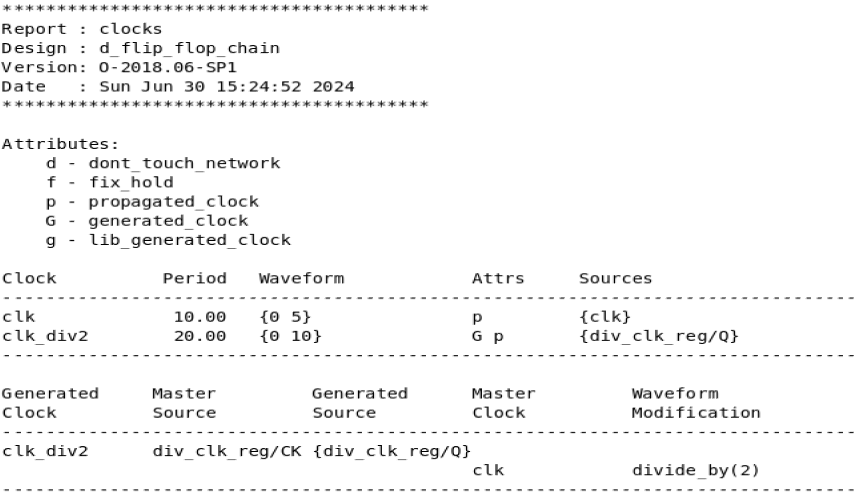

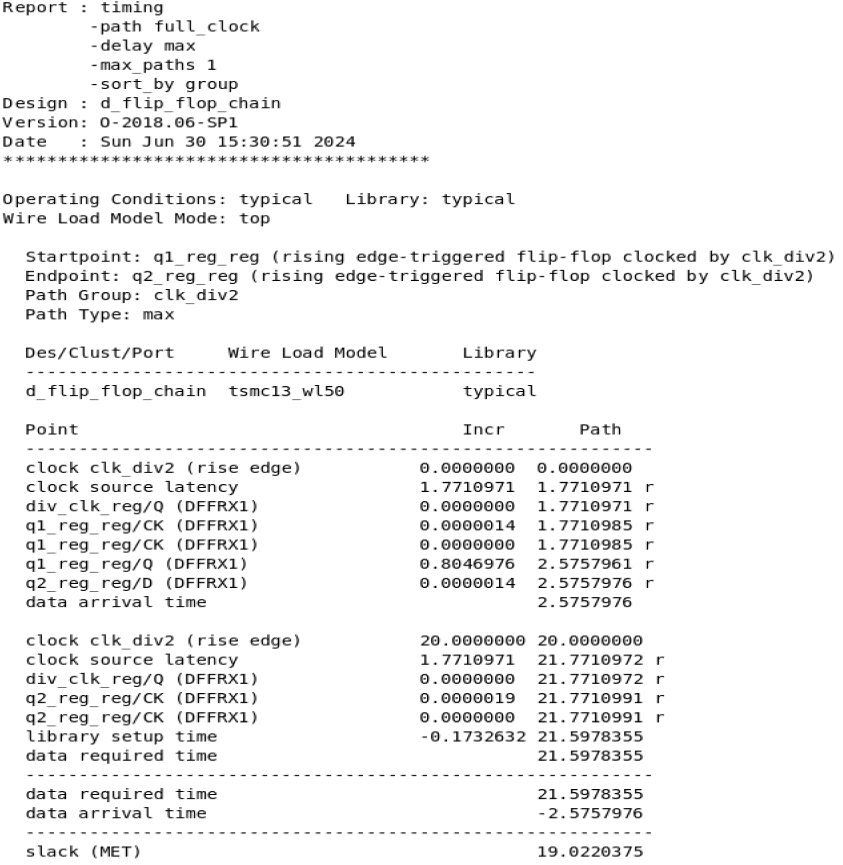

传播主时钟+传播生成时钟+生成时钟不指定源延迟

使用以下命令进行约束(注意,为了引入线延迟,使用了非理想的线负载模型),此时的时钟报告如图17所示,建立时间时序报告如图18所示,此处使用了-path full_clock选项和-significant_digits 7选项,便于观察细节,可以看出总延迟为主时钟源延迟1ns加上从输入端口clk到div_clk_reg/D引脚的线延迟0.0000014ns加上从div_clk_reg/D引脚到div_clk_reg/D引脚的单元延迟0.7710956ns(前面这些延迟被统计在生成时钟的clock source latency中),加上从div_clk_reg/D引脚到q1_reg_reg/CK引脚的0.0000014ns,总计1.7710984ns。

create_clock -period 10 [get_port clk]

create_generated_clock -divide_by 2 [get_pin div_clk_reg/Q] -source [get_pin div_clk_reg/CK] -name clk_div2

set_propagated_clock [get_clock clk]

set_propagated_clock [get_clock clk_div2]

set_clock_latency -source 1 [get_clock clk]

set_wire_load_model -name tsmc13_wl50 -library typical

图17 时钟报告

图18 建立时间时序报告

4029

4029

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?