module test_v1(

input clk,

input rst_n,

input [12:0]data_in,

output [5:0]num

);

reg [5:0]num_r;

integer i;

assign num=num_r;

always@(posedge clk or negedge rst_n)

if(!rst_n)

num_r=6'd0;

else begin

num_r=6'd0;

for(i=0;i<=12;i=i+1)

begin

if(data_in[i])

num_r=num_r+1'b1; //循环语句使用阻塞赋值,因为非阻塞赋值只在周期结束时赋值,会导致循环只执行一次

else

num_r=num_r;

end

end

endmodule

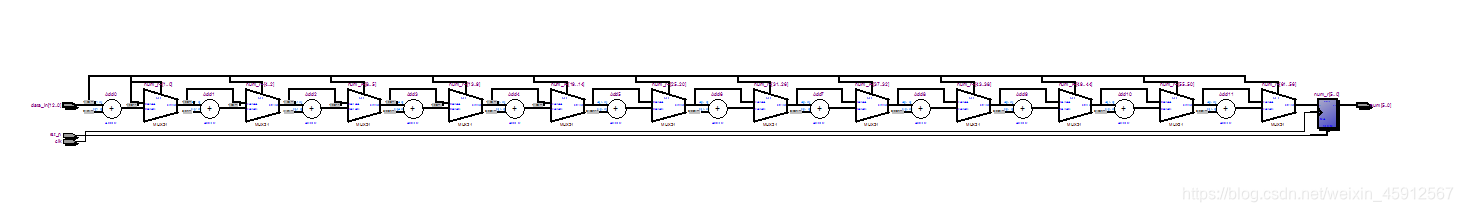

综合的电路如图所示

可知for语句在综合后,就是把相同的电路复制若干次

Verilog循环计数器设计

Verilog循环计数器设计

本文介绍了一种使用Verilog实现的循环计数器设计,该设计接收13位输入数据,通过for循环统计其中的1的数量,并将结果输出为6位的二进制数。文章详细解释了如何使用阻塞赋值来确保循环能够正确执行。

本文介绍了一种使用Verilog实现的循环计数器设计,该设计接收13位输入数据,通过for循环统计其中的1的数量,并将结果输出为6位的二进制数。文章详细解释了如何使用阻塞赋值来确保循环能够正确执行。

2472

2472

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?