背景

如果想在 Xilinx 的FPGA上构建一个 RAM,通常有两种方式:

- 使用逻辑资源LUT组成DRAM,一般来说是用verilog声明一个多维数组即可

- 使用开发板上内嵌专用的BRAM,一般来说需要使用Xilinx提供的IP核

Block Memory Generator 就是使用了开发板上的BRAM。我在一个项目中需要对该IP核进行初始化,主要是使用 coe 文件初始化存储,因此本文主要介绍如何使用并初始化 Xilinx 提供的IP核 Block Memory Generator v8.4 ,为了确保成功初始化,还对其进行了一个简单的仿真,更多细节请参考官方手册。

IP核的使用

创建工程后,点击左侧的 IP Catalog,搜索 Block Memory Generator ,双击对应的IP核,会打开如下所示的配置界面

如果要查看该IP核的文档,可以点击左上角

Documentation查看;如果打开的DocNav显示无法查看pdf,只要点击Open to Print即可下载说明文档,用自带的pdf阅读器查看文档

现在对其主要的配置作一个简单的介绍:

Component Name:设置该IP核的名称,我这里保持了默认。Interface Type:RAM接口总线。这里保持默认,选择Native接口类型(标准RAM接口总线);Memory Type:存储器类型。可配置成Single Port RAM(单端口RAM)、Simple Dual Port RAM(伪双端口RAM)、True Dual Port RAM(真双端口RAM)、Single Port ROM(单端口ROM)和Dual Port ROM(双端口ROM),这里选择Simple Dual Port RAM。ECC Options:Error Correction Capability,纠错能力选项,这里保持默认。Write Enable:字节写使能选项,勾中后可以单独将数据的某个字节写入RAM中,这里不使能。Algorithm Options:算法选项。可选择Minimum Area(最小面积)、Low Power(低功耗)和Fixed Primitives(固定的原语),这里选择默认的Minimum Area。

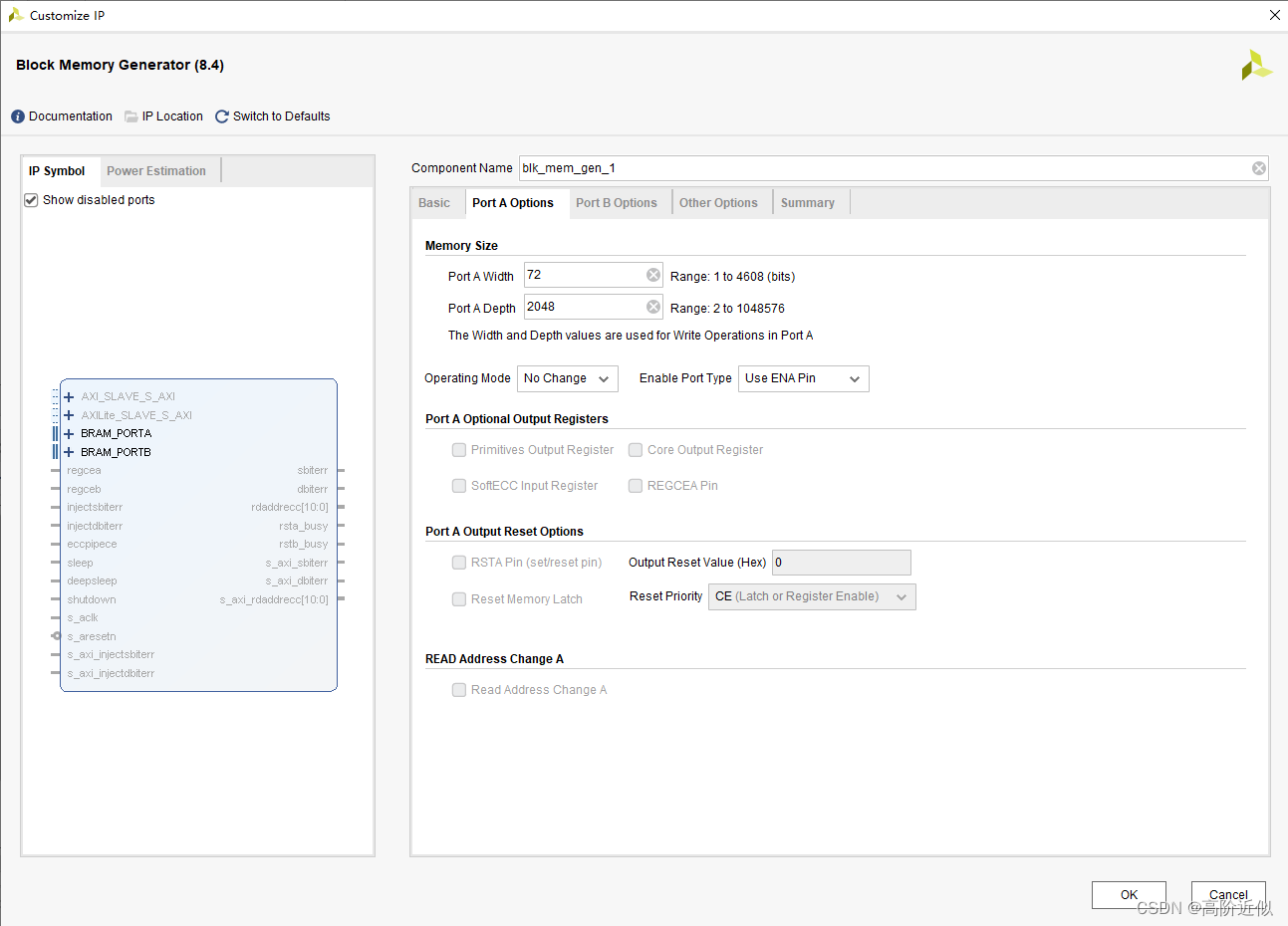

接下来切换至 Port A 选项页,设置端口A的参数,该页面配置如下:

这里将 Port A Width 和 Port A Depth 分别设置为 72 和 2048,实际的宽度和深度请根据需求来设定。其他选项均保持默认。

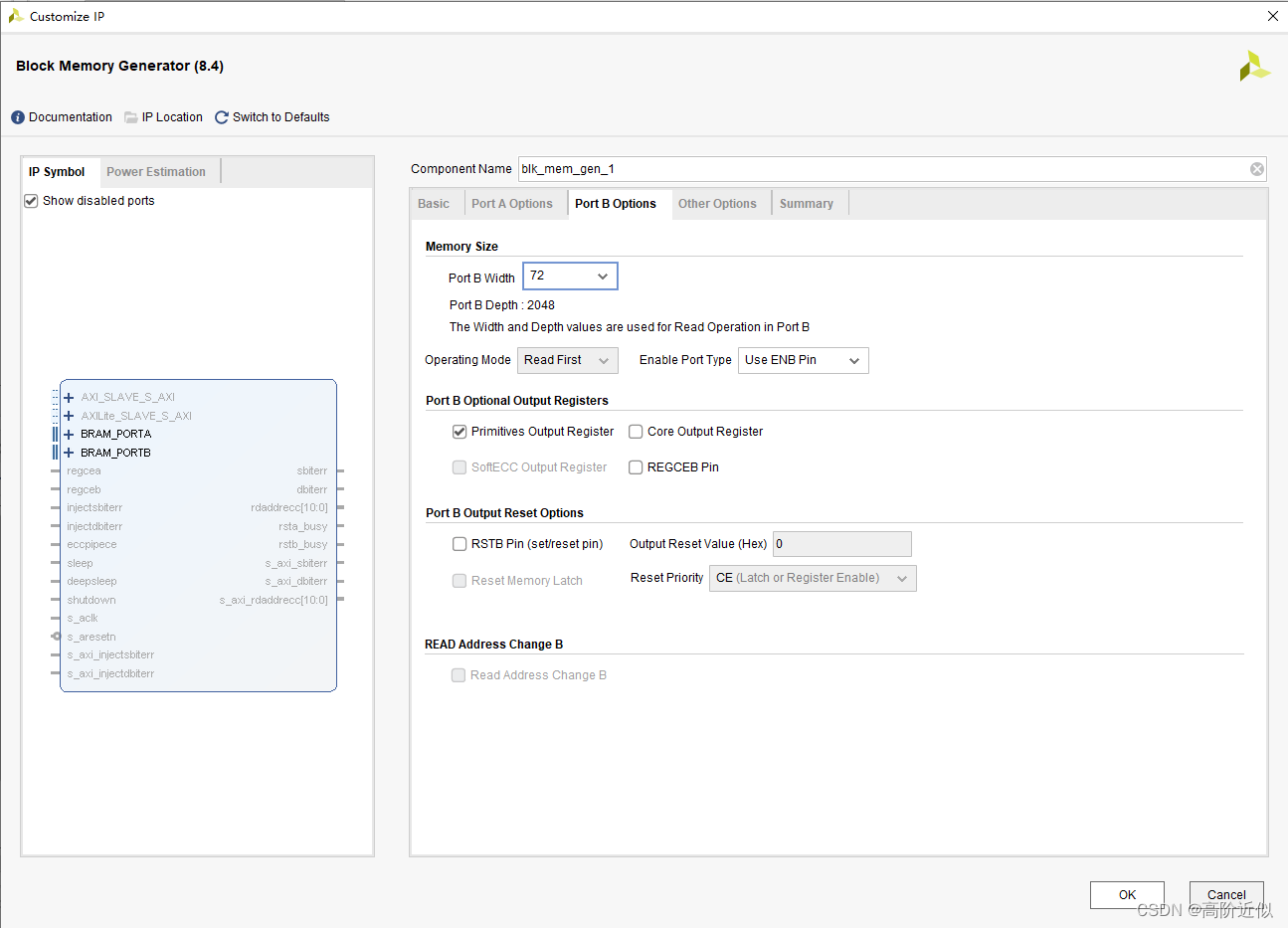

接下来切换至 Port B 选项页,设置端口B的参数,该页面配置如下:

这里将 Port B Width 设置为 72,实际的宽度请根据需求来设定。其他选项均保持默认。

完成配置后,点击右下角 OK,紧接着会弹出 Genarate Output Products 的窗口,直接点击 Generate 即可

初始化

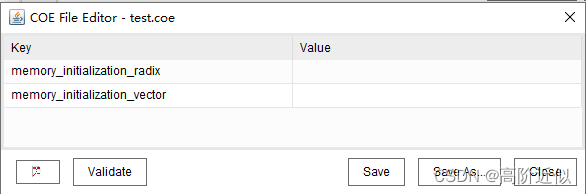

重新打开IP核的配置界面,切换到 Other Options 选项页,勾选上 Load Init File,然后点击 Edit 按钮,如果弹窗显示 No COE file specified. Create/Choose?,点击 OK 然后选择coe文件的路径和名字即可。最终会弹出下面的窗口。

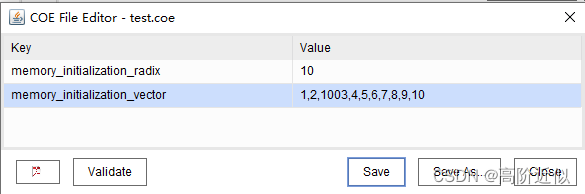

第一行是用于指定第二行输入的值是什么进制的,比如第一行输入10,那么第二行输入的值都应该是十进制。

完成第一行输入后,第二行可以输入一系列值,相邻的值用逗号分隔,下图是一个示例。

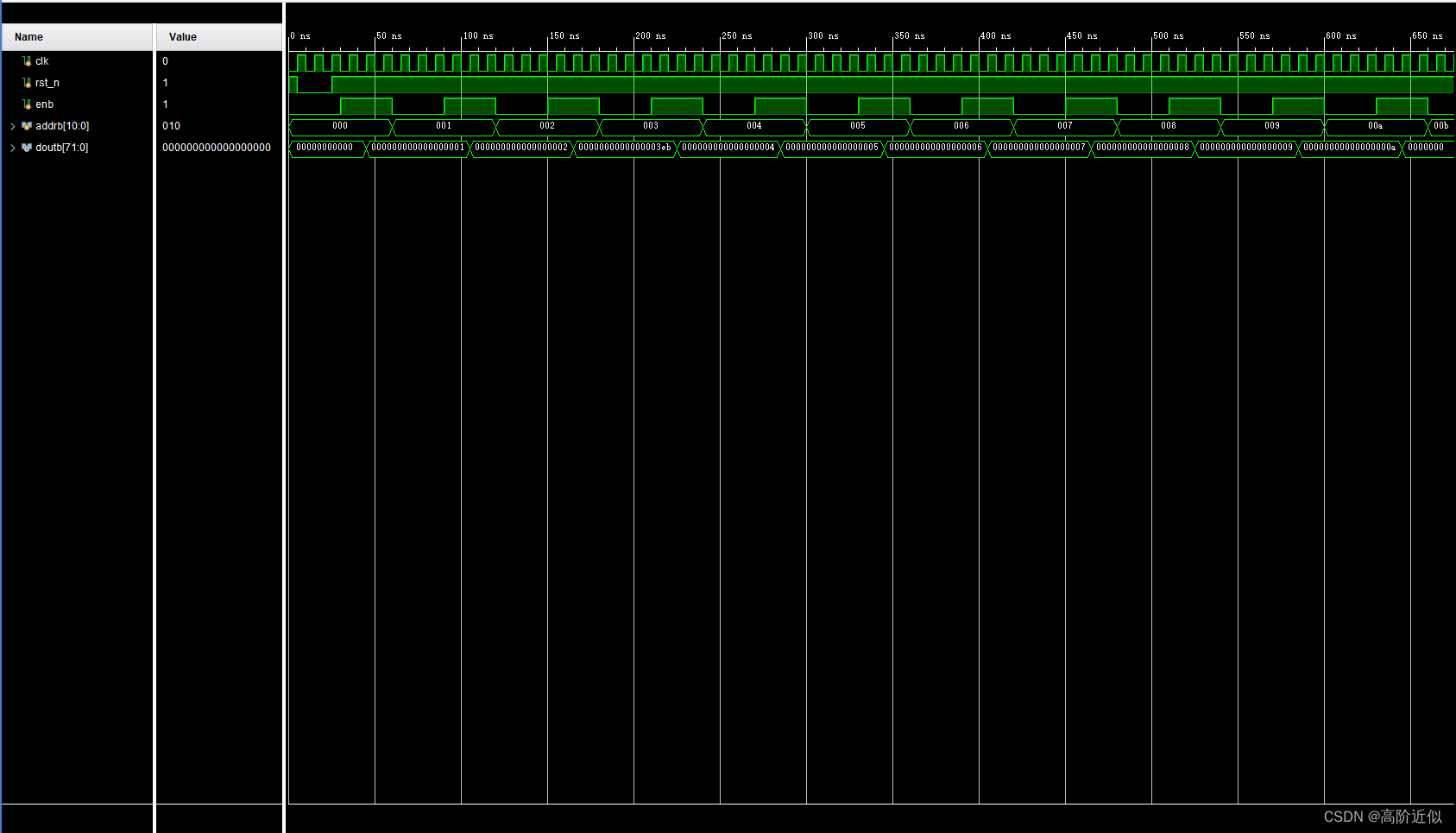

由于配置的宽度是72,因此第一个72比特的值是1,第二个72比特的值是2,第三个72比特的值是1003,以此类推。后面将通过仿真来验证这一点。

完成后点击 Save,然后关闭窗口,点击配置界面右下角OK,重新 Generate 即可。

后面如果要改初始化的内容,可以直接修改对应的coe文件即可,但是最好去配置界面里重新加载初始化文件,因为直接修改coe文件,可能IP核还是使用的旧coe文件的内容

仿真

编写测试代码,如下所示

module test_mem();

reg clk;

reg rst_n;

reg enb;

reg [10:0] addrb;

wire [71:0] doutb;

blk_mem_gen_0 mem_instance(

.clka(clk),

.ena(1'b0),

.wea(1'b0),

.addra(11'b0),

.dina(72'b0),

.clkb(clk),

.enb(enb),

.addrb(addrb),

.doutb(doutb)

);

always #5 clk = ~clk;

initial begin

clk = 1'b0;

rst_n = 1'b1;

enb = 1'b0;

addrb = 11'b0;

#5;

rst_n = 1'b0;

#20;

rst_n = 1'b1;

end

always #60 addrb = addrb + 11'b001;

always #30 enb = ~enb;

endmodule

仿真波形如下所示

2155

2155

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?