分频器介绍

在数电系统设计中,分频器的应用非常的广泛,它的功能就是对高频率的信号进行分频。分频器的本质上是加法器的演变,其计数值由分频系N=fin/fout决定,分频器输出的不是普通的计数值,而是根据分频系数对输出信号高低电平进行控制。分频器常用于数字电路中的时钟分频,用以得到较低的时钟信号、选通信号、中断信号等。分频器在公司的笔试题是必考题,这里我们主要介绍几种分频器,偶数分频、奇数分频。

偶数分频器

偶数分频器是指分频系数为偶数,分频系数为N=2n(n=1,2,3....)。例如,输入的时钟信号为f,那么偶数分频器输出的时钟信号为F=f/2n(n=1,2,3....)。

分频系数为2的整数次幂的分频器

- clk_even_div程序接口

| 名称 | 方向 | 位宽 | 说明 |

| clk | Input | 1 | 工作时钟 |

| reset | Input | 1 | 复位信号(active high) |

| clk_div | Output | 1 | 分频时钟信号 |

module clk_even_div(

input clk,

input reset,

output reg clk_div=0

);

reg [2:0]cnt_div=0;

//实现计数器计数功能

always @(posedge clk)

begin

if(reset)begin

cnt_div<=3'd0;

clk_div<=1'b0;

end

else if(cnt_div==3'd6)begin

cnt_div<=3'd0;

clk_div<=~clk_div;

end

else begin

cnt_div<=cnt_div+1'b1;

end

end

endmodule测试文件:

module TB_clkdiv(

);

reg clk;

reg reset;

wire clk_div;

clk_even_div inst_clk_even_div(

.clk (clk),

.reset (reset),

.clk_div (clk_div)

);

initial begin

clk=0;

reset=1;

#100;

reset=0;

end

always #10 clk=~clk;//50M 时钟

endmodule仿真结果:

分频系数不是2的整数次幂的分频器

对于分频系数不是2的整数次幂的分频器来说,我们可以使用计数器实现分频功能,至需要我们对计数器进行一些控制操作。例如,分频系数是14,那么我们就计数到6时对分频信号就行取反操作就可以了。

clk_even_div程序接口

| 名称 | 方向 | 位宽 | 说明 |

| clk | Input | 1 | 工作时钟 |

| reset | Input | 1 | 复位信号(active high) |

| clk_div | Output | 1 | 分频时钟信号 |

测试文件:

仿真结果:

奇数分频器

奇数分频器就是分频系数为奇数N=2n+1(n=1,2,3.....).如果输入的时钟信号为f,那么分频时钟信号为f/(2n+1);奇数分频器在公司笔试中用的最多。

占空比为1:1的奇数分频器

占空比为1:1的技术分频器需要在输入时钟信号的下降沿时进行翻转操作。这种分频器的设计需要两个计数器,一个计数器采用时钟的上升沿触发,另一个计数器采用时钟的下降沿触发;两个计数器的模和分频系数相同,然后根据两个计数器的并行信号输出决定两个相应的电平控制信号;最后对两个电平控制信号进行相应的逻辑运算就可以了。

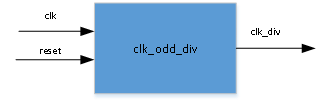

clk_odd_div程序接口

| 名称 | 方向 | 位宽 | 说明 |

| clk | Input | 1 | 工作时钟 |

| reset | Input | 1 | 复位信号(active high) |

| clk_div | Output | 1 | 分频时钟信号 |

module clk_odd_div(

input clk,

input reset,

output clk_even

);

reg [3:0]count1,count2;

reg clka,clkb;

parameter N=5;//改变N的值就可以得到不同的奇分频的波形(占空比是1:1的)

assign clk_even=clka|clkb;

///

always @(posedge clk )

begin

if(reset)

begin

count1<=0;

clka<=0;

end

else

begin

if(count1<(N-1))

begin

count1<=count1+1;

if(count1<(N-1)/2)

begin

clka<=0;

end

else if(count1>=(N-1)/2)

begin

clka<=1;

end

end

else

begin

clka<=0;

count1<=0;

end

end

end

always @(negedge clk )

begin

if(reset)

begin

count2<=0;

clkb<=0;

end

else

begin

if(count2<(N-1))

begin

count2<=count2+1;

if(count2<(N-1)/2)

begin

clkb<=0;

end

else if(count2>=(N-1)/2)

begin

clkb<=1;

end

end

else

begin

clkb<=0;

count2<=0;

end

end

end

endmodule 测试文件

仿真结果

想学习FPGA的联系我哦!

2302

2302

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?