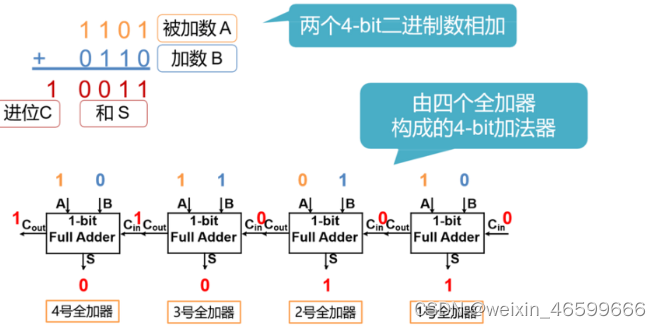

行波加法器的电路图构成

module adder4bit(

input [3:0] a,

input [3:0] b,

input c_in,

output [3:0] sum,

output c_out

);

wire c1, c2, c3;

adder1bit a1(a[0],b[0],c_in,sum[0],c1);

adder1bit a1(a[1],b[1],c1,sum[1],c2);

adder1bit a1(a[2],b[2],c2,sum[2],c3);

adder1bit a1(a[3],b[3],c3,sum[3],c_out);

endmodule

module adder1bit(

input a,

input b,

input c_in,

output sum,

output c_out

);

assign sum = a ^ b ^ c_cin;

assign c_out = (a & b) + (a ^ b) & c_cin;

endmodule

这篇博客详细介绍了如何使用Verilog语言设计一个4位行波加法器。通过4个1位全加器模块级联,实现了4位二进制数的加法运算。每个adder1bit模块分别处理一对输入位,并根据前一位的进位信号进行计算,最终输出总和和进位信号。这是一个基础的数字逻辑电路设计实例。

这篇博客详细介绍了如何使用Verilog语言设计一个4位行波加法器。通过4个1位全加器模块级联,实现了4位二进制数的加法运算。每个adder1bit模块分别处理一对输入位,并根据前一位的进位信号进行计算,最终输出总和和进位信号。这是一个基础的数字逻辑电路设计实例。

9590

9590

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?