一、verilog原代码

module top_module(

input clk,

input reset,//复位信号

input ena,//使能信号

output pm, //pm对于上午am是0,pm对于下午pm是1

output [7:0] hh,//输出的时针时刻

output [7:0] mm,//输出的分钟时刻

output [7:0] ss);//输出的秒针时刻

reg pm_temp;//用来区分上下午

wire fanzhuan;//反转标志信号,检测11:59:59的存在

reg [3:0] ss_one;//秒针的个位

reg [3:0] ss_ten;//秒针的十位

reg [3:0] mm_one;//分针的个位

reg [3:0] mm_ten;//分针的十位

reg [3:0] hh_one;//时针的个位

reg [3:0] hh_ten;//时针的十位

//第一部分:秒针部分

always@(posedge clk)//先来写秒针的个位部分

begin

if(reset)

begin

ss_one <= 4'b0;

end

else if(ena)//使能端工作

begin

if(ss_one == 4'd9)

ss_one <= 4'b0;

else

ss_one <= ss_one + 1'b1;

end

end

always@(posedge clk)//写秒针的十位部分

begin

if(reset)//复位信号工作了

begin

ss_ten <= 4'b0;

end

else if((ena)&&(ss_one == 4'd9))//使能端端工作且个位已经加满了,十位开始计数

begin

if(ss_ten == 4'd5)//十位加满了

ss_ten <= 4'b0;

else

ss_ten <= ss_ten +1'b1;

end

end

//第二部分:分钟部分

always @(posedge clk)//先来写分钟的个位部分

begin

if(reset)

mm_one <= 4'd0;

else if((ena)&&(ss_one == 4'd9)&&(ss_ten == 4'd5))//使能端工作,且到了分针个位该动的时候

begin

if(mm_one == 4'd9)

mm_one <= 4'd0;

else

mm_one <= mm_one + 1'b1;

end

end

always@(posedge clk)//写分针的十位部分

begin

if(reset)//复位信号工作了

begin

mm_ten <= 4'd0;

end

else if((ena)&&(ss_one == 4'd9)&&(ss_ten == 4'd5)&&(mm_one == 4'd9))//使能端端工作且个位已经加满了,十位开始计数

begin

if(mm_ten == 4'd5)//十位加满了

mm_ten <= 4'd0;

else

mm_ten <= mm_ten +1'b1;

end

end

//第三部分:时针部分------这部分比较重要

always@(posedge clk)//先来写时针的个位部分

begin

if(reset)

hh_one <= 4'd2;//从12点进行切换,复位的时候,直接就是12:00

else if((ena)&&((ss_one == 4'd9)&&(ss_ten == 4'd5)&&(mm_one == 4'd9)&&(mm_ten == 4'd5)))//使能端工作

begin

if(hh_one == 4'd9)

hh_one <= 4'd0;

else if((hh_ten == 4'd1)&&(hh_one == 4'd2)) //已经到12点

begin

hh_one <= 4'b1;

end

else

hh_one <= hh_one + 1'b1;

end

end

always @(posedge clk)//再来写时针的十位部分

begin

if(reset)

begin

hh_ten <= 4'd1;

end

else if((ena)&&((ss_one == 4'd9)&&(ss_ten == 4'd5)&&(mm_one == 4'd9)&&(mm_ten == 4'd5)))

begin

if((hh_ten == 4'd1)&&(hh_one == 4'd2))//如果12点了,十位置零

hh_ten <= 4'd0;

else if(hh_one == 4'd9)//等到个位是9的时候,十位加1

hh_ten <= hh_ten+1'b1;

end

end

always @(posedge clk)

begin

if(reset)

begin

pm_temp <= 1'b0;

end

else if(fanzhuan)

begin

pm_temp <= ~pm_temp; //检测到11:59:59 该换了

end

end

assign hh = {hh_ten,hh_one};

assign mm = {mm_ten,mm_one};

assign ss = {ss_ten,ss_one};

assign fanzhuan = (ena)&&(ss_one == 4'd9)&&(ss_ten == 4'd5)&&(mm_one == 4'd9)&&(mm_ten == 4'd5)&&(hh_ten == 4'd1)&&(hh_one==4'd1);

//fanzhuan在11:59:59的时候成立,如果成立,pm=1

assign pm = pm_temp;

endmodule

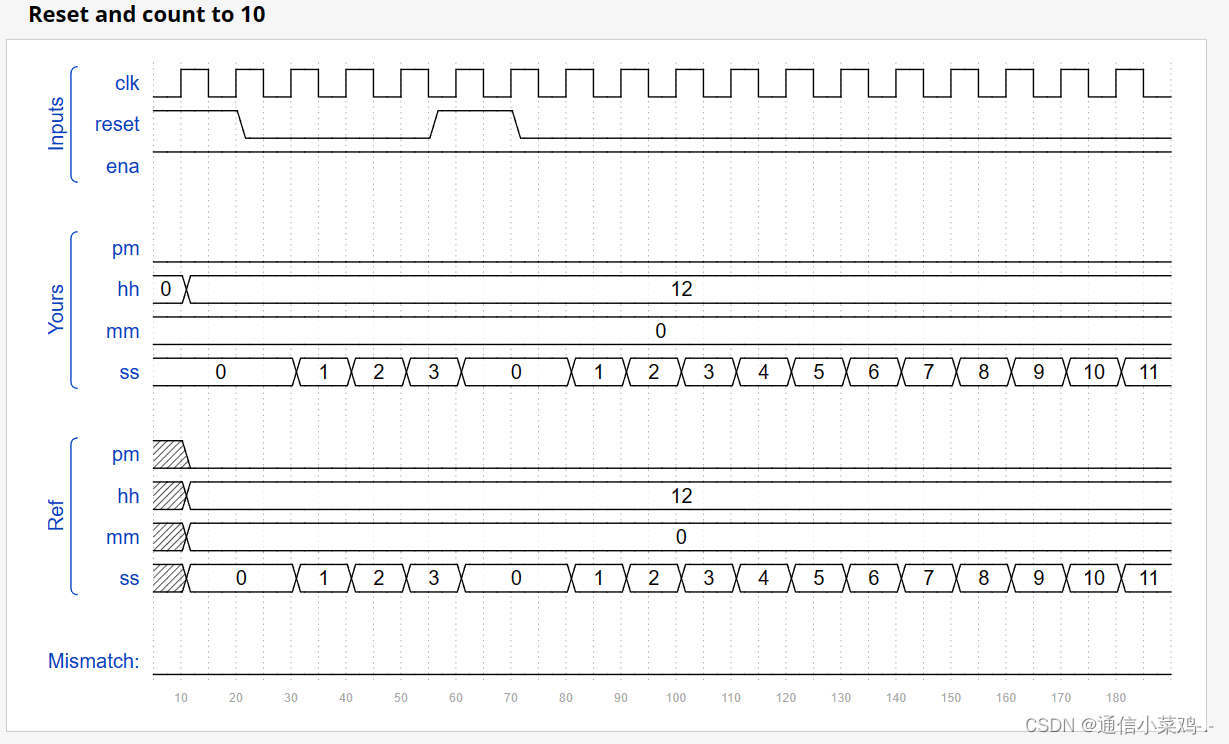

二、仿真图

5794

5794

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?