1位全加器

一、1位全加器

1. 基本原理

真值表:

二、绘制原理图实现1位全加器

1. 半加器实现

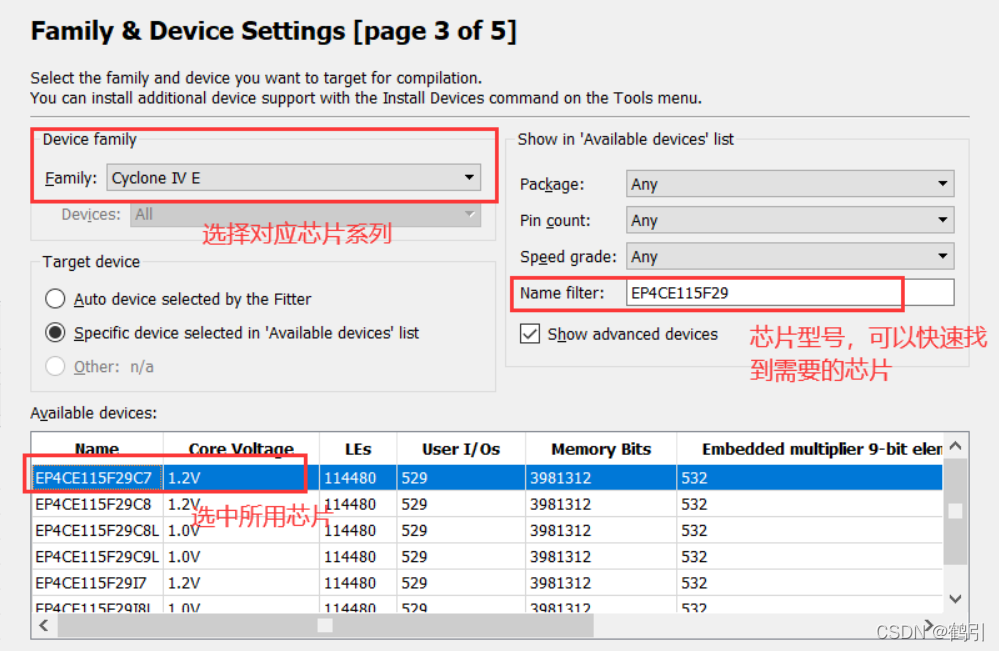

- 创建工程文件,并勾选所需型号芯片

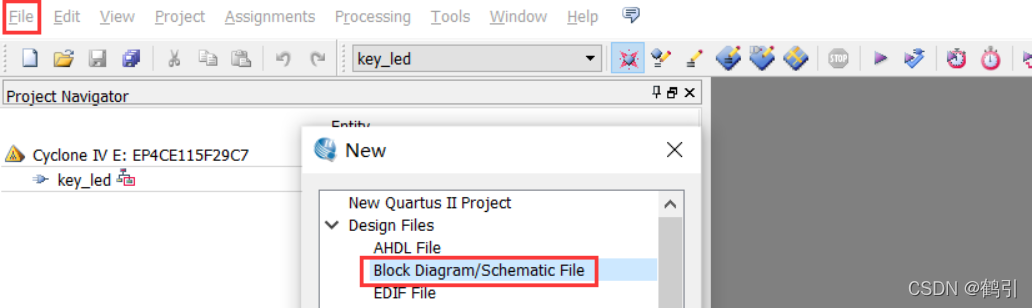

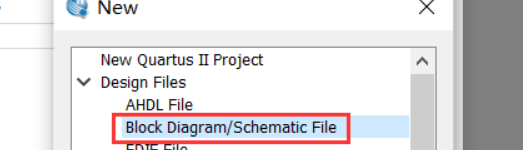

- File->New,进入后选择Block Diagram/Schematic File

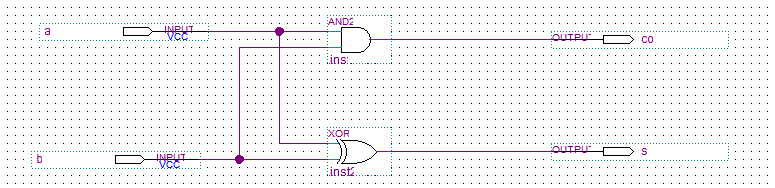

- 选择原件,实现半加器需要 一个and2 一个xor原件,后进行电路连接

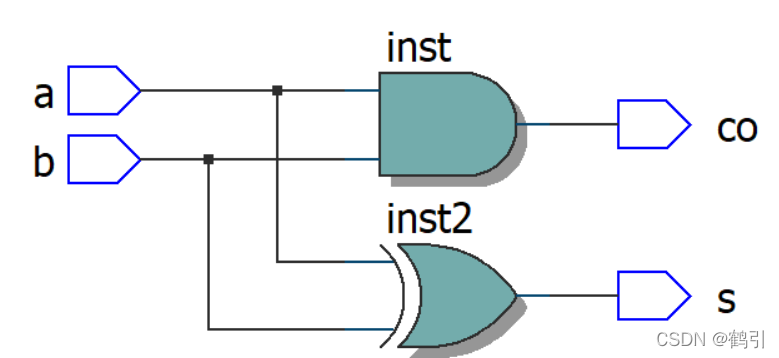

- 保存文件,并通过RTL Viewer查看线路效果图

- 仿真测试半加器是否正确

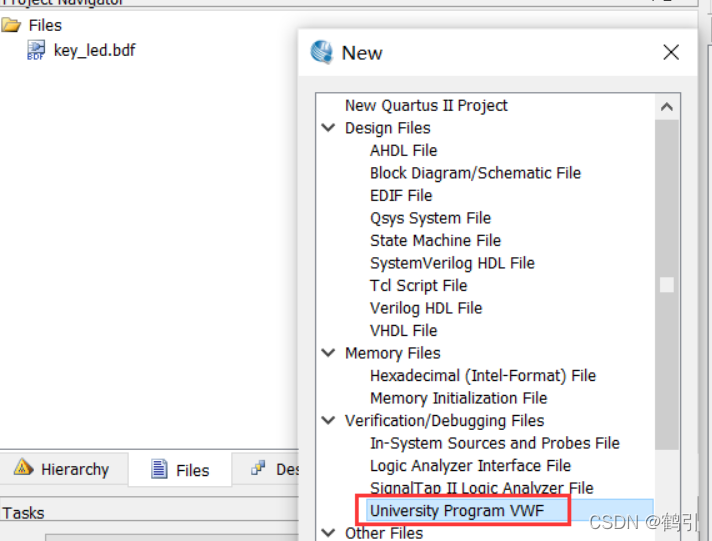

- 新建向量波形文件

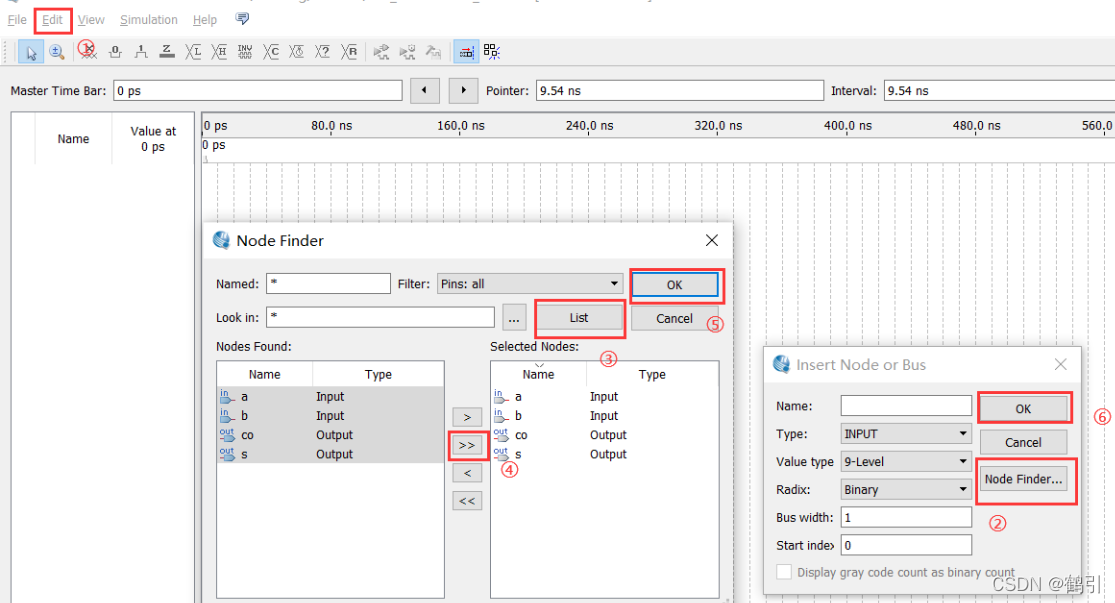

- 添加信号,及所设引脚

- 编辑信号,并进行仿真操作

半加器运行效果

- 新建向量波形文件

2. 全加器实现

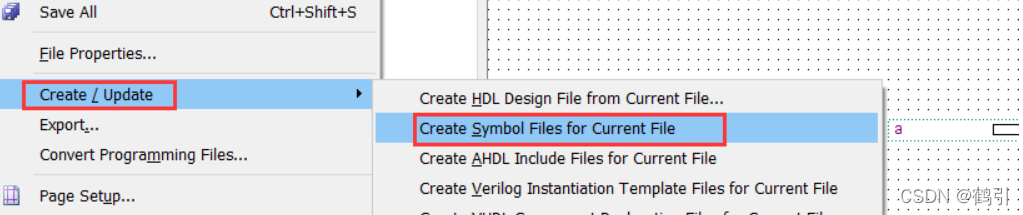

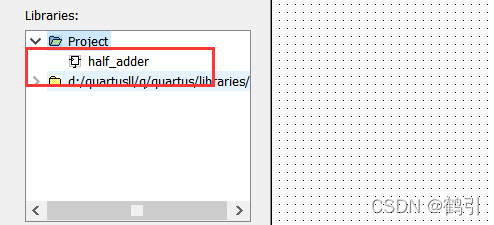

- 全加器的实现是基于半加器模块实现,通过多个半加器原件实现全加器,需要将半加器原件文件设置为可调

File-> Create/Update→CreateSymbolFilesforCurrentFile将当前文件h_adder.bdf变成一个元件符号存盘,以待在高层次设计中调用

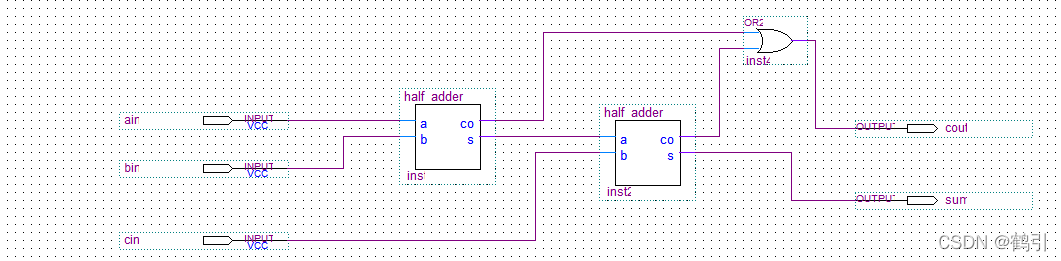

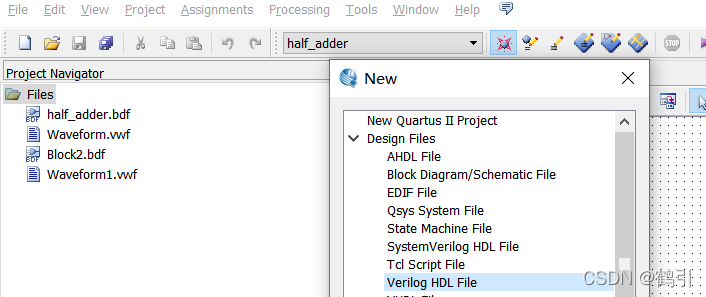

- 绘制全加器原理图

- 新建原理图绘制 File->New -> Block Diagram/Schematic File

- 勾选原件,此时可以使用已经绘制的半加器原件,进行使用

- 勾选所需原件,绘制全加器原理图

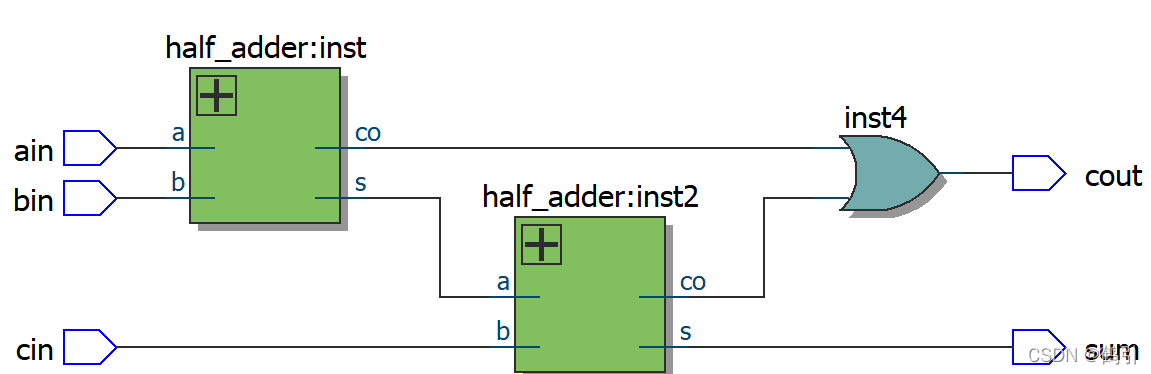

- 保存原理图,并进行测试是否存在问题,并通过RTL 查看器件电路图

- 新建原理图绘制 File->New -> Block Diagram/Schematic File

- 仿真实现

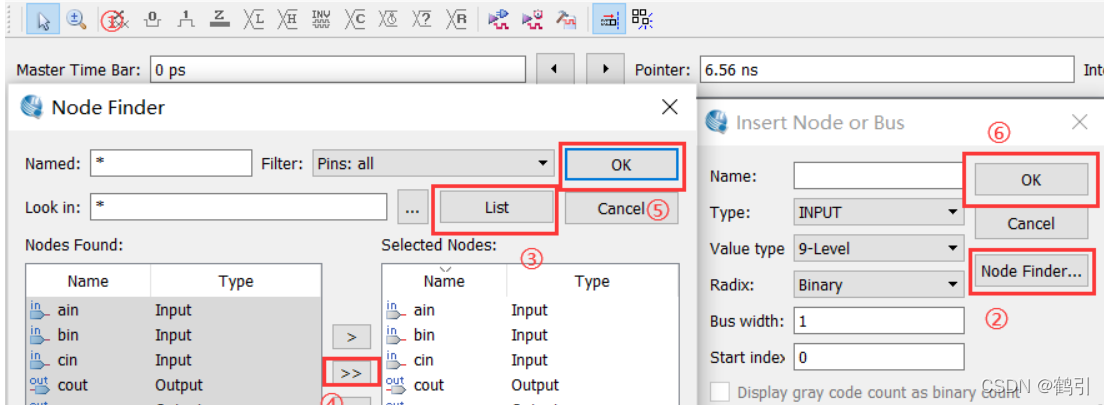

- 创建波形文件,并添加信号

- 编辑信号,并进行仿真操作,查看波形

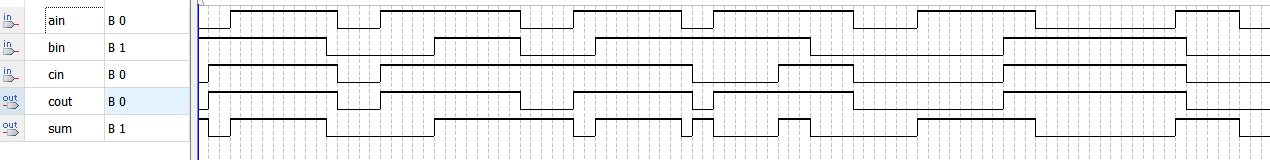

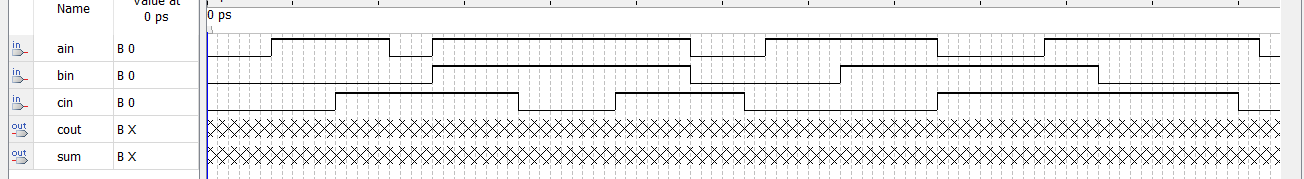

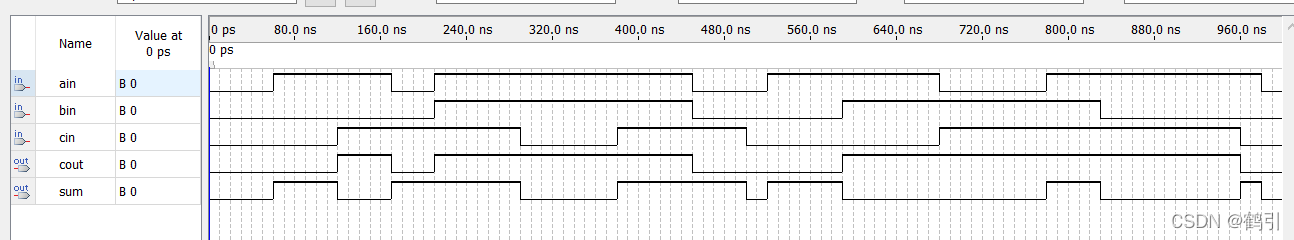

功能仿真:

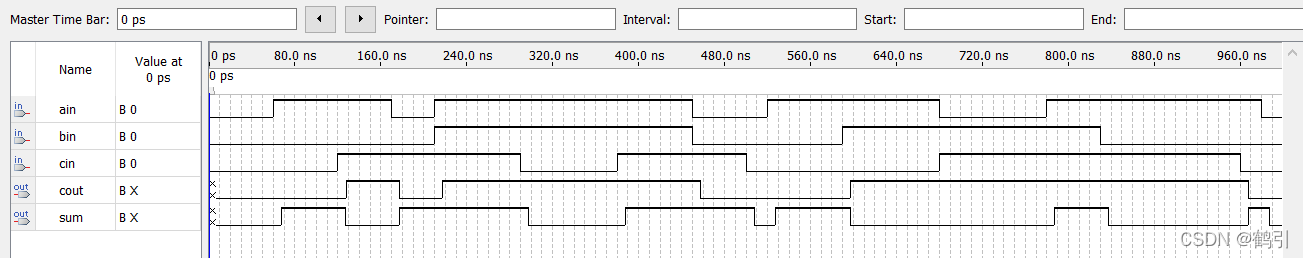

时序仿真

- 创建波形文件,并添加信号

三、Verilog实现一位全加器

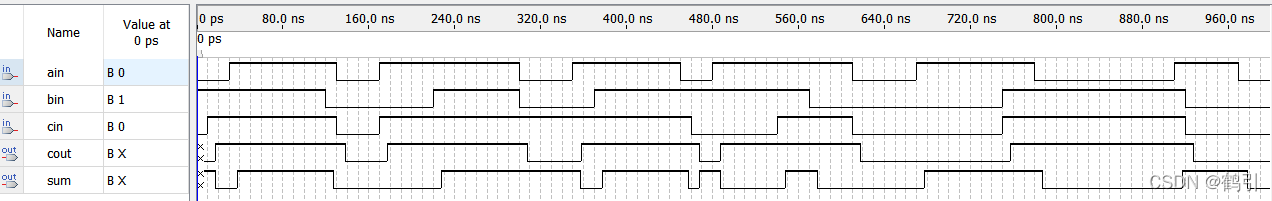

- 新建工程项目,并建立Verilog文件

- 编写Verilog一位全加器,并运行查看电路图

module Fulladder(

input ain,bin,cin,//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

output reg cout,sum//输出信号,cout表示向高位的进位,sum表示本位的相加和

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;

end

endmodule

3. 新建波形文件,添加信号并进行仿真测试

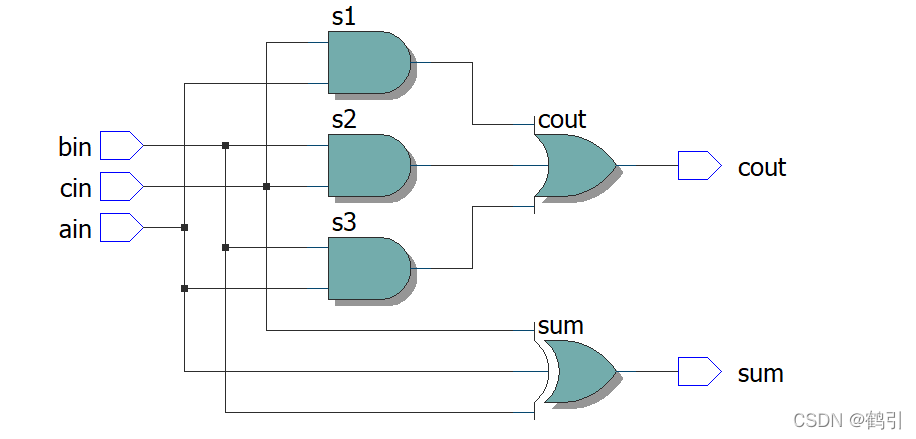

- 功能仿真

- 时序仿真

四、硬件测试

1. 原理图测试

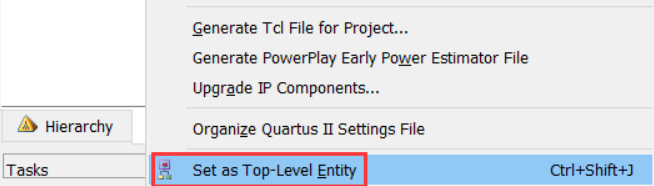

- 设置原理图为顶层文件,方便后续调用

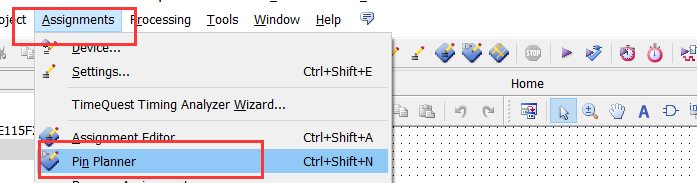

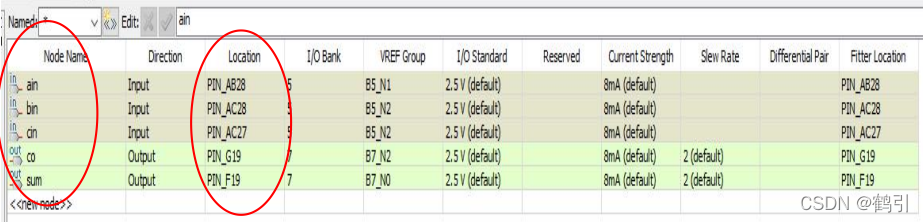

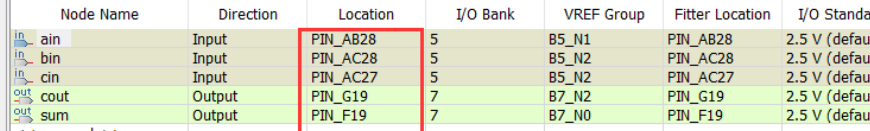

- 配置引脚

3个SW作为输入信号,通过两个LED灯作为输出信号

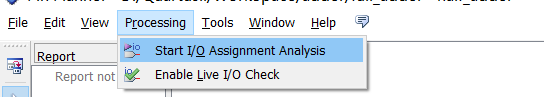

- 引脚配置完成后,需要进行重新编译,才能将引脚绑定在所对应的位置

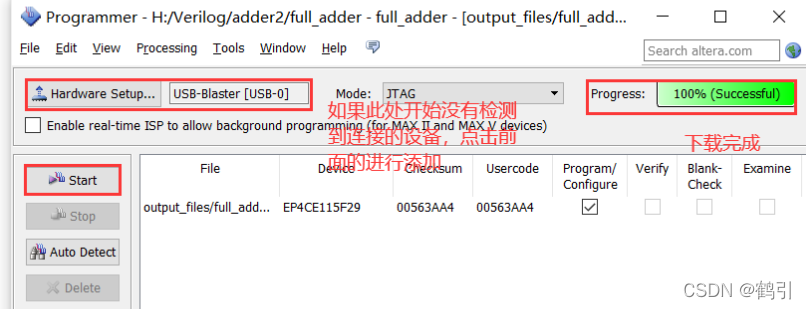

- 下载

- 硬件验证

- 输入信号

1 0 1

进位端为1,和为0

- 输入信号

1 1 1

进位端为1,和为1

- 输入信号

0 0 1

进位端为0,和为1

- 输入信号

2. Verilog测试

- 同理配置引脚同原理图引脚相同

- 执行同操作,实现全加器

- 实物操作与验证

五、总结

- 硬件测试过程中,通过对相应引脚的绑定,测试,到电路测试运行,可以清楚实验并完成全加器的测试

- 通过本次实验中,学习到加法器的实现,可以通过底层逻辑向上逐级实现,通过个人绘制底层半加器,并通过逻辑电路进行组合仿真实现一位全加器,进一步验证全加器功能

2500

2500

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?