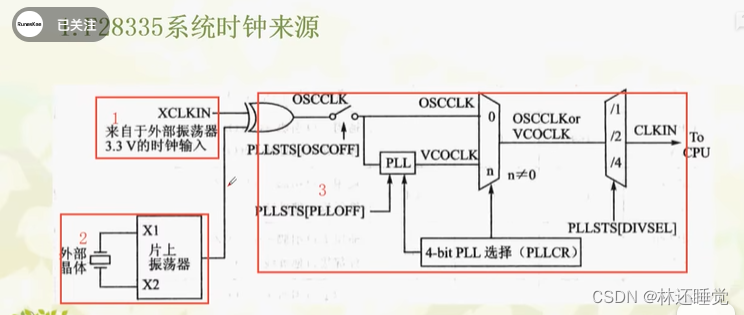

一、F28335的时钟来源

DSP 属于数字信号处理器,也可以说是一种高级单片机

F28335 的时钟源有两种:

1 外部时钟源信号

(1)采用外部振荡器作为时钟源(简称外部时钟),即在 XCLKIN 引脚提供 一定频率的时钟信号,也可以通过复用的 X1 引脚提供,即由其他数字系统或外部振荡器引入。

(2)采用 F28335 内部振荡器作为时钟源(简称内部时钟),在 X1 和 X2 引 脚之间连接一个晶体就可以产生时钟源。

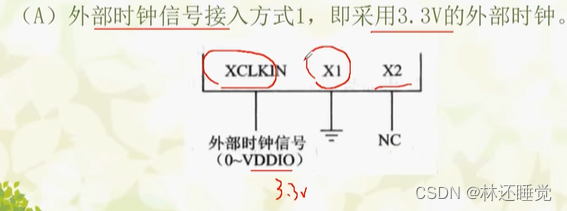

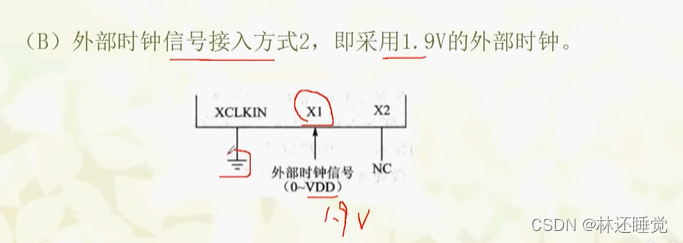

2.外部时钟源信号接入方法有 2 种,分别针对的是电压为 3.3V 的外部时钟和 1.9V 的外部时钟:

(1)外部时钟信号接入方式 1,即采用 3.3V 的外部时钟

3.3V 外部时钟信号直接接入 XCLKIN 引脚,X1 引脚接 GND,X2 引脚悬空,系统内高电平不能超过 VDDIO,即 3.3V。

(2)外部时钟信号接入方式 2,即采用 1.9V 的外部时钟。1.9V 外部时钟信号直接接入 X1 引脚,XCLKIN 引脚接 GND,X2 引脚悬空,系统内高电平不能超过 VDD,即 1.9V。

2.内部时钟源信号

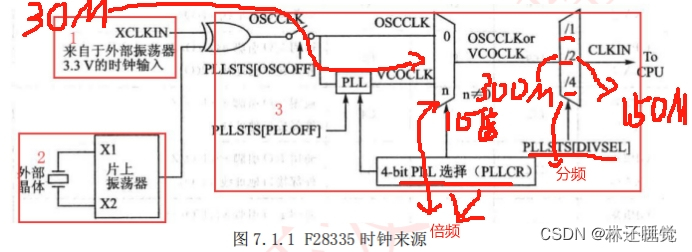

(晶振30MHz)

二、如何设置DSP的工作频率

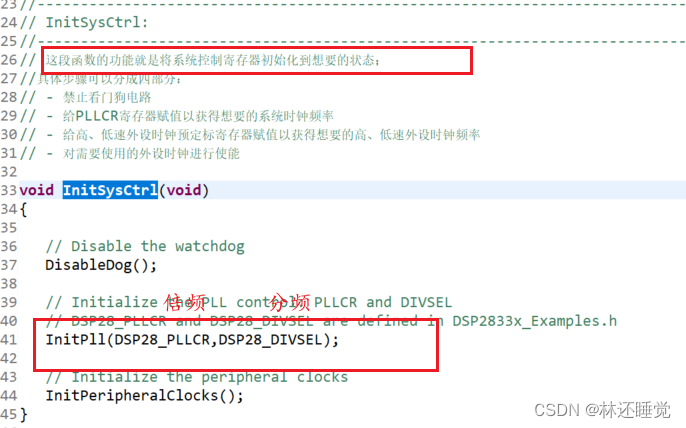

F28335 工作的最高主频是 150MHz,但实际提供的晶振是30MHZ,我们希望 CPU 能工作在最高主频上,这时怎么能让这 30M 转变成 150M供 CPU 工作呢?——>F28335 内部的 PLL 锁相环

倍频+分频

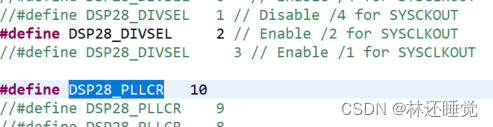

通过寄存器 PLLCTR 来设置倍频数,倍频值最大可设置为 10,通常我们就设置倍频数为 10,这样通过 PLL 后的时钟信号 VCOCLK 即为 300MHZ。因为 F28335 芯片最高工作频率是 150MHZ,所以此时还不能直接 CPU 内核使用,还需要对其分频处理,可通过寄存器 PLLSTS(DIVSEL) 位来设置分频系数,为了使 CPU 工作在最高频率下,通常设置分频系数为 2,即最终时钟信号 CLKIN 为 150MHZ 供给 CPU。

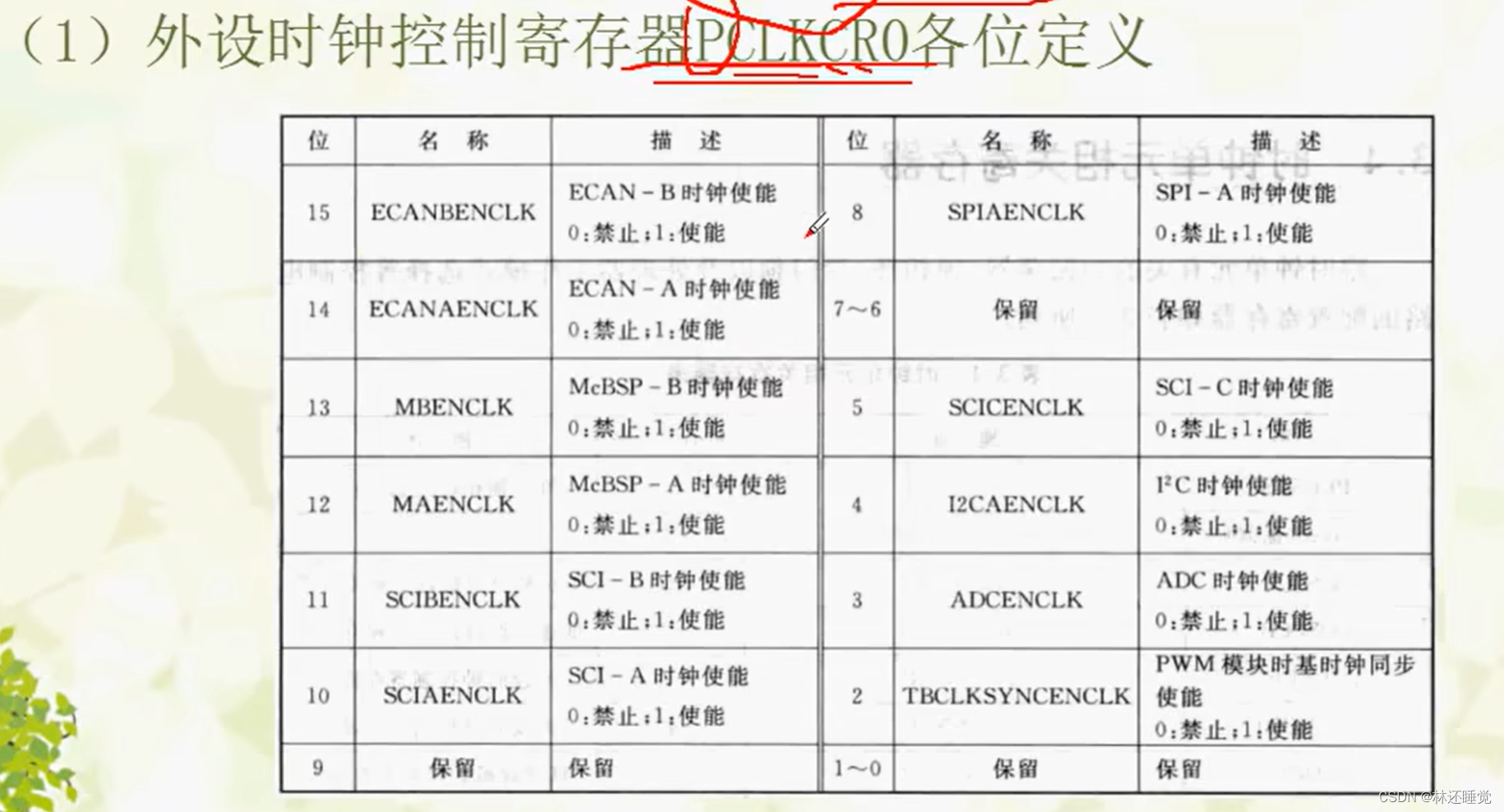

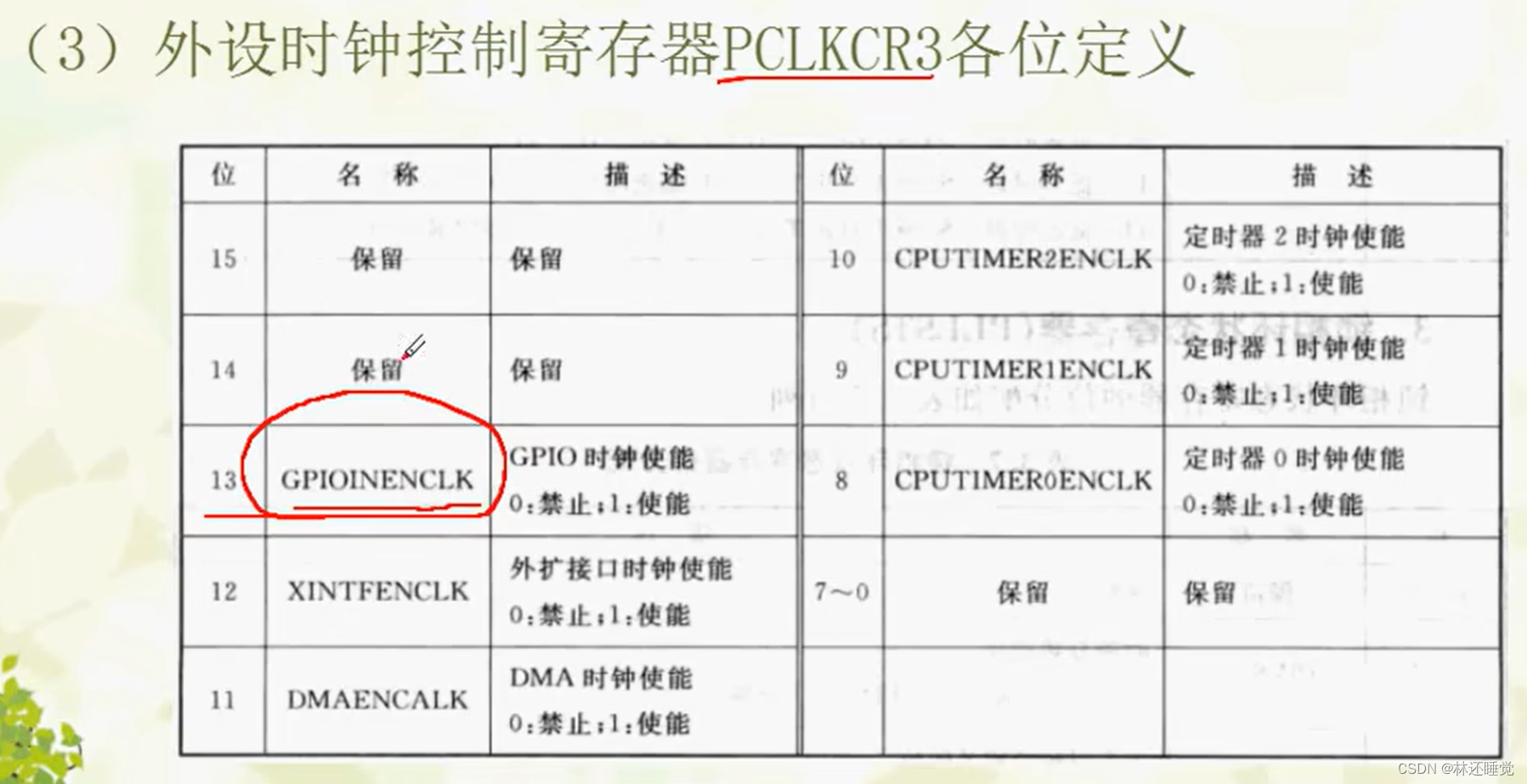

三 外设时钟控制寄存器(16位)

要使用GPIO ,PCLKCR3的第13位必须使能;

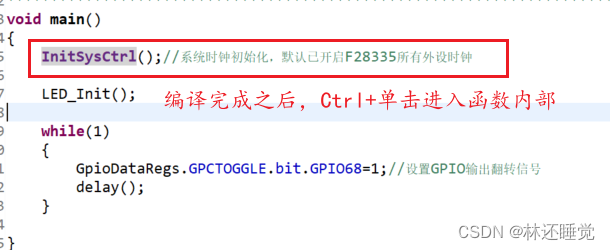

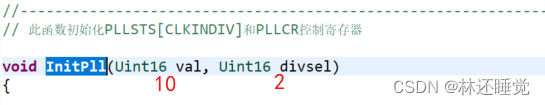

四、自定义系统时钟(以150MHZ为例子)

30X10/2 = 150MHz;

4927

4927

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?