Module addsub √

翻译:

提示:

提示翻译:

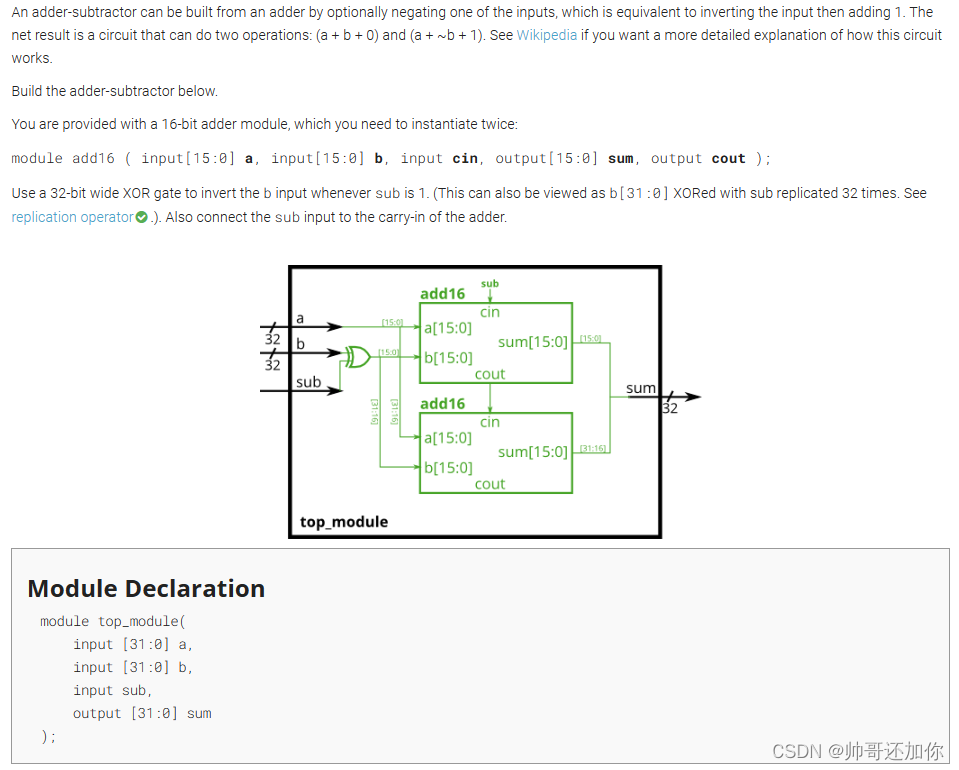

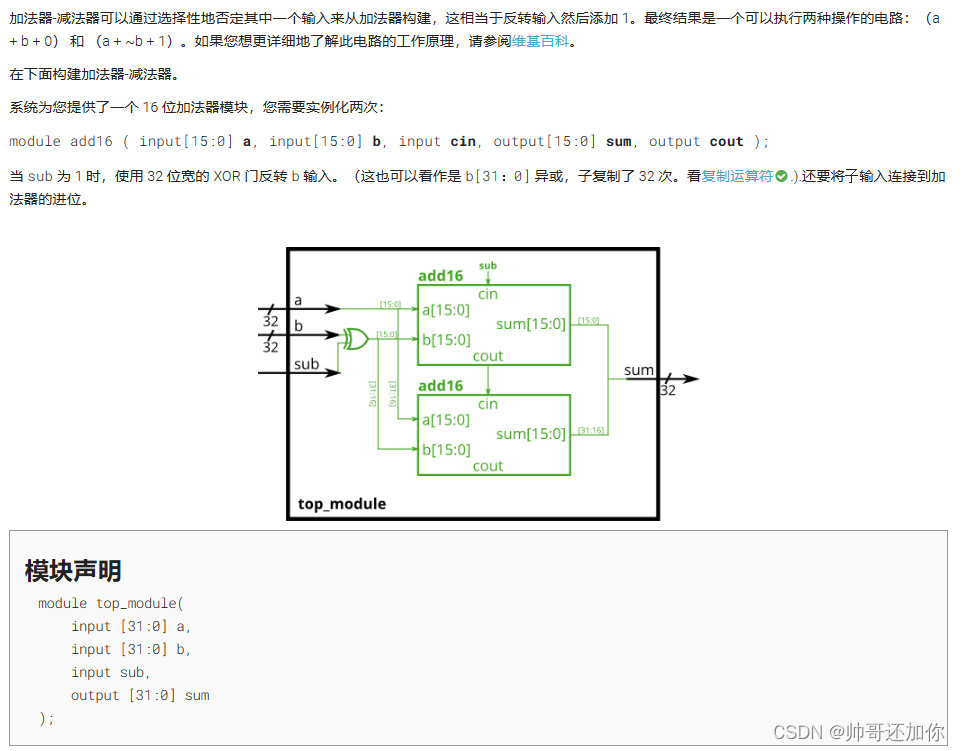

问题要求:用两个16位加法器和一个异或门,构建一个加法-减法器。

当sub为0时,正常实现加法电路:a+b+0

当sub为1时,b与sub异或,使b取反得到~b,实现减法电路:a+(~b)+1

在这简单分析一下,我也捋了一段时间,讲讲自己的看法,有不对的或者补充观点欢迎指出,我也借此学习学习。

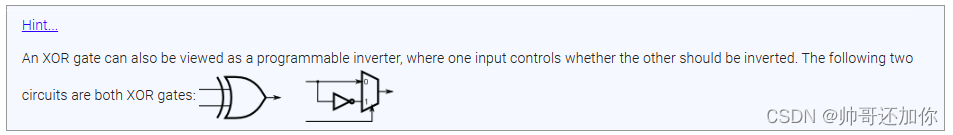

首先我们看看给的提示,提示给到的是异或门(XOR)的一个用法,即可编程的取反器。因为异或的原理是,全同为0,不同为1。我们假设sub为0,当输入0时,相同所以输出为0;当输入为1时,不同所以输出为1。此时输出等于输入,保持不变。假设sub为1,当输入为1时,相同所以输出为0;当输入为0时,不同所以输出为1。此时输出与输入相反,实现了取反的操作。

附带门的运算,可以对照着看看

再看看减法的运算原理,取反+1的操作其实就相当于得到负数的补码,计算机的减法相当于加上其补码。简单讲讲我学习到的观点,首先题目中给的定义是无符号数,所以我们就讲简单的无符号数的看法。

在这里我们就简化16位加法器,用4位的数举例子,比如4位的3,其二进制表示是0011,正数的补码就是他自己,也就是0011,取反得到其反码1100,再+1得到1101,1101正是(-3)的补码,也是13的二进制数。我们再进行3 - 3的运算,那就是 0011 + 1101 = 10000 ,可以看到此时已经得到5位的二进制数,但我们只声明了4位,只取低4位0000,就是0了,第五位的高位就相当于溢出了。

根据我看网上一些比较好理解的说法,就相当于时钟只有12,当我们想从3点清零的时候,可以逆时针转3格(3-3),也可以顺时针转9格(3+9=12,12点也相当于0点)。

理解上面,再看回4位的3-3,0011 + 1101 = 10000,相当于3 + 13 = 16 ,但是4位的定义最大是15 ,所以到了16就相当于归0了,也就反向实现了减法的操作。

理解上面再看这道题就只剩下打代码的问题了

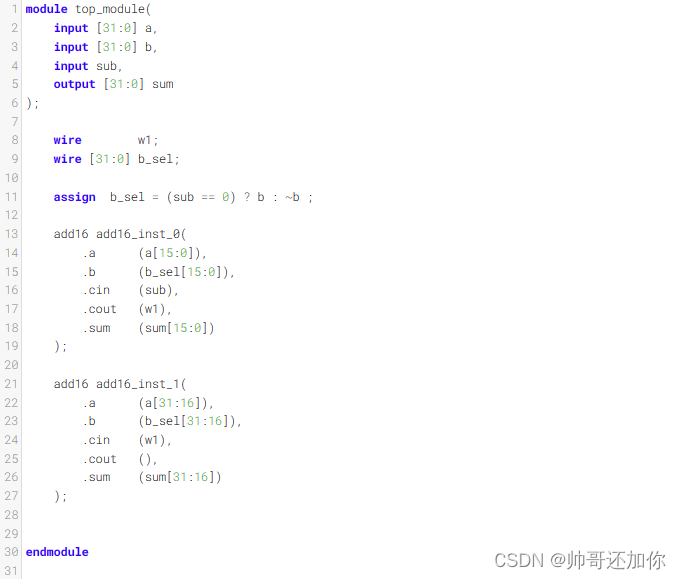

代码如下:

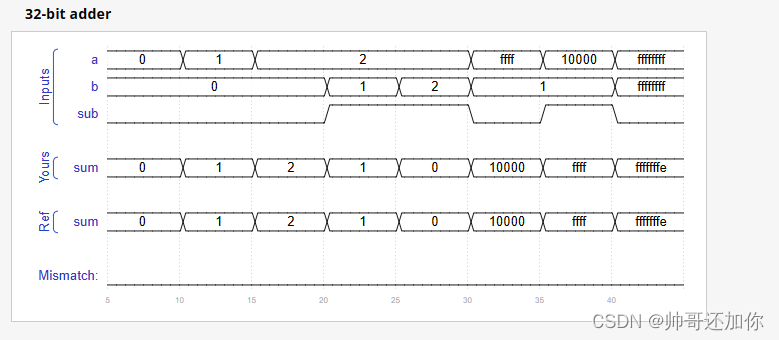

结果如下:

268

268

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?