在本文中,我们将讨论什么是抖动,它的来源,以及它如何影响高速数据转换器的噪声性能。我们还将探究何计算抖动,以及执行怎样的步骤以最大程度地减小噪声性能下降。

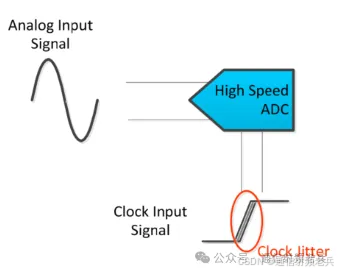

在采样理论中,高速ADC使用外部时钟信号对输入信号进行采样。时钟边沿具有通常称为抖动的时序不确定性,这会降低ADC的噪声性能。

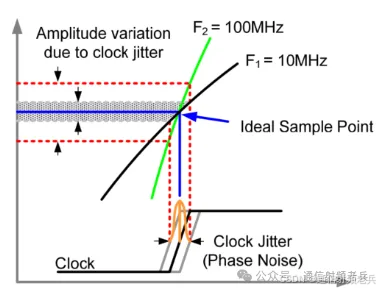

在采样过程中,采样时钟边沿的时序不确定性会导致振幅误差。对于给定量的抖动,误差会随着输入频率的增大而变大。因此,ADC的噪声或SNR性能下降对抖动量和输入信号的频率都很敏感。

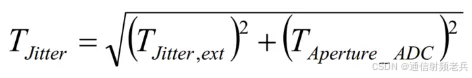

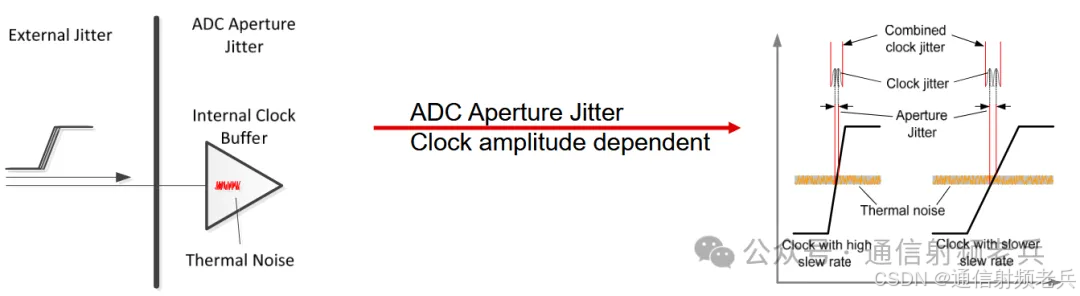

采样时钟抖动包含两个分量,即来自非理想时钟源的外部抖动和内部ADC孔径抖动。ADC孔径抖动主要源自内部时钟缓冲器的热噪声,而孔径抖动通常取决于向ADC提供的时钟信号振幅。需要将外部抖动和内部ADC孔径抖动结合在一起才能确定ADC SNR降低量。

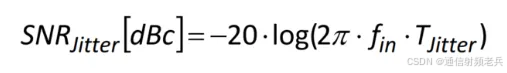

我们通常会使用下面的公式来估算时钟抖动导致的噪声性能下降,即-20*log10[2π*输入频率*抖动]。

正如先前提到的,该公式还证明抖动导致的SNR下降主要取决于输入频率和抖动量。

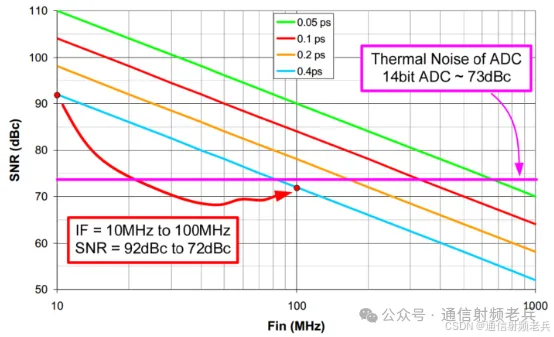

下面的示例图显示了一个具有大约73dB热噪声的14位ADC,即粉色的水平线所示。此外,我们可以看到四条显示抖动导致的SNR降低的迹线,抖动时长分别为50、100、200和400飞秒。例如,对于400飞秒的采样时钟抖动,当输入频率从10Mhz更改为100Nhz时,抖动导致的SNR会降低20dB。

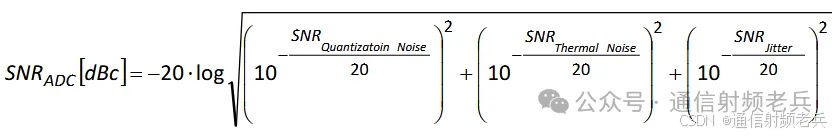

ADC的底噪由三个不同的因素决定。

第一个因素是ADC量化噪声。通常,选择ADC的输出分辨率时应满足以下条件:量化噪声不会使ADC SNR显著降低。在高速ADC中,有效位数或ENOB通常远低于实际的ADC分辨率。

第二个因素是ADC热噪声,而热噪声是ADC的固有的噪声。

第三个因素是抖动导致的恶化。这是时钟边沿时序不确定性导致的噪声增加。

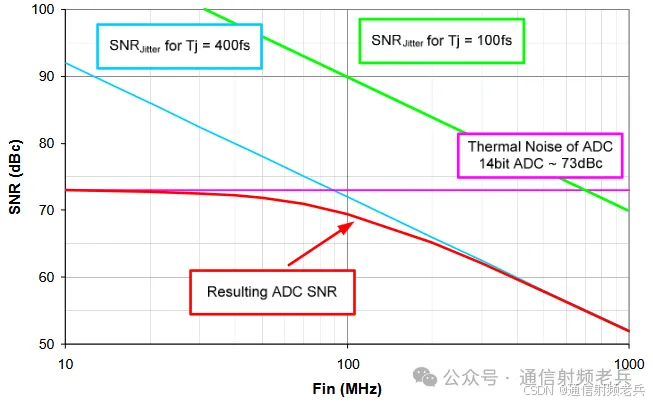

返回到前面有关14位ADC的示例,我们的14位ADC具有大约73dB的热噪声和86d的量化噪声。总采样时钟抖动为400飞秒。

如下图所示,在高达约30Mhz的输入频率下,产生的SNR受约73dB的热噪声限制。86dB的量化大小完全不会影响结果。随着输入频率不断增加,抖动恶化将占据主导地位,并最终完全限制它。如果时钟从400飞秒提高至100飞秒,那么即使在200Mhz的输入频率下,抖动影响一点儿也不明显。

对于射频采样转换器,时钟抖动降级是一个非常重要的考虑因素。

外部时钟信号的抖动可以通过对其相位噪声进行积分来计算。

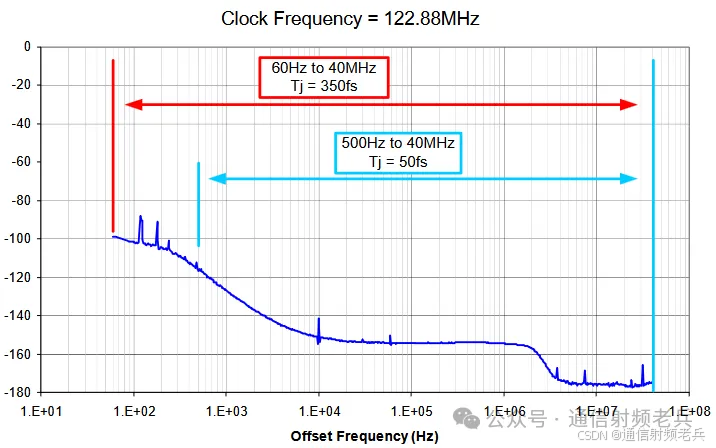

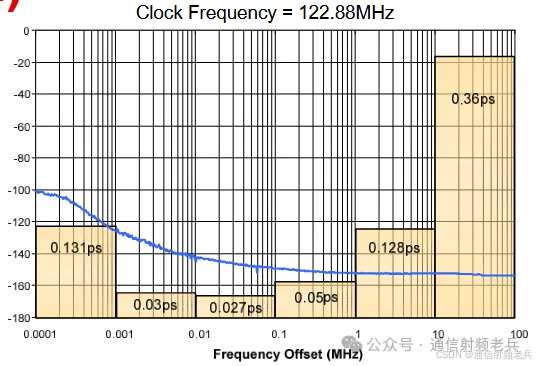

要进行该计算,必须设置积分上限和积分下限。积分下限通常由具体应用场景决定。例如,如果应用于FFT处理,那么下限由FFT bin大小决定,如下图所示。

如果是应用到计算通信指标的场景中,那么下限由频道间隔决定。例如,在GSM通信中,频道间隔是200Khz。任何比这更接近的相位噪声都是不相关的。

下图显示了积分下限可能对总抖动数有显著的影响,因此正确设置积分下限非常重要。

上积分限取决于几个不同的变量。如果在时钟输入端使用带通滤波器,则上限由滤波器的带宽决定。如果时钟输入未经过滤,那么理论上,相位噪声需要积分到时钟频率两倍的偏移频率。但是,内部时钟输入的带宽是有限的,因此积分到时钟频率的两倍是最坏的情况。

从下面的图片中可以看出,外部底噪对总时钟抖动数值有显著贡献。

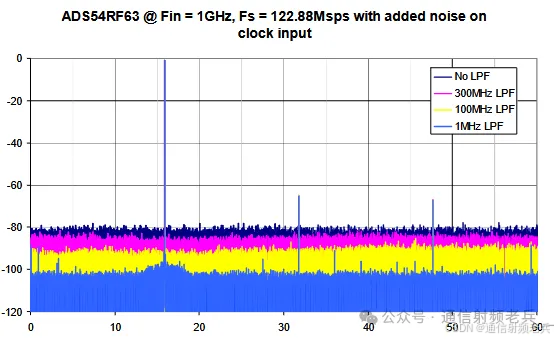

尽可能在ADC时钟输入端使用带通滤波器,以限制噪声流动的恶化。作为一个简单的实验,向ADS 5463的时钟输入端添加了白噪声,然后使用不同的低通滤波器来说明对ADC宽带底噪的影响。

结果如下图所示。不出所料,在未使用滤波器时,底噪恶化程度最为严重。当我把时钟输入端低通滤波器的截止频率从300Mhz降低到1Mhz时,所得的整体底噪恶化程度逐渐改善。

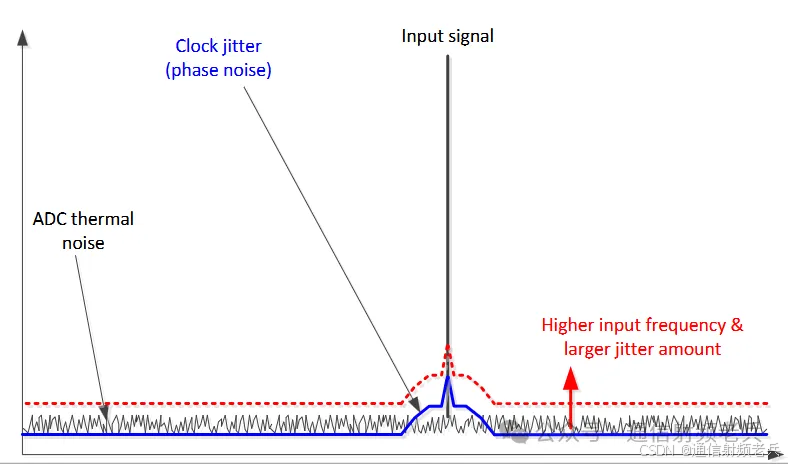

或许,更好地理解时钟抖动导致的底噪恶化的一个方法是从频域的角度来观察它。在采样过程中,时钟信号的相位噪声会被加到输入信号上,但时钟相位噪声的幅度也会根据输入频率与时钟频率的比值,按20倍的对数比例进行缩放,即20*log(Fin/Fs)。

与时域分析类似,如果输入频率增加10倍,那么在将时钟相位噪声加到ADC的热噪声之前,时钟相位噪声的幅度会增加20分贝(dB)。显然,固有的时钟噪声幅度越大(这直接表现为更高的抖动),ADC底噪的恶化程度就越严重。

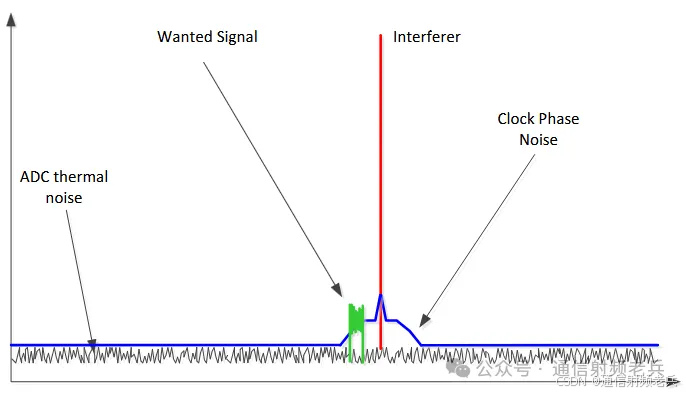

那么,为什么时钟抖动或相位噪声对接收机性能如此关键呢?一个典型的接收机应用场景是阻塞条件,即接收机需要在高功率带内干扰信号存在的情况下检测到一个微弱的期望信号。这个干扰信号位于所需的通带内,因此无法通过滤波去除。由于我们不能使ADC(模数转换器)输入过载或饱和,高功率干扰信号限制了可以对微弱期望信号应用的前端增益量。因此,ADC本身的底噪需要尽可能低。

如下图所示,时钟相位噪声会被调制到全功率干扰信号上,并且这种时钟相位噪声开始直接限制能够检测到的期望信号的最小幅度。随着输入频率或时钟相位噪声的增加,ADC的总底噪也随之增加。这使得检测微弱期望信号变得越来越困难。

那么,为了将时钟噪声对ADC信噪比(SNR)的影响降到最低,我们还可以采取哪些措施呢?有几个不同的选择可供参考。

首先,选择一个抖动或相位噪声足够低的时钟源。

其次,使用低插入损耗的带通滤波器来限制宽带噪声的恶化。

第三,确保ADC时钟输入引脚的时钟幅度足够大,以免恶化ADC孔径抖动。

微信公众号文章:一文讲透时钟抖动Jitter对ADC性能的影响

584

584

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?