Case1,多时钟domians的scan

当两个时钟之间skew 较大的时候,可能会有问题,一般由下列两种情况:

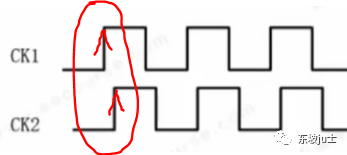

第一种情况,CK2在CK1之前capture,此时,CK2 capture的是前一个寄存器的值,这种情况是没问题的。符合越晚capture的越应该放在前面。

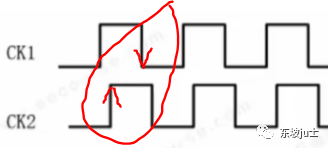

第二种情况,CK1在CK2之前capture,此时CK2 capture 的值可能是下个周期的值,这时候就会导致scan 出错。

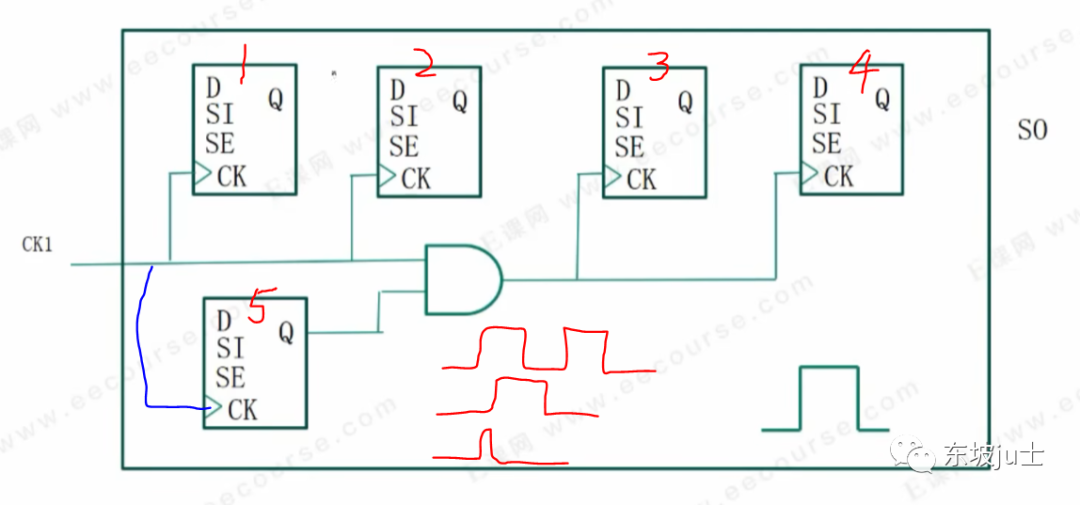

当然,scan 的时候不知道CK1 & CK2 之间的skew 正负关系,所以需要scan的时候去规避出错。处理方式就是在CK1 & CK2 之间插入一个latch up。(注意这个是在scan 的时候插入的,RTL中是不存在的)

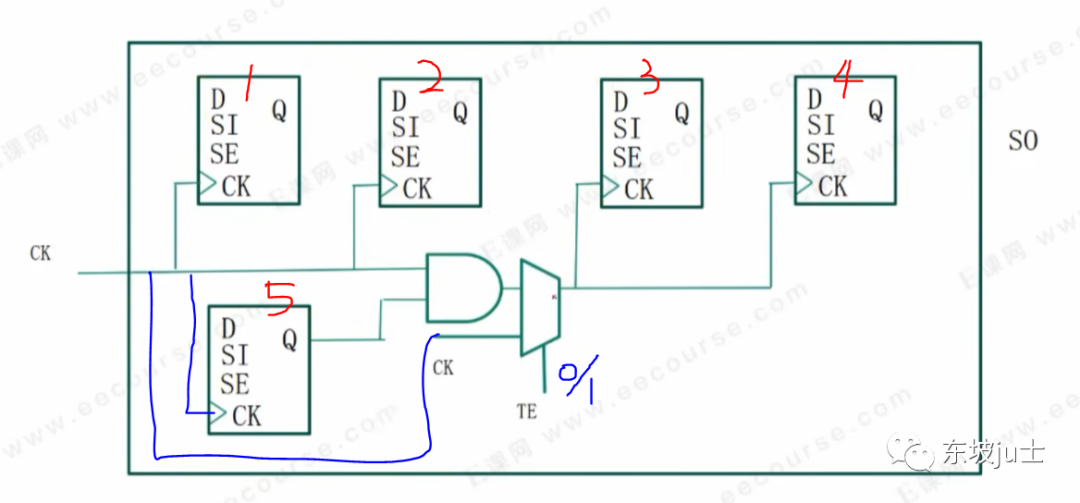

如下图所示,加入latch up 之后,CK2寄存器capture 的还是上一个寄存器的值。满足越晚capture的越应该放在前面。

变成

Case2,clocks 相关的 scan rule

scan 相关的一些signal:

scan 的目标就是把所有的寄存器都在覆盖范围内,即每一个寄存器都穿起来。但有些寄存器时不能直接穿到scan chain 的,所以做scan 之前需要检查寄存器是否能被穿,或者如果不能,应该怎么样修改design,把这部分寄存器穿进来。

能不能做scan 的评价标准就是,scan chain 上的每一级寄存器都能够稳定准确的抓到上一级寄存器的值。下图中,reg3,reg4是不能被穿进来的,因为reg3受到reg5的控制,不能保证每次都能抓到上一个寄存器的值。所以dft /RTL owner 需要对RTL 进行修改(前提是保证func 不被改变)。

下图是dft 修改之后的design:

Case3,Reset 相关的 scan rule

reg1,2,4,5没问题,reg3收到reg5控制,不可控,所以不能满足 scan rule,需要反馈designer 改进。

改进的策略:加一个或门,TIE1,让其一直有效。

遗留问题:

1,除了MUX-D scan cells,列出两种scan cells并简述:

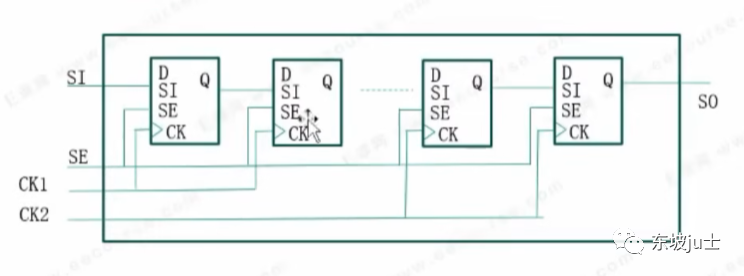

a,双端口扫描单元:为了把扫描时钟和正常时钟、扫描数据和正常触发器输入数据区分开,扫描触发器采用双数据双时钟触发器,有两个数据端口D和SI、两个时钟CLK1和CLK2,两时钟的信号到来后SI端口的信号被捕获。

b,电平敏感扫描设计(LSSD):采用双锁存设计,对瞬态特效,如上升沿下降沿都不敏感,电路结构中包括两个互相连接的电平敏感锁存器,信号有效数据输入D,系统时钟CK,串行扫描输入SI和两个互相不重叠的时钟ck1和ck2,串行扫描输出SO,测试中L1(主)和 L2(副)结构,正常func 状态时只有L2起作用,作用如同触发器。

1669

1669

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?