1, pt fix 后生成的 icctcl,回到 icc source 后,如果需要eco_route,建议先关掉 timing_driven,因为 icc 与 pt 看到的 timing 情况一般都有 mismatch,所以如果开了 timing_driven,可能在 icc eco_route 后,在 pt 中看到新的 violation。关闭 timing_driven 方法:

set_route_zrt_detail_options -timing_driven false

route_zrt_eco -reroute modified_nets_first_then_others -max_detail_route_iterations 5

2, 绕线完成后首先要检查是否有short,有较多short 就说明没有绕通,没必要往下做了,先回头找原因。CalibreDRC 不会去检查short,DRC主要检查绕线spacing 、 min area、density;LVS 如果出问题,一般主要是power 或者short,先确认ICC error browser 中是否有short存在。

3. 从 designer 那边拿到的sdc,需要先修改掉一些内容,主要包括:set_wire_load,set_voltage,set_clock_uncertainty,set_operating_condition 等等,因为这些设定只是针对一个scenario条件的,而后端一般会用到多个scenario,在 set_mcmm 步骤会针对不同 scenario 做不同的设定,所以需要在 sdc 中删去这些设定。

4. 完成place 阶段后,需要检查几个指标:timing,utilization, cell density, route congestion。其中 cell density 可直接查看 density map,而 congestion 可用 report_congestion 报出横纵两个方向的routing overflow。查看这些参数的目的就是提前预估当前的 floorplan,chip size 是否合理,能否做的出来。

5. 在做 PNS 时,如果发现执行命令却没有任何结果,首先考虑是不是没有 pg nets, nets 属性是不是 power/ground(方法:get_nets DVDD 如果可以抓到,就是 signal,如果不能抓到,再用 get_nets -all DVDD ,如果可以抓到,就是pg net了),然后检查有没有 derive_pg_connection ( 方法:直接看 std cell 的pg pin 的owner net,如果没有net,就是没有做 derive_pg ) ,总之就是一定要确保有pg nets,并且与 std cell pg pin 在逻辑上有连接,这样才能接着去做物理连接。物理连接连不上,第一反应就要想到可能是逻辑连接没连上。

6. 修timing 时,如果data已经没什么可修了,那就要考虑改 tree,改 tree 需要注意先看看launch clock 和 capture clock 的 last common pin,只能改 last common pin 之后的那一段tree,因为前面的 tree 都是 common path ,改了会同时影响 launch 和 capture,等于没修。查看 last common pin 可以用 PT report_timing,ICC 好像没法报出来。

7. 绕线的 user_route 属性要慎用,如果某段绕线的属性是 user_route,那么在 route 过程中,ICC 就不会改动这段绕线,并且会将对应net 的绕线连接到这段上,可能会浪费绕线资源。

8. LVS 简单来说就是对比 layout与 schematic 是否一致,即 Layout VS Schematic,这里的 layout 就是写出来 GDS, schematic 就是写出来的 pg.v ,二者做对比,可以查出物理版图和逻辑电路之间的差别,比如如果版图有 short,就会报出来,最好是在 error browser 中把所有short 清干净再去跑 lvs ,否则 lvs rpt 会非常大,无法查看。而 gds 与 netlist 无法直接对比,所以将两者都转成 spice 文件,第一步先用 v2lvs 工具将 pg netlist 转换成 spice,注意需要include 相应的库spice ,比如 std cell 库的 spice文件(有的库可能叫 cdl文件);第二步是要准备好merge 后的gds,一般从ICC写出0层的gds,然后带上相应的 std 库和 macro 库做merge,得到完整版的gds;这样就可以用 calibre 读取这两份data做 lvs 比对了。

9. 关于delay cell,修hold 时,可能会用到delay cell,delay cell 的特点是 delay 大但是驱动能力小,容易在下一级的输入端出现 transition 问题,所以加 delay cell 时注意其位置需要靠近下一级的输入端,最好不要放在绕线的中点,更不要放在上一级的输出端附近。

10. 手动修改部分绕线后,建议执行 check_lvs 确认是否改出 short 或者 open,如果有,可以打开 error browser,查看 check_lvs 的结果,定位出 short / open 坐标位置。有时候接手别人的data,最好也先执行 check_lvs 、check_routes 确认当前状况。注意:check_lvs 仅仅查看绕线 metal 和 cell pin,不去查看 cell 内部的 metal,因此 check_lvs 报出的 short 可能不全,而 check_routes 才可以看到所有的 short, 包括 cell 内部 metal 与 route 的short,但是 check_routes 一般不看 open,所以推荐的流程是先用 check_lvs 确认没有 open 和 short,再用 check_routes 确认没有short。

11. 如果绕线资源比较紧张,可以考虑禁用部分 high pin-density cell,比如大小为 x1 和 x2 的 AO, AOI 等cell,这种 size 较小、pin 密度又高的 cell 很容易引起绕线问题 。

12. create_clock 时,不要定义在 hierarchical pin 上,否则 cts 时会忽略这个 clock ,详见 CTS-811 Warning,解法是将其定义到实际存在的 pin 或者 port 上。

13. ICC2在运行过程中,Check for TCL_ERROR error conditions with the Tcl catch command on the commands that might generate errors.

如果想遇错不停,Set the sh_continue_on_error variable to true in the script file.

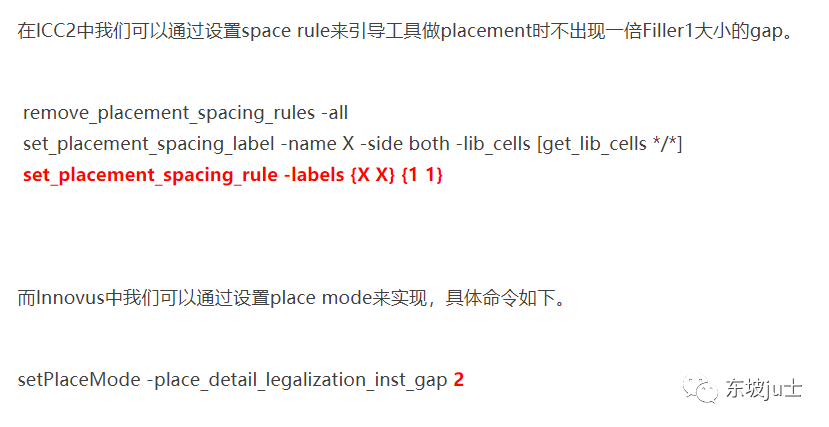

14. ICC2和Innovus中如何避免出现Filler1大小的缝隙?

1468

1468

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?