(1)Vivado基本界面介绍:

Open elaborated design:打开详尽的设计,即显示工程文档,包括设计文件,仿真文件,约束文件(主要为管脚约束和时序约束)。

Synthesis:进行综合。

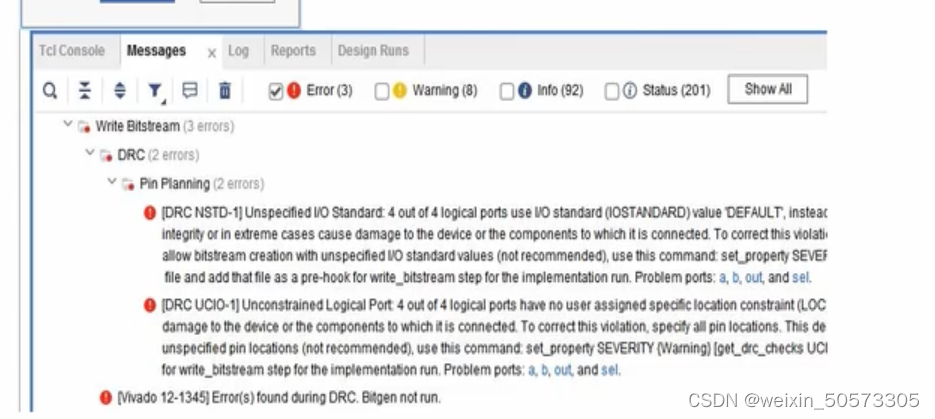

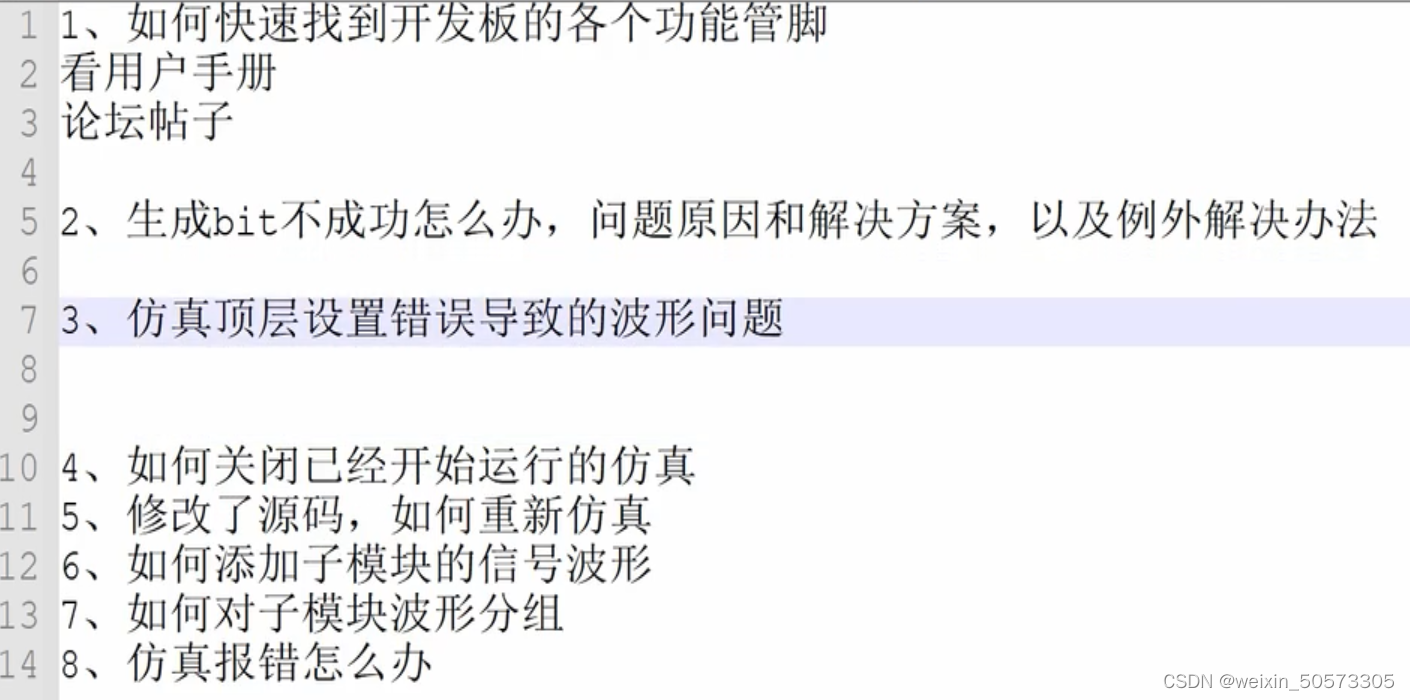

(2)出现编译报错:

第一种 错误说明管脚电平未指定(通常为3.3V),第二种错误说明管脚未与芯片IO口绑定。

这两种报错可以通过语句将其降级为警告,如图所示语句:

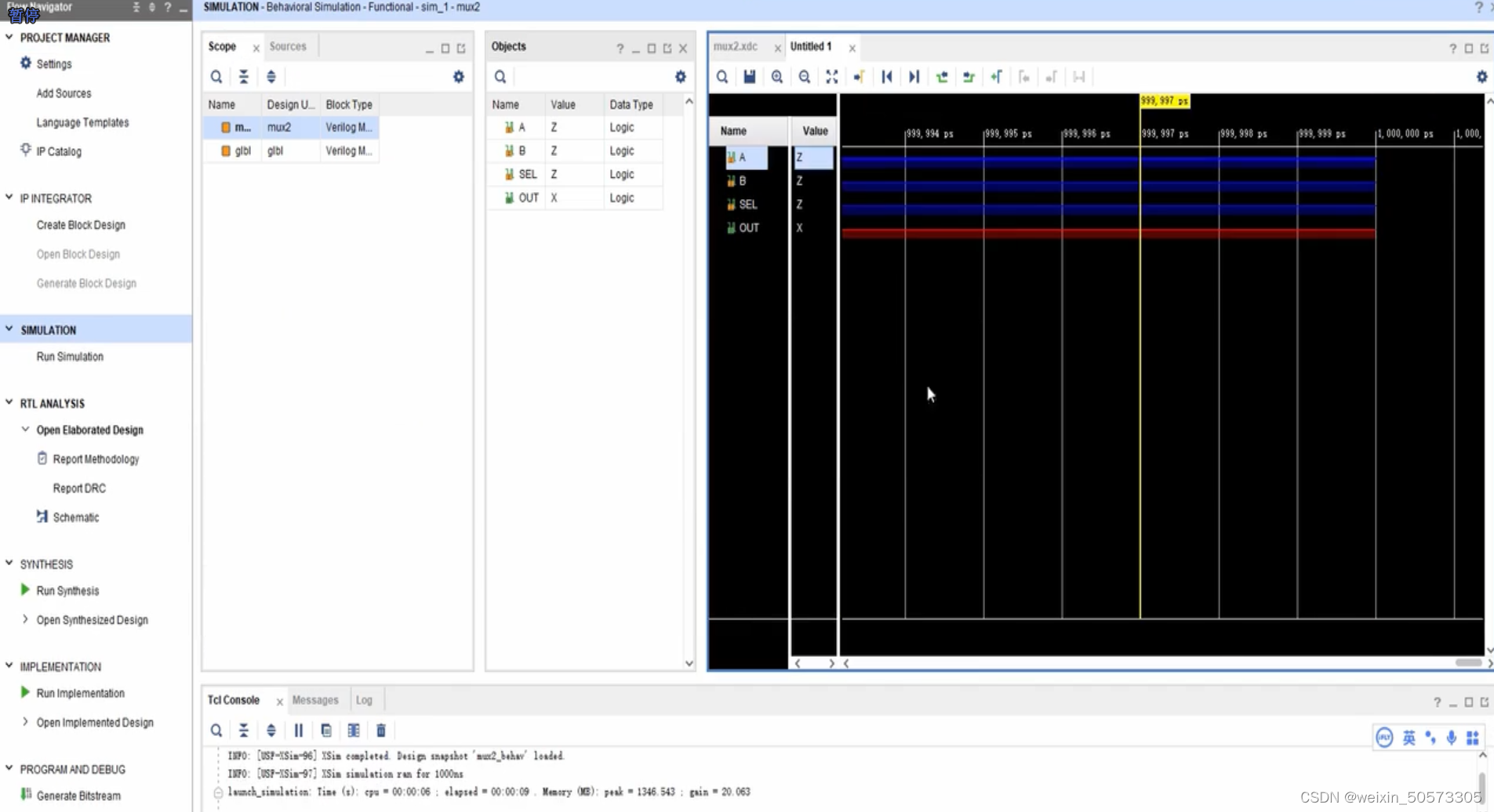

(3)仿真波形出现错误:

此错误是由仿真的时候顶层模块设置错误导致的,仿真的顶层模块应该是testbench模块,解决此种错误只需要将testbench设置为顶层模块即可。

(4)关闭仿真:

右键Simulation选择close

(5)修改了源代码之后重新仿真:

右键Simulation选择relaunch simulation(重新启动仿真),点restart-run是不行的,这个只是再仿真一次,还是修改代码前的结果。

(6)仿真时添加子模块信号并且分组:

Scope窗口选中子模块信号然后右键添加;分组也同理,选中后右键选择New group

(7)仿真报错怎么办:

找错误然后修改,看他给出的建议,建议你从哪个窗口or文件去找错误,则去哪里找错误。

(8)device窗口和Schematic窗口:

Schematic是硬件电路图(综合、实现之后的电路图更加详细),组成的基本单元是FPGA上的具体的硬件资源,由查找表,触发器和CarryLogic(进位)资源

device是该型号的FPGA的具体的硬件资源(可编程逻辑资源)图,甚至你所占用的逻辑资源的具体位置or(pin)引脚的具体名称都可以在这里看到,是所映射的使用到的具体的FPGA资源位置以及数量,FPGA的可配置资源CLB由Slice组成...后面补充一些FPGA的概念!!

(9)FPGA的可配置资源CLB,Slice:

CLB可配置逻辑块是指实现各种逻辑功能的电路,是xilinx基本逻辑单元。

在Xilinx FPGA中,每个可配置逻辑块包含2个Slice。

每个Slice 包含查找表、寄存器、进位链和多个多数选择器构成。

而Slice又有两种不同的逻辑片:SLICEM和SLICEL。SLICEM有多功能的LUT,可配置成移位寄存器,或者ROM和RAM。

逻辑片中的每个寄存器可以配置为锁存器使用。

1)一个CLB 等于2个Slice

2)一个Slice等于4个6输入LUT+8个触发器(flip-flop)+算数运算逻辑 ——每个Slice的4个触发器(虽然有8个flip-flop,但是每个LUT分配一个flip-flop)可以配置成锁存器,这样会有4个触发器(flip-flop)未被使用。

3)这里还有一点需要特别注意的,XILINX FPGA 的slice还不都是长一样的,FPGA中三分之二的slice是SLICEL而剩余的是SLICEM。

注意:

1)SLICEL 没有distributed RAM 和 shift registers

2)SLICEM是可以当作分布式64bit-RAM或者32bit的移位寄存器或者2个16bit移位寄存器。通过VIVADO软件或者原语的调用可以利用这些逻辑算数功能和存储功能。

所有slice均使用上面的元素来提供逻辑、算术和ROM功能。 此外某些slice还支持两个附加功能:使用分布式RAM存储数据和使用32位寄存器移位数据。 支持这些附加功能的slice称为SLICEM; 其他称为SLICEL。 SLICEM(下图所示)表示在所有slice中找到的元素和连接的超集。

参考文献:FPGA CLB单元 汇总 (CLB、LUT、存储单元

待补充.....

5592

5592

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?