目录

信号通过元件都会有延迟,延迟时间的计算是逻辑仿真的重要功能。考虑延迟信息得到的仿真输出波形可以更精确地反映实际电路的情况。针对元件的延时,人们根据需要建立了一些用的延时模型,这些模型均有自己的使用特点。

零延迟模型把元件抽象为没有延时的理想元件,常用于简单电路的设计及计算,单位延迟横型默认所有元件延迟时间相同,均为 1个时间单位;标准延迟模型对每种元件设定一个标准延迟时间,不考虑元件的离散性;上升下降延迟模型分别考虑信号在正跳变和负跳变时的不同征迟时间;模糊延迟模型则给出元件延时的范围,即延时的最大值和最小值。

在FPGA/CPLD 设计过程中,源设计文件一般不需要建立延时模型。因为源设计采用VHDL高级行为描述,即使采用延时模型,也与经 FPGA/CPLD 适配器布线后的结果有很大差异。但是,在 VHDL 中有两种延时模型能用于行为仿真建模:惯性延时和传输延时。需要注意的是,这两种延时模型仅用于仿真,不能被综合。

1,惯性延时

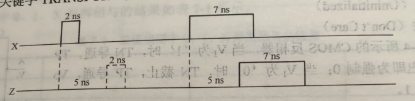

惯性延时也称为固有延时,是任何电子器件都存在的一种延时特性。物理机制是器件的电容分布效应。若信号的脉宽小于器件的惯性延时,器件对输入的信号不做任何反应。为了使器件对输入信号的变化产生响应,就必须使信号的脉宽大于固有延时。VHDL 中将惯性延时默认为一个无穷小量。但由于不同物理特性器件的惯性延时是不同的,为了在行为仿真中更加逼真地模仿电路的这种延时特性,VHDL 提供了有关的语句:

Z<=X after 5ns;-惯性延时

在 VHDL 语句中如果不特别说明,产生的延时一定是惯性延时。上述语句惯性延时默认就是平时使用的情况:

Z<= X;

--惯性延时默认

进VHDL-延迟模型-惯性延迟与传输延迟进VHDL-延迟模型-惯性延迟与传输延迟进VHDL-延迟模型-惯性延迟与传输延迟进VHDL-延迟模型-惯性延迟与传输延迟

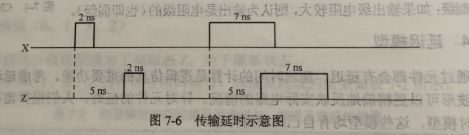

2,传输延时

与惯性延时不同,传输延时并不考虑信号的持续时间,它仅仅对信号延迟一个时间段。任何宽度的输入信号在经过传输延时后,将完全复现在输出端。VHDL 中,传输延时表示连线延时,它对延时器件、PCB 板上的连线延时和 ASIC 上的通道延时的建模特别有用。VHDL中的传输延时由关键字TRANSPORT 引导:

Z<=TRANSPORTX after 5ns;

注意:虽然产生两种延时的物理机制不同,但在行为仿真中,传输延时与惯性延时造成的延时效应是一致的。在综合过程中,综合器将忽略 after 后面所有的延时设置。

进VHDL-延迟模型-惯性延迟与传输延迟进VHDL-延迟模型-惯性延迟与传输延迟进VHDL-延迟模型-惯性延迟与传输延迟进VHDL-延迟模型-惯性延迟与传输延迟

进VHDL-延迟模型-惯性延迟与传输延迟进VHDL-延迟模型-惯性延迟与传输延迟进VHDL-延迟模型-惯性延迟与传输延迟进VHDL-延迟模型-惯性延迟与传输延迟

进VHDL-延迟模型-惯性延迟与传输延迟进VHDL-延迟模型-惯性延迟与传输延迟进VHDL-延迟模型-惯性延迟与传输延迟进VHDL-延迟模型-惯性延迟与传输延迟

910

910

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?