最近在芯片测试公司进行学习,指导资料是《数字半导体测试基础》和加速科技出版的《集成电路测试指南》。对于刚入门芯片测试,很多全新的内容和专业词汇让新人一时间找不到进门的路,且上网能找到这一块内容的解答较少,时常看书处于抓不到重点走马观花的苦恼状态。该篇博客是为了记录这两周学习到的内容,目的是脱离书本回想知识点,尝试理清一下知识脉络。欢迎各位一起在学习的小伙伴和资深大佬莅临斧正!

一、半导体测试基础

1、常见术语

| 晶粒(Die):晶圆上的单个芯片单元,在封装之前的状态。 |

| 来料检验(Incoming Quality Assurance,IQA) |

| 可测性设计(Design for Test,DFT) |

| 被测器件(Device Under Test,DUT) |

| 分Bin(Binning):测试程序按照器件的表现性能做分类。 |

| 引脚(pin),引脚电路(PE) |

| 系统供电单元(System Power Supply,SPS) |

| 输入低电平(VIL),输入高电平(VIH),输出低电平(VOL),输出高电平(VOH) |

| 精密测量单元(PMU) |

| 参考电压源(Reference Voltage Source,RVS) |

| 开始测试(Start of Test,SOT) |

| 自动测试设备(Automatic Test Equipment,ATE) |

| 微控制器(Mirco Controller Unit,MCU) |

| 模数转换器(Analog to Digital Converter,ADC或A/D),数模转换器(DAC) |

| 数字信号处理(Digital Signal Process,DSP) |

| 任意波形发生器(Arbitraty Waveform Generator,AWG):能够产生各种复杂波形。 |

| 系统级封装(System in Package,SIP) |

| 射频功率放大器(Power Amplifier,PA) |

| 负载板(Load Board,LB):专门设计的接口板,用于确保芯片在封装前经过精确测试。 |

| 系统主控板(System Control Board,SCB) |

| 模拟前端(Analog Front End,AFE) |

| 通用输入输出(General Purpose Input Output,GPIO) |

| PAD:芯片上一个小的金属区域。 |

| IDD:静态电流测试,测量芯片在不同工作状态下的功耗。 |

| 开短路测试(Open/Short Test) |

| 芯片测试座(Socket) |

| 器件接口板(Device Interface Board,DIB) |

| Pattern:一组用于测试IC的输入信号序列或者向量。 |

| 周期(Cycle):反映Pattern运行的速度。 |

| 沿(Edge):数据出现或改变的时刻点。 |

| 脉冲宽度(Pulse Width):高电平或低电平信号持续的时间。 |

| 差分非线性误差(Different Nonlinearity,DNL),积分非线性误差(INL) |

| 最小有效位(Least Significant Bit,LSB):连续输入的两个数字代码产生的电压差。 |

| 信噪比(Signal Noise Ratio,SNR) |

2、器件介绍

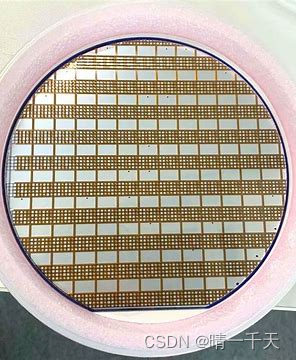

2.1、晶圆

晶圆(Wafer)是由单晶硅制成的半导体晶体圆形片,经过处理后,上面可以形成数千个微小的晶粒(Die)。一个晶圆在其顶端会有一个平的缺口,这跟芯片缺口一样,是为了生产和测试时确定方向用的。晶圆制造完成后,需要对每一块晶粒进行测试,以确保其上的每一个Die满足制造书的规范。

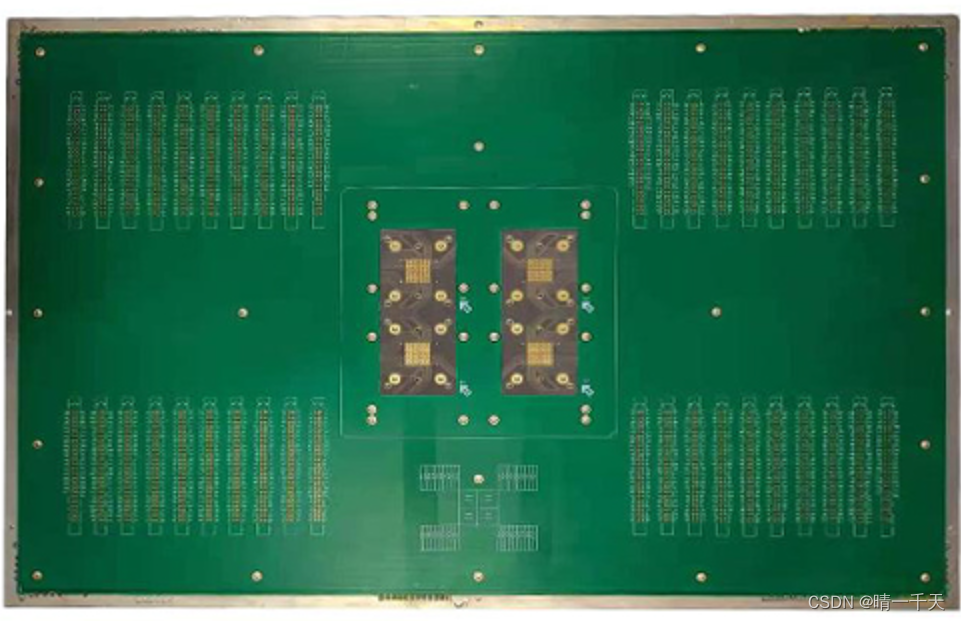

2.2、测试负载板(LoadBoard)和芯片测试座(Socket)

测试负载板是连接测试设备的测试头和待测器件的电路接口,它的布线用于传输测试机发给待测芯片引脚的信号。下图中一排一排的就是排线插口,可以使用排线连接芯片进行信号传输。

芯片测试座类似于可拆卸的芯片槽,它会让芯片测试更加方便,不用多次焊接和取下芯片,避免了触点损坏。芯片装在Socket卡槽内,然后将Socket固定在LoadBoard上(上图中间的位置)。使用Socket连接可以优化信号传输路径,减少信号干扰,对于高速传输的测试环境是更好的选择。

2.3、探针卡(ProbeCard)

探针卡是在晶圆测试中连接测试设备和待测芯片(Die)的工具。它通过微小的探针与晶圆上的每个晶粒接触,以进行电气测试。

探针卡类型(下表来自@你骄傲的飞远)

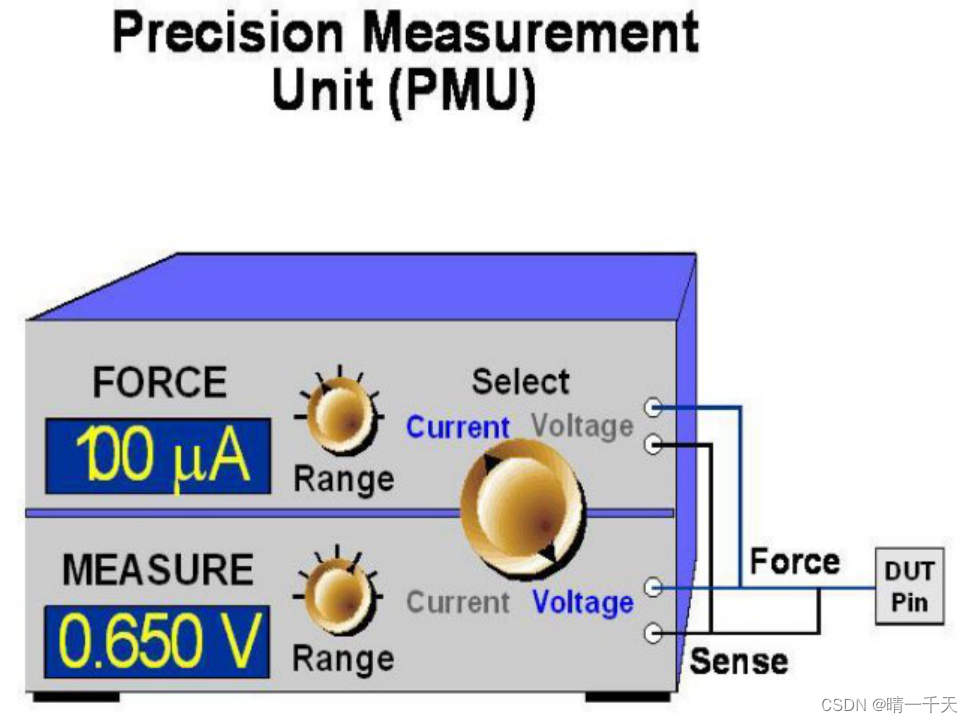

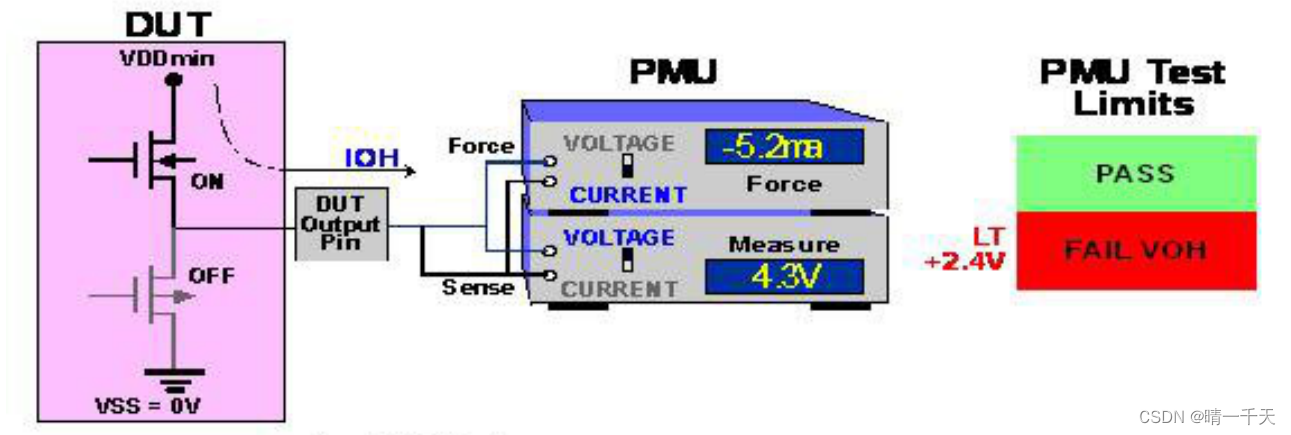

2.4、精密测量单元(Precision Measurement Unit)

PMU用于DC参数的精确测试。有两种模式设置,可以加流测压即驱动电流流经器件后测量器件电压;还可以加压测流即为器件加上电压后测量其产生的电流。PMU的驱动和测量量程在编写程序时就应该进行设定,合适的量程设置能使测量结果更加准确,驱动和测量的的量程范围取决于PMU的最大驱动和测量能力。PMU有上限和下限两个可编程的边界,当测量超过这个界限时会被判定为不良品,这两个界限可单独使用。在进行测试之前,还需要对PMU进行钳位电流和钳位电压设置,以保护测试的操作人员、测试硬件和测试电路。钳制的边界必须大于测试边界,才能正确识别到有缺陷的产品。

3、ATE测试

随着集成电路的复杂度越来越高,测试的复杂度也随之增长,器件的测试费用占到了芯片成本的大部分。大规模集成电路需要数次测试,实现复杂的测试,就需要自动测试设备ATE来完成。ATE是一种通过计算机控制进行批量器件、电路板和系统等自动化测试的设备。

3.1、CP测试

CP测试通常是指晶圆探针测试(Chip Probe Test),针对的是未切割的晶圆,因此也称晶圆测试。在晶圆制作完成后,晶圆上的每一个晶粒都要进行性能测试,确保每一个芯片只有合格了才能进入封装阶段。在测试中,使用探针卡接触晶圆上的测试焊盘,一次可以测试单个或多个晶粒。CP测试后会生成两种输出,一种是测试数据,包含每个Die的位置信息、测试项和结果以及分Bin信息;另一种是分Bin显示的晶圆图。

3.2、FT测试

在一个合格的Die封装之后需要进行性能再次测试,确保每个芯片满足设计规范和质量要求,该过程称为Final Test。FT测试用弹簧针(Pogo pin)连接集成电路(IC)外引脚进行测试。

CP测试是把坏的Die挑出来,测试晶圆的良率,减少后续封装和测试的成本;FT测试是把坏的芯片挑出来,测试封装的良率。ATE测试机对硬件进行测试,性能指标达标的器件pass,否则就是fail。fail的器件未达到设计的要求,不能用于最终产品上,但测试机会根据硬件在测试中的性能表现将其分类,这个过程称作“分Bin”。分Bin有“杀鸡焉用牛刀”的意味在,fail的硬件可能不能用在当前的产品中,但对于其他对性能要求不高的产品还是可以使用的。分Bin后的硬件还可以进行缺陷分析,回溯到设计进行设计改良。

二、直流测试流程

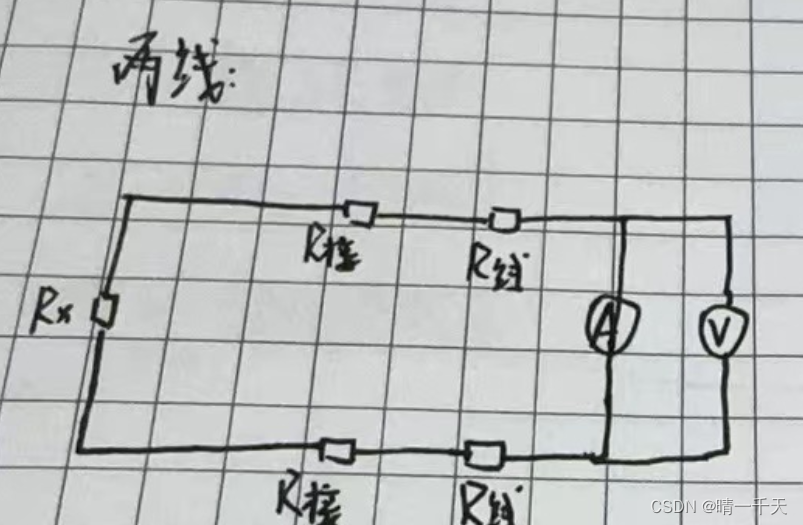

1、开尔文测试

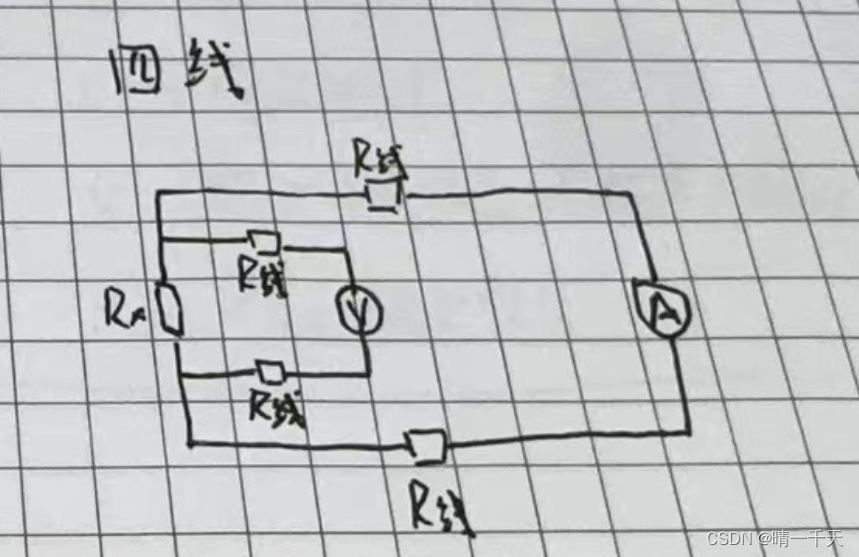

开尔文测试是一种测量电阻的技术,相比于两线测量电阻的方法,使用单独的电流和电压进行测试会更加准确。传统的两线方式,比如使用万用表两只表笔直接接在电阻上测量,万用表是给固定电流流经电阻,然后测量电压后通过计算得到电阻的。但是万用表接线本身是有微小电阻的,在电路中会与被测电阻分压,如果被测电阻阻值很大,这点微小电阻产生的分压还在可接受的误差范围内;如果被测电阻阻值本就很微小,接线产生的电阻就会增大电阻被测阻值,超过误差范围。

四线测试能减轻接线电阻的误差影响。对于电流测量单元,保证给的电流源是稳定不变的,接线电阻与被测电阻串联,电流不会受到分压影响;对于电压测量单元,接入的电压表是高阻值的,该回路产生的电流是微弱的,所以在接线上产生的压降较小。用测出来的电压/电流就可以得到较为精确的电阻值。

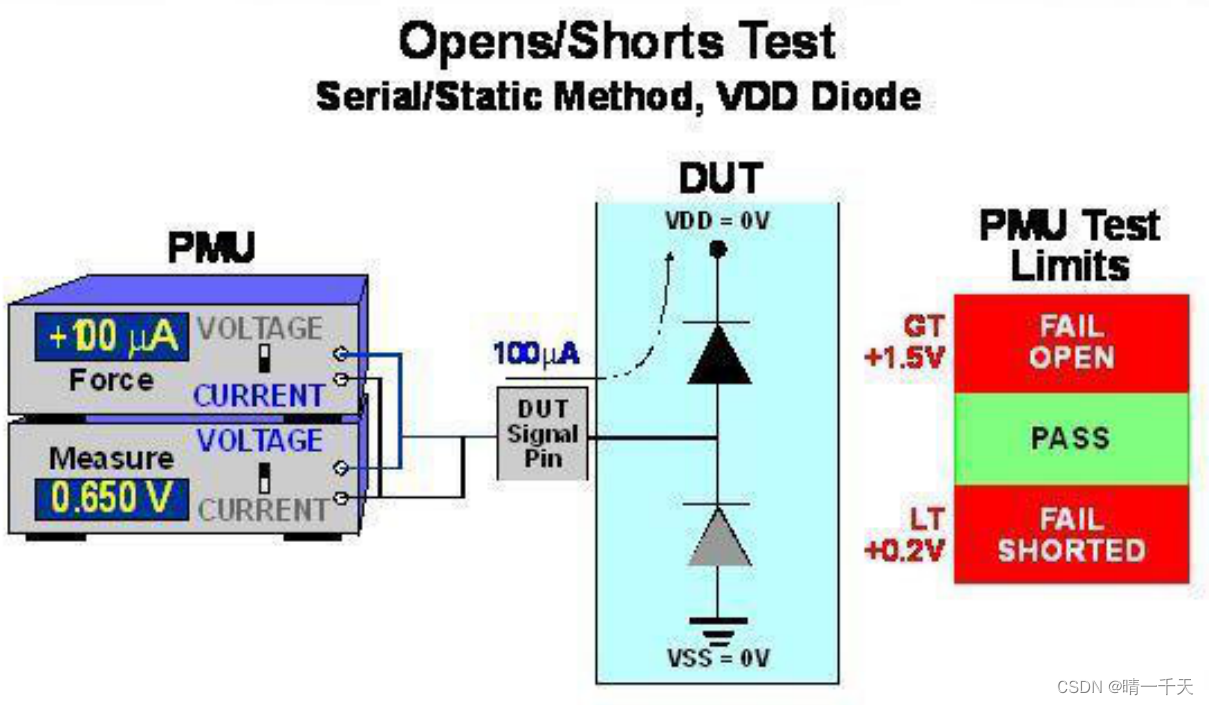

2、开短路测试(Open/Short Test)

OS测试是为了测试DUT与ATE电气连接是否正常,同时也可以检测DUT自身是否出现开短路现象。测试的成本高低与测试时间相关,使用OS测试可以快速剔除有问题的芯片,减少了后续测试的时间。OS测试的核心在于测量产生的压降,OS的测试流程是:检查电气正常连接-->电源引脚和其他引脚接地-->被测引脚使用PMU施加电流-->测量产生的压降(压降范围在0.2--1.5,小于0.2判定为短路,大于1.5判定为开路)。

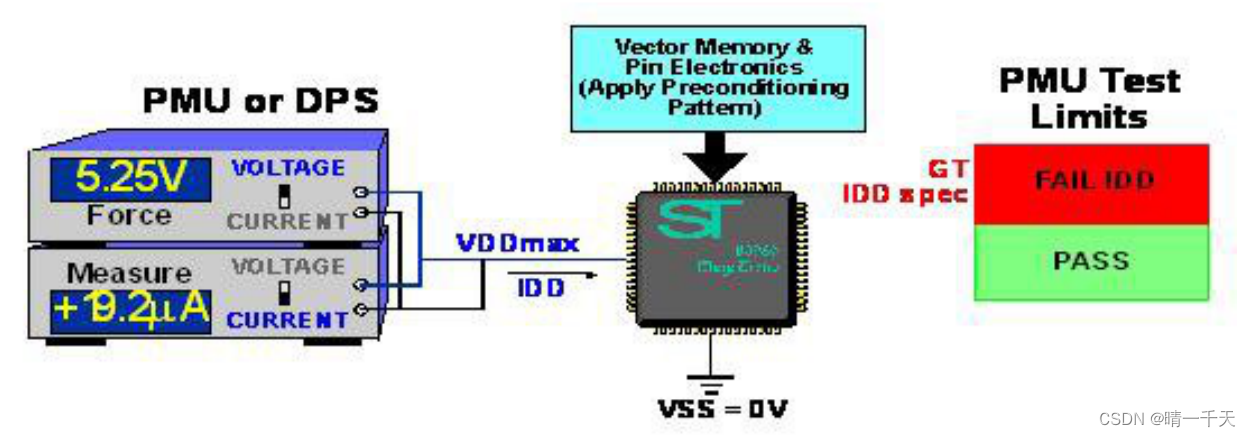

3、电源电流测试(IDD)

一件产品的功耗参数也很重要,所以产品在未工作时的电源电流消耗和工作时的电源电流消耗也需要测量。IDD测试指在额定电压下,测量器件通过电源消耗的电流功耗。IDD测试一般分为静态和动态测试,两者测试流程的区别在于程序预置的状态不同,静态IDD需要将DUT设置在静态消耗模式,动态IDD需要将DUT设置在循环工作模式。

静态IDD的测试流程:使用PMU给电源引脚输入-->执行预置状态-->DUT进行静止消耗状态,持续到测试结束-->检查电流是否超出规范的限制

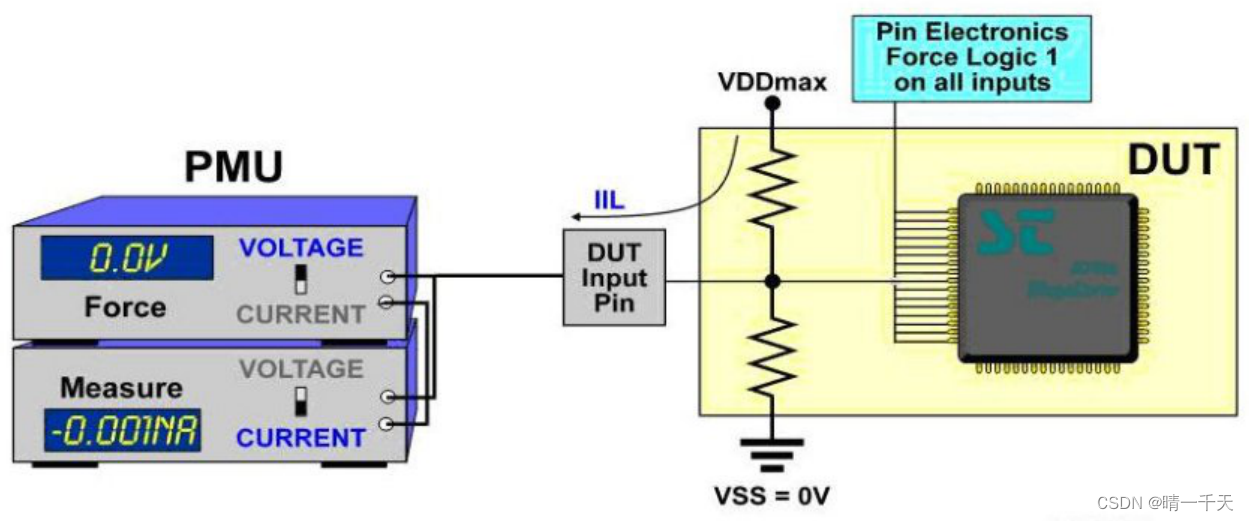

4、漏电流测试

漏电流测试是根据产品手册给额定电压的情况下,测量流入或流出的电流是否符合产品设计。漏电流测试分为输入低电平漏电流(Input Leakage Low,IIL)和输入高电平漏电流(Input Leakage High,IIH)测试。

IIL的测试流程:电源引脚输入-->其他引脚设置在高电平-->被测引脚施加0V电压,测试测量电流是IIL

5、输出电平测试

在测试过程中,我们无法直观观察输出的电平高低,而是根据功能测试判断输出电平是否符合规范设计。输出电平测试包括输出高电平(VOH)和输出低电平(VOL)测试,VOH是输出引脚在逻辑为“1”时的最小电压值,VOL是输出引脚在逻辑为“0”时的最大电压值。

VOH的测试流程:电源引脚施加-->执行预置状态,令输出引脚逻辑为“1”-->输入负向电流-->测量VOH

一些学习中的思考

1.在开短路测试中,ATE与DUT之间电气连接不正常和产品同时存在缺陷,该怎么判断?

首先,所有的板卡在上机之前会进行校准,以确保ATE硬件无异常;其次,在上线测试之前会进行调机测试,这个过程会拿一些样片进行测试,以确保电气连接无异常。

2.开短路测试中正常压降区间在0.2v-1.5v,但对于硅二极管和锗二极管分别是0.6和0.4v,区间差距太大,该区间是怎么得到的?

硅管和锗管的导通电压值不是绝对的,所以这里会是一个范围值;至于为什么是0.2-1.5,这取决于常规电平的10%-90%区间,这样进行判断可以减少误判,OS测试主要是为了检查二极管是否开短路,来判断IO是否异常,只要能筛查出开短路就够了,区间大一些可以有效减少误判的可能性。

3.为了提高测试速度,会采取并行测试的方式,并行测试的一种方法是奇偶数测试,该方式类似于二分法吗,不断二分查找pin-to-pin的短路?

奇偶测试主要是为了排除相邻引脚之间粘连短路造成误判,同时也可以提高测试效率。

4.IIL(输入低电平漏电流)测试时需要对电源引脚和非测试引脚施加高电压,原因是因为置于高电压可以确保引脚状态,防止悬空引脚带来的不确定性吗?

电源和非测试引脚施加高电平,首先可以确保芯片引脚为输出状态,其次是因为高电平可以测得此时的最大漏电流。

5.VOH(输出高电平)测试中,给DUT电源引脚施加最小VDD的严苛条件,是为了快速达到最小电压值的临界条件?

就是为了测试临界条件下的值。

6.测试前需要将DUT执行预置状态,达到所需预置条件,该条件是否唯一,还是视情况而定?

预置条件是根据芯片不同而改变的,只是常规测试基本都是一样的,可以看做的一样的而已。

7.上拉电阻/下拉电阻会影响IDD电流测试,但是需要分情况讨论,对于IIL测试,上拉电阻会存在影响,造成影响的原因是上拉电阻分压导致NMOS管电阻变小,从而电流就增大吗?此时条件是不是PMOS管是不导通的

之所以有影响是因为电阻那条链路本身就会分流,测IIL时,IO口是低电平,在电阻的两端存在压差,就会有电流通过,导致实测漏电流增大。

8.CP测试按不同要求分为CP1、CP2、CP3?

CP测试中的不同阶段,增加了对测试的深度。CP1测试基本功能,包括存储读写功能;CP2增加温度测试,晶圆经过高温烘烤后进行测试;CP3进行逻辑功能测试。

致谢文章参考:加速科技出版的《集成电路测试指南》;《the fundamentals of digital semiconductor testing》中文版

2232

2232

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?