xilinx 提供了基础的DSP模块,完成加、乘运算。

IP核讲解

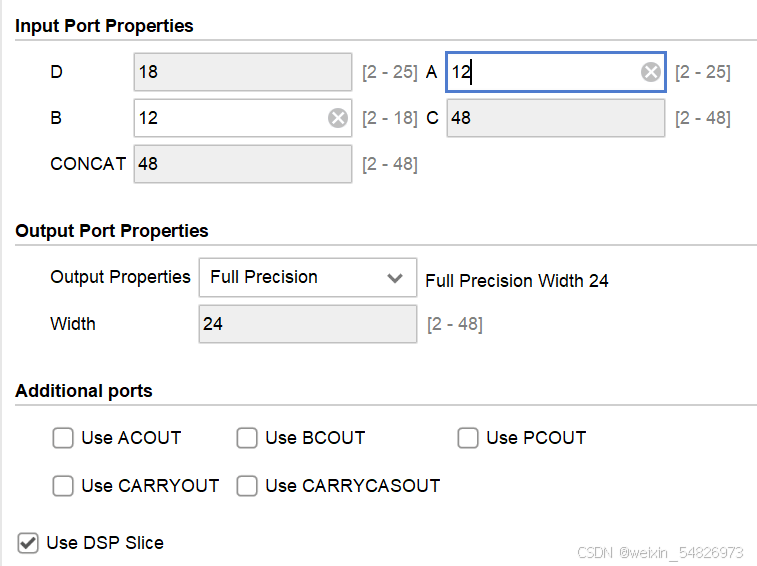

输入变量有A B C D 输出变量为P

同时每次运算提供反馈运算,即结果作为新的变量添加到输入端口,

上图界面可选择输入变量、输出变量的位宽和是否使用反馈运算。

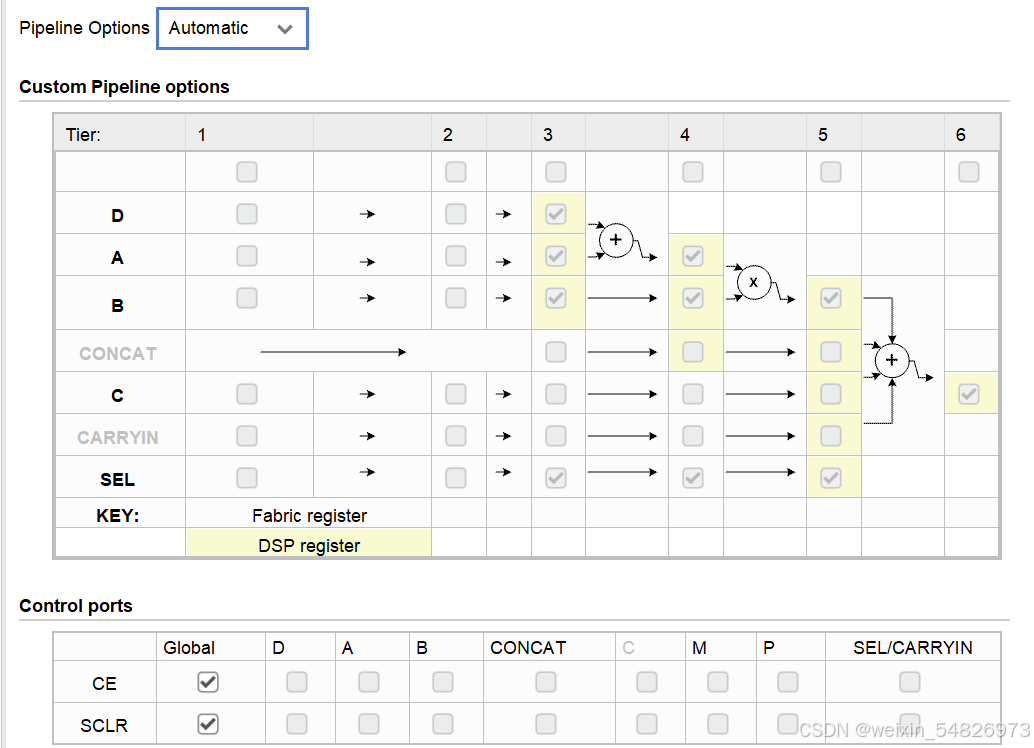

该界面选择硬件流水线架构配置,也就是运算分几步完成,一般选择自动即可。

同时控制端口可对每个端口控制,CE使能端口,SCLE重置

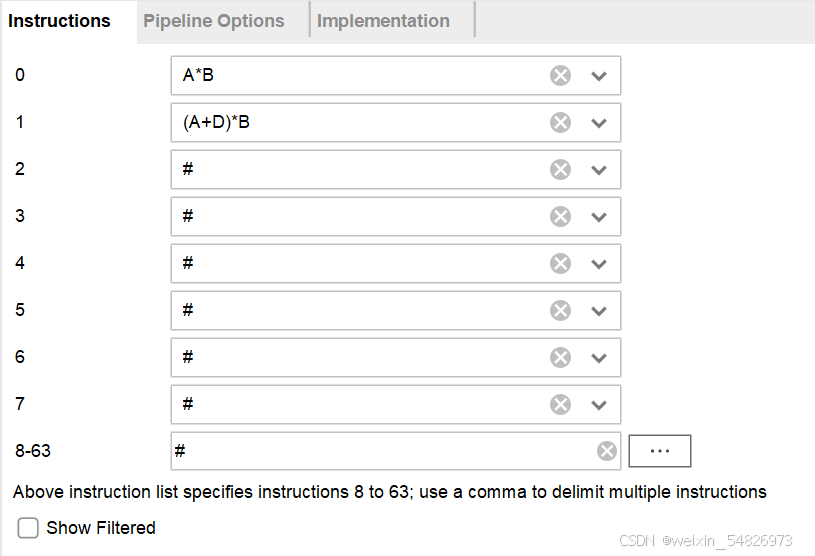

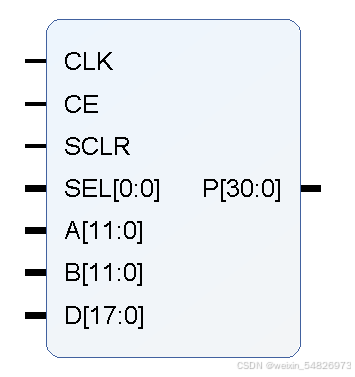

该页面配置公式,可选多个公式计算,如右图是端口示意图,SEL端口选择计算那个公式。

例化仿真

我们用verilog对 ip核心:代码

module DSP48(

input CLK,

input CE,

input SCLR,

input signed [11:0] A, // 改为有符号数

input signed [11:0] B, // 改为有符号数

output signed [23:0] P // 输出也为有符号数

);

// 例化 dsp_micro_0 模块

dsp_macro_0 dsp_init0 (

.CLK(CLK),

.CE(CE),

.SCLR(SCLR),

.A(A),

.B(B),

.P(P) // 假设 P 是 dsp_micro_0 的输出

);

endmodule

然后textbench:

`timescale 1ns/1ps

module DSP48_tb;

// 参数定义

reg CLK;

reg CE;

reg SCLR;

reg signed [11:0] A;

reg signed [11:0] B;

wire signed [23:0] P;

// 实例化 DSP48 模块

DSP48 DSP48_tb_init0 (

.CLK(CLK),

.CE(CE),

.SCLR(SCLR),

.A(A),

.B(B),

.P(P)

);

// 时钟生成

initial begin

CLK = 0;

forever #5 CLK = ~CLK; // 10ns 的时钟周期

end

// 测试向量

initial begin

// 初始化信号

CE = 0;

SCLR = 0;

A = 0;

B = 0;

// 清零

SCLR = 1; // 使清零信号有效

#10; // 等待 10ns

SCLR = 0; // 清零结束

// 启用 DSP 模块

CE = 1;

// 输入测试向量

A = 12'd125; // 输入 A = 3

B = -12'd4; // 输入 B = 2

#10; // 等待一段时间

// 结束仿真

end

endmodule

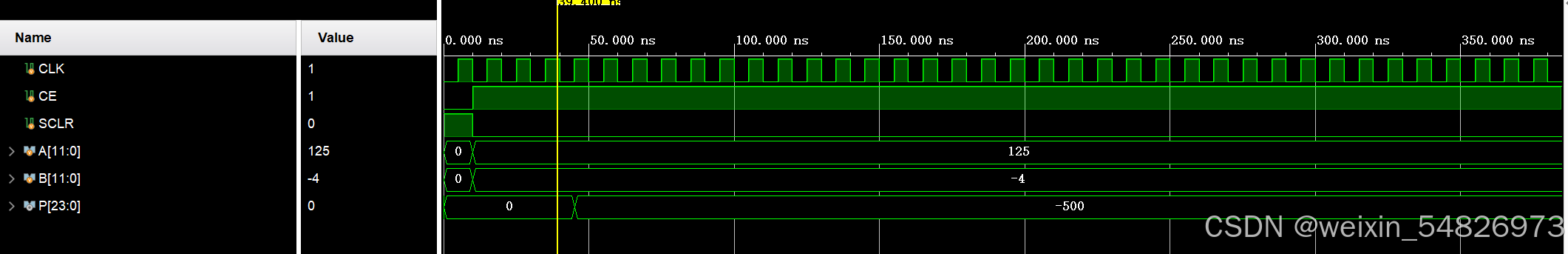

仿真结果:

设定A=125 B=-4 P=A*B=-500 ,验证结果,同时说明输入是默认有符号数,MSB是符号位。同时可以看到,从输入CE使能,开始第一个高电平开始算,4个clk周期输出结果,对应了流水线图的实际运算步骤(一个步骤一个clk)。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?