在HLS中通过对函数进行接口设置生成的IP核能够利用axi-lite在sdk中进行配置并启动,在RTL编程中利用axi4总线实现该功能

部分内容参考正点原子axi读写ddr内容;

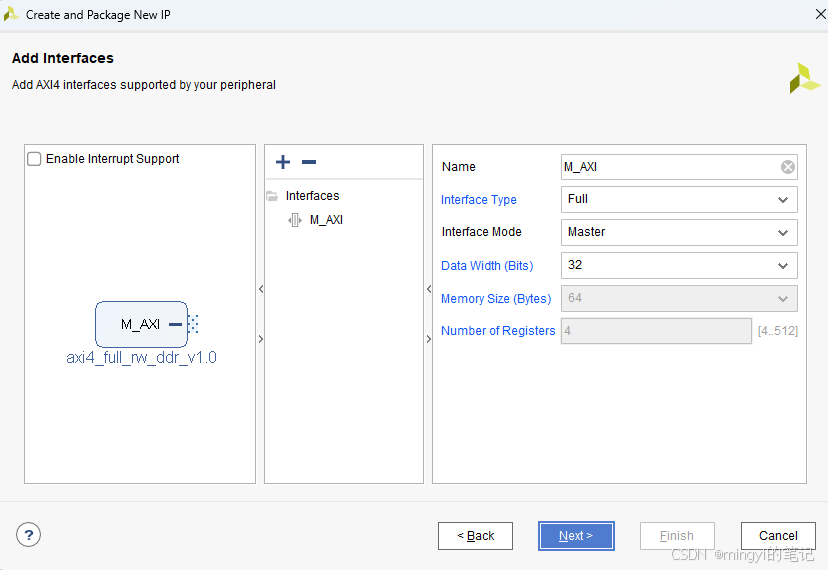

创建M_AXI4_full IP核读写DDR

zynq的ps端具有axi4-hp与axi4-gp接口,axi4-hp具有更高的传输速率,为使用hp接口,则需PL端作为主机发起读写控制请求,因此创建M_AXI4_full IP核,该IP核的功能为在DDR的4k地址范围内写入1024个32位数据,由1累加至1024

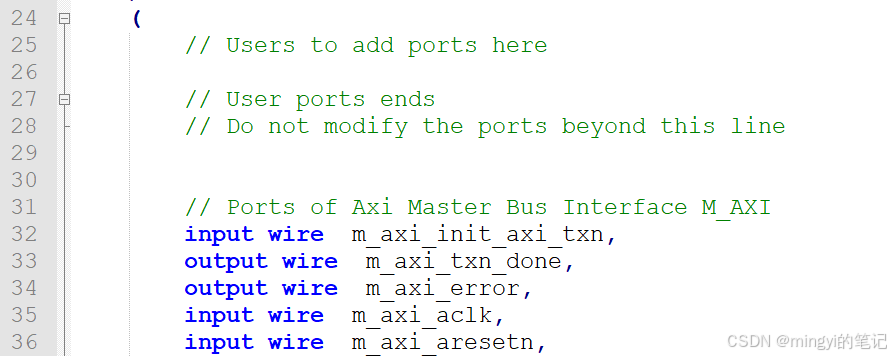

生成IP核后,可通过代码看到该IP的触发信号接口为m_axi_init_axi_txn

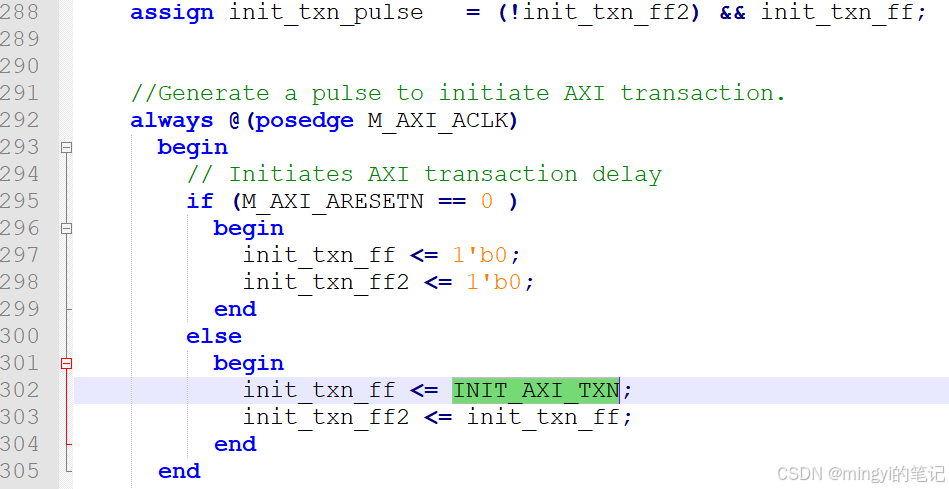

代码中对该信号进行了打拍以消除亚稳态,并采集上升沿作为触发信号,也就是说可以将一个启动信号直接与m_axi_init_axi_txn作为该IP的启动信号,因此可利用axi4_lite对指定寄存器进行控制并连接至m_axi_init_axi_txn,实现ps端利用axi4-lite启动PL端的axi4full对ddr进行读写。

打包IP核

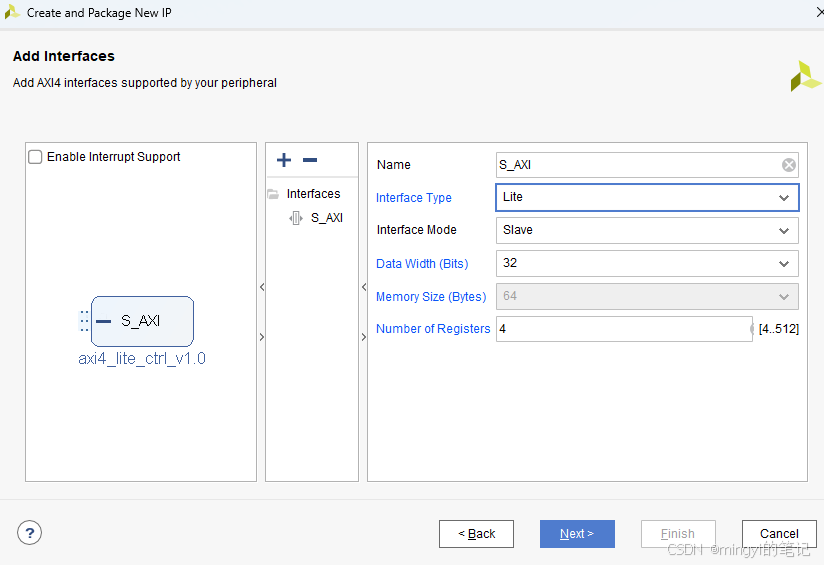

创建AXI4-lite IP核并引出配置寄存器信号

axi4-lite由PS端进行控制,因此作为从机创建s-axi4-lite IP核

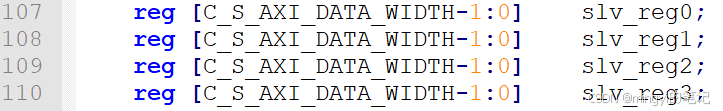

IP核内默认最少有4个可读写的寄存器,如下图,并且在代码中寄存器的复位值被设为0

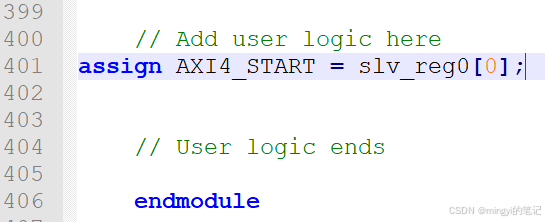

由于单个寄存器的位宽为32位,将slv_reg0[0](最低位)信号引出,

定义 output wire AXI4_START,并在顶层模块同样定义output wire axi4_start

在代码尾部添加如下代码

并将AXI4_START例化至顶层模块 .AXI4_START(axi4_start)

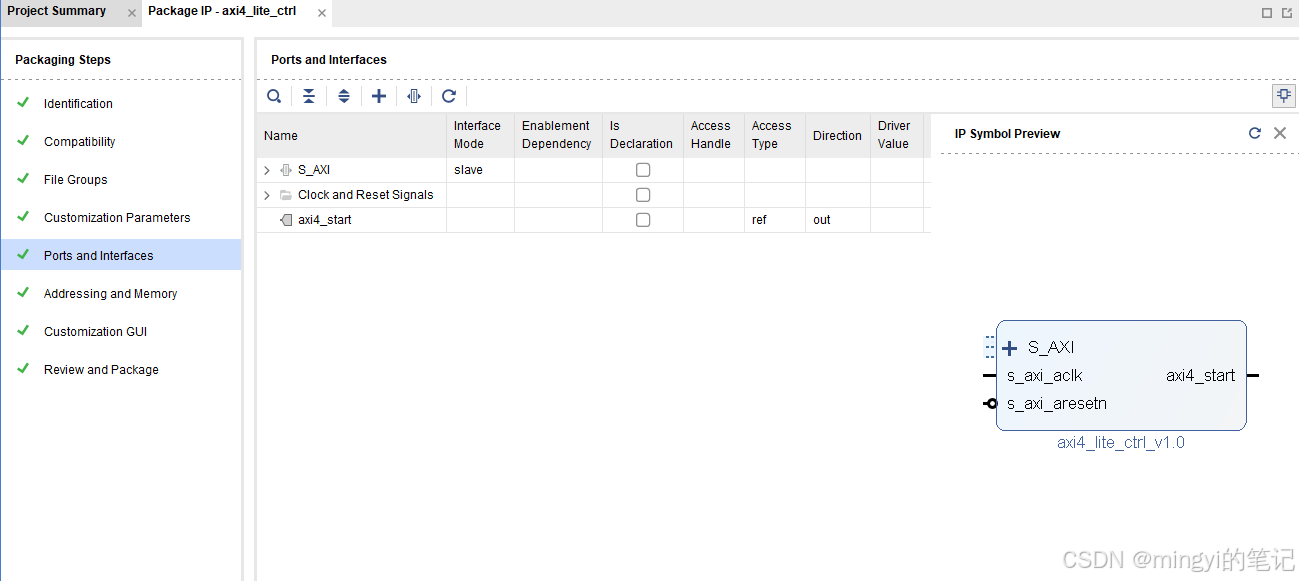

最后打包IP核如下图

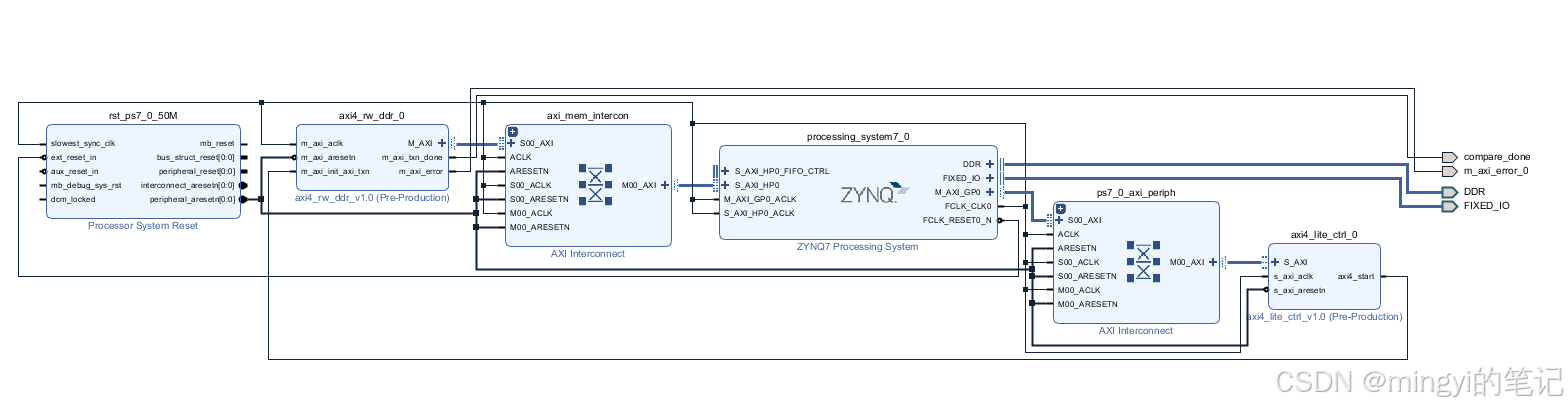

创建vivado BD

新建工程,并导入以上两个IP核,

添加zynq核心,配置ddr、uart、s_axi_hp、m_axi_gp、PL时钟与复位,

将m_axi4_full IP核的m_axi_init_axi_txn信号连接至axi4_lite IP核的axi4_start,

将m_axi_txn_done与m_axi_error引出,并分配管脚至led作为完成信号和错误信号,

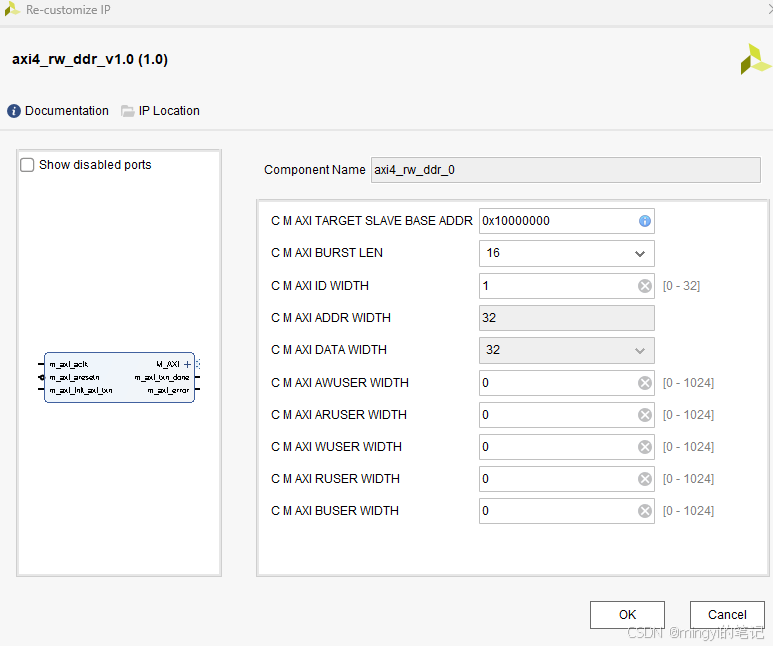

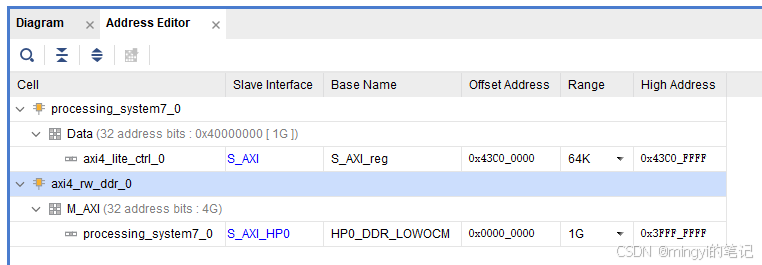

注意m_axi4_full IP核的默认地址应在Adress Editor中PS_DDR的地址范围内,

C M AXI USER WIDTH全部设为0

BD设计如下图

完成bd设计后generate output,create hdl wrapper,添加PL led管脚约束文件(或手动设置),最后生成比特流,export hardware ,launch SDK

SDK工程

创建sdk工程,代码如下

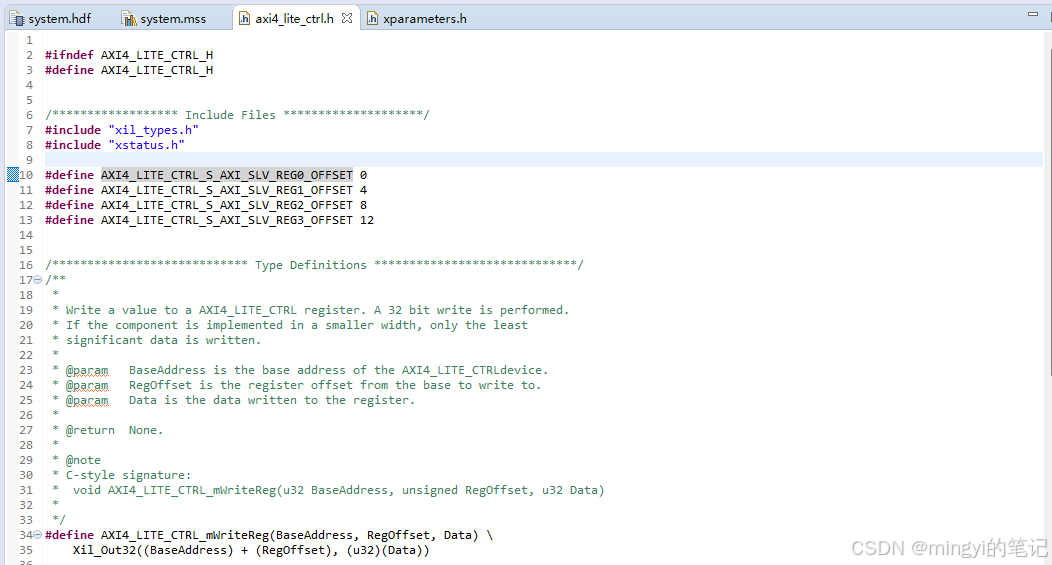

sdk默认给出的axi4-lite IP核内容如下,下图给出了IP核内指定寄存器的偏移地址(10-13行),

向寄存器写数据的函数(34或35行),函数内三个参数分别为基地址,偏移地址,写入数据,

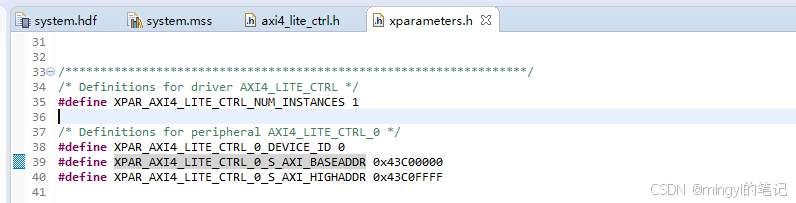

基地址可在“xparameters.h”中找到,如下图39行

SDK代码如下

#include "stdio.h"

#include "xil_cache.h"

#include "xil_printf.h"

#include "xil_io.h"

#include "axi4_lite_ctrl.h"

#include "xparameters.h"

#define axi_lite_baseaddr XPAR_AXI4_LITE_CTRL_0_S_AXI_BASEADDR

#define axi_lite_start_reg AXI4_LITE_CTRL_S_AXI_SLV_REG0_OFFSET

int main()

{

int i;

char c;

Xil_DCacheDisable();

printf("AXI4 PL DDR TEST!\n\r");

for(i=0;i<4096;i=i+4)

{

printf("%d is %d\n",i,(int)(Xil_In32(0x10000000+i)));

//地址要与axi4-full IP核中的地址保持一致

}

while(1)

{

scanf("%c",&c);

if(c == 's'){

AXI4_LITE_CTRL_mWriteReg(axi_lite_baseaddr, axi_lite_start_reg, 0x00000001);

//向slv_reg0[0]写入1(slv_reg0为32位寄存器)

for(i=0;i<4096;i=i+4)

{

printf("%d is %d\n",i,(int)(Xil_In32(0x10000000+i)));

//地址要与axi4-full IP核中的地址保持一致

}

}

}

return 0;

}

首先读取DDR指定地址起始的4k字节的数据,4个字节为1个32位数据,共在串口打印1024个,且为随机不规则数据,当串口检测到有“s”输入时,启动m_axi4_full IP对以上地址写入数据,由1-1024,并再从地址读出数据并校验是否正确,最终将地址更新的数据内容打印至串口为1-1024,PL端done信号的led点亮,error led熄灭。

8213

8213

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?