目录

1. AXI总线概述

AXI(Advanced eXtensible Interface)总线是ARM公司在AMBA 3.0协议中提出的一个重要部分,主要面向高性能、高带宽、低延迟的片内总线设计。在AMBA 4.0版本中,AXI被进一步发展为AXI4,包括AXI4、AXI4-Lite、AXI4-Stream等多个版本。

1.1 主要特点

高性能和高频率系统设计:AXI协议支持高带宽和低延时设计,适合于需要高频操作的系统。

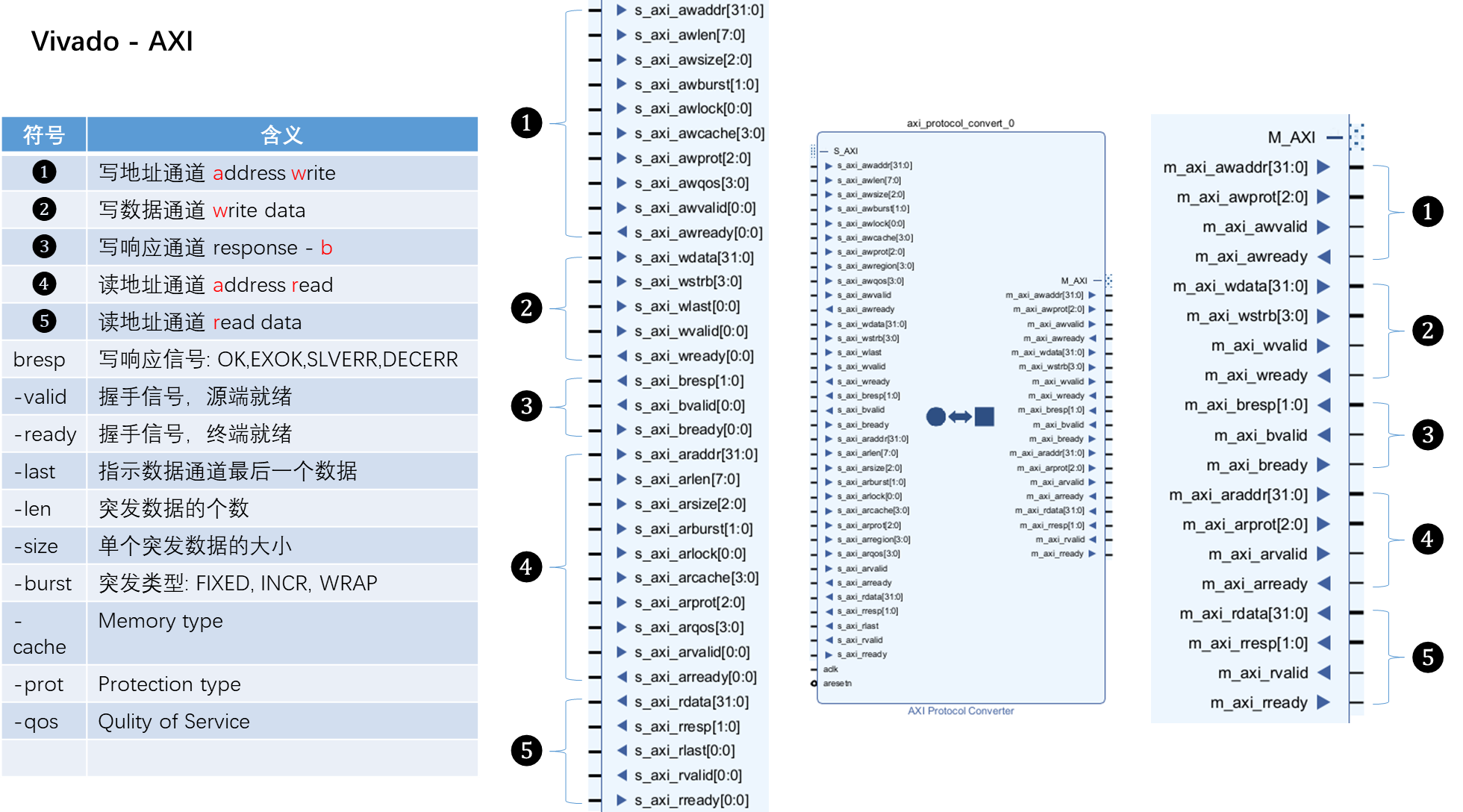

读写通道分离:AXI协议定义了五个独立的传输通道,包括读地址通道、读数据通道、写地址通道、写数据通道和写响应通道,从而支持全双工的数据传输。

灵活的互联架构:AXI提供了单一的接口定义,适用于master/interconnect、slave/interconnect和master/slave之间的连接。

支持多种传输类型:包括burst传输、乱序传输和outstanding传输,有助于提高数据处理效率。

易于时序收敛:AXI协议允许在任何通道的任何点插入寄存器级,以实现时序收敛。

1.2 通道功能

读地址通道(Read Address Channel):携带读操作的地址和控制信息。

读数据通道(Read Data Channel):用于从slave到master的数据传输。

写地址通道(Write Address Channel):携带写操作的地址和控制信息。

写数据通道(Write Data Channel):用于从master到slave的数据传输。

写响应通道(Write Response Channel):用于slave对写操作的响应。

1.3 信号概览

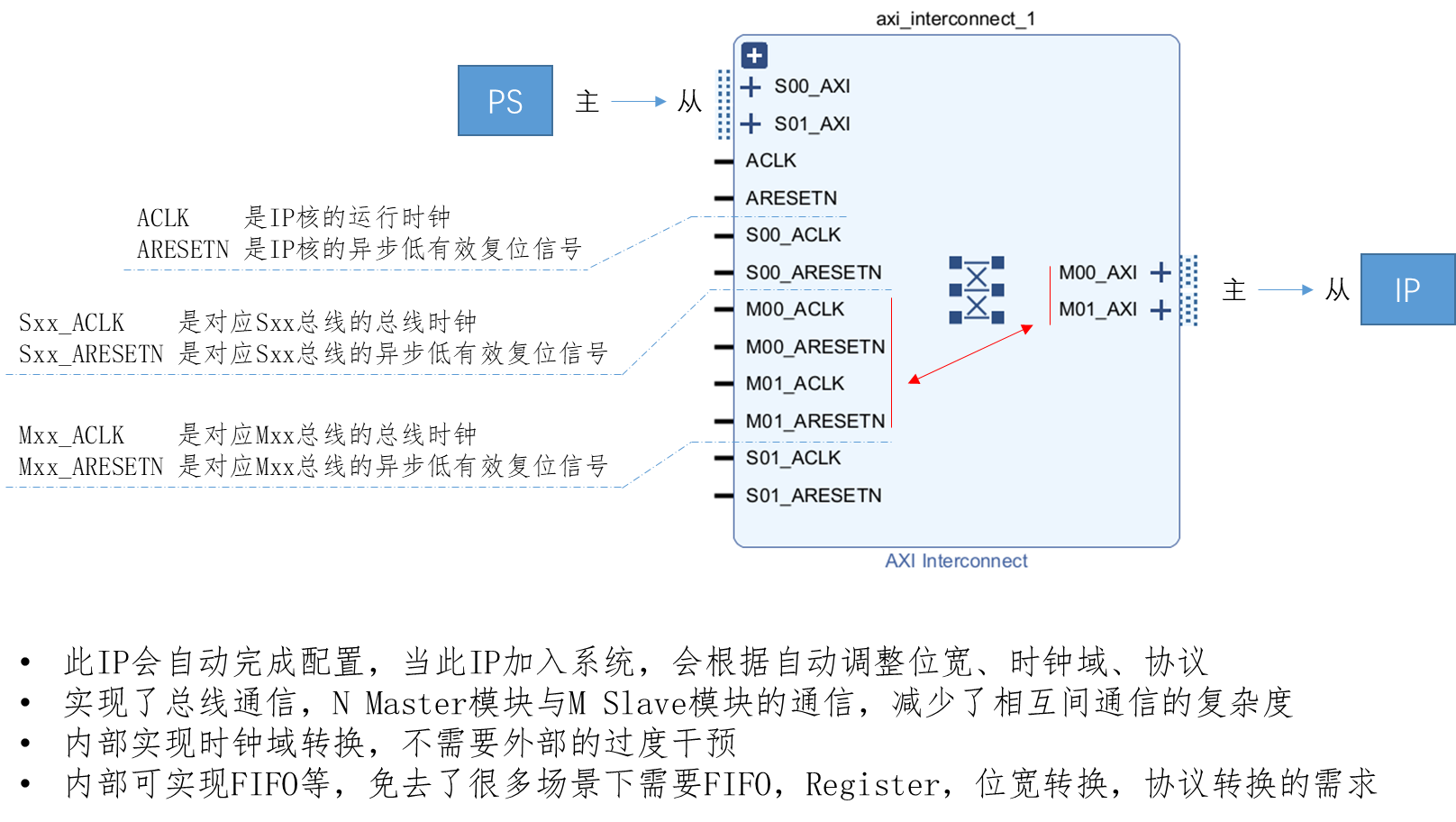

2. AXI Interconnect

AXI Interconnect 非常常见。它用于连接多个AXI主设备和从设备的关键组件。它是ARM AMBA规范的一部分,专门设计来处理多个主设备和从设备之间的通信。

AXI Interconnect 一般由Vivado自动生成并连接。理解其作用有助于提到系统设计能力。

2.1 信号说明

本文详细介绍了AXI总线的特点、通道功能以及AXIInterconnect在系统设计中的角色,包括Vivado生成的连接、信号转换组件和ILA在观察AXI信号的应用。重点讨论了AXI4协议、AXI-FPD/LFP/ACP、地址编辑和AXI-DDR等内容。

本文详细介绍了AXI总线的特点、通道功能以及AXIInterconnect在系统设计中的角色,包括Vivado生成的连接、信号转换组件和ILA在观察AXI信号的应用。重点讨论了AXI4协议、AXI-FPD/LFP/ACP、地址编辑和AXI-DDR等内容。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2114

2114

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?