1.双脉冲实验实验的必要性

在平常的使用中,我们基本通过芯片手册来了解功率器件的各种性能参数,但是手册中的参数的测量环境都是在理想状态下,与实际使用或多或少都会有差别。通过双脉冲实验可以获取器件在真实工况下的参数,对于产品设计很有帮助。

2.具体作用

评估驱动电阻数值是否合适,是否需要加吸收电路

衡量开关管在实际电路中的表现,主要有反向恢复电流,关断电压尖峰,开通关断时间

观察器件的栅极波形,评估驱动板是否能为开关管的开启提供足够的驱动电流

获取开关管在开通、关断过程的主要参数,以评估Rgon与Rgoff的选择是否合适

观察开通、关断过程是否有电压尖峰,评估实际应用是否需要吸收电路

评估二极管的反向恢复行为和安全裕量;

测量母排的杂散电感;

3.双脉冲的具体原理

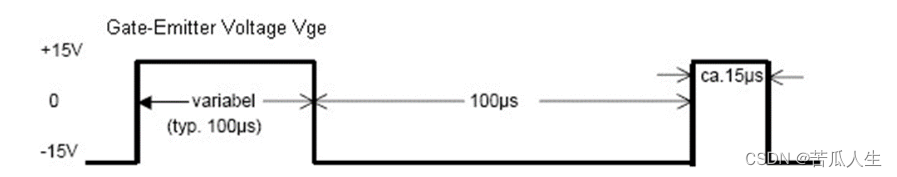

从名字上可以看出,双脉冲是以两个脉冲的形式发送脉冲信号,这两个脉冲的区别一个宽一个窄。

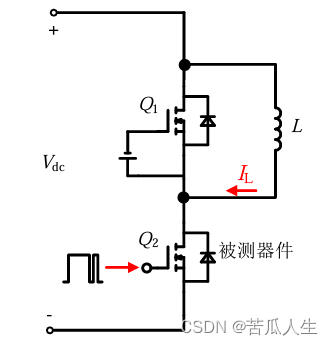

测试的原理图

在直流侧加上直流电压

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3483

3483

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?