闪存基本原理

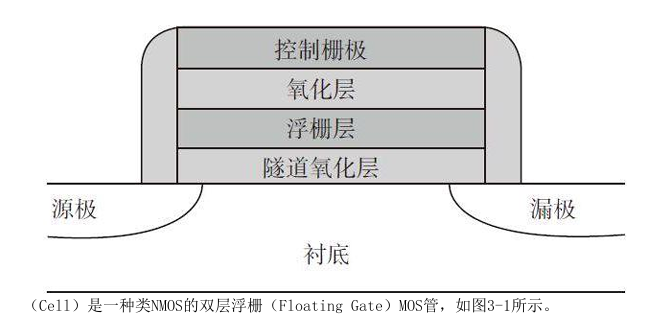

Nand Flash是一种非易失性存储器(Non-volatile memory),通俗来说,就是掉电之后不会丢失数据。闪存的基本存储单元为:“浮栅晶体管”,如图所示

浮栅极内没有电子,用状态 1 表示。存储一定量电子的状态用 0 表示。

读写擦操作原理

- 写操作:(电子进入浮栅极)在控制极添加一个比较大的正电压,电子会穿过隧道氧化层进入浮栅极

- 擦除操作:(电子从浮栅极出来)在衬底添加一个大的正电压,电子会从浮栅极经过隧道氧化层回到衬底

- 读操作:(晶体管是否导通)通过在控制极添加一个中等电压,判断晶体管是否导通,如果导通则状态为1,否则为0。假设浮栅极内现在没有电子(即状态为1),此时导通电压为0.1v。注入一定量电子之后(状态为0),此时的导通电压为0.5v。我们在控制极加一个0.3v的电压(参考电压),如果晶体管导通,则为1,反之则为0。

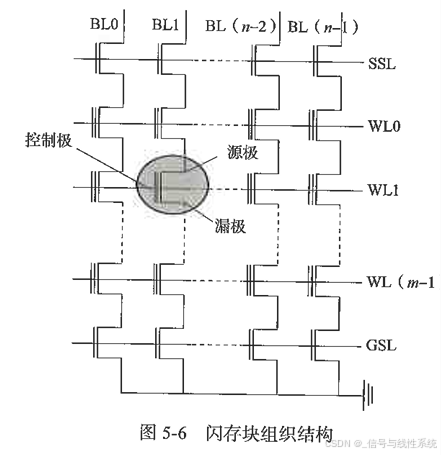

闪存块的组织结构

微观角度

Word line和Bit line,它俩是NAND Flash中存储阵列用于寻址和操作存储单元的核心结构。

- WL:是连接存储单元控制极的横向导线,负责激活某一整行所有的存储单元,使其进入可操作状态

- BL:是连接源极 / 漏极的纵向导线,负责读写某一列的数据,在读数据的过程中,BL可以检测到电流的变化

对于SLC来说,因为一个存储单元内存储 1 bit数据,所以1个字线包含一个Page。TLC包含3个Page。一个Page有多少Bit,就存在多少位线。

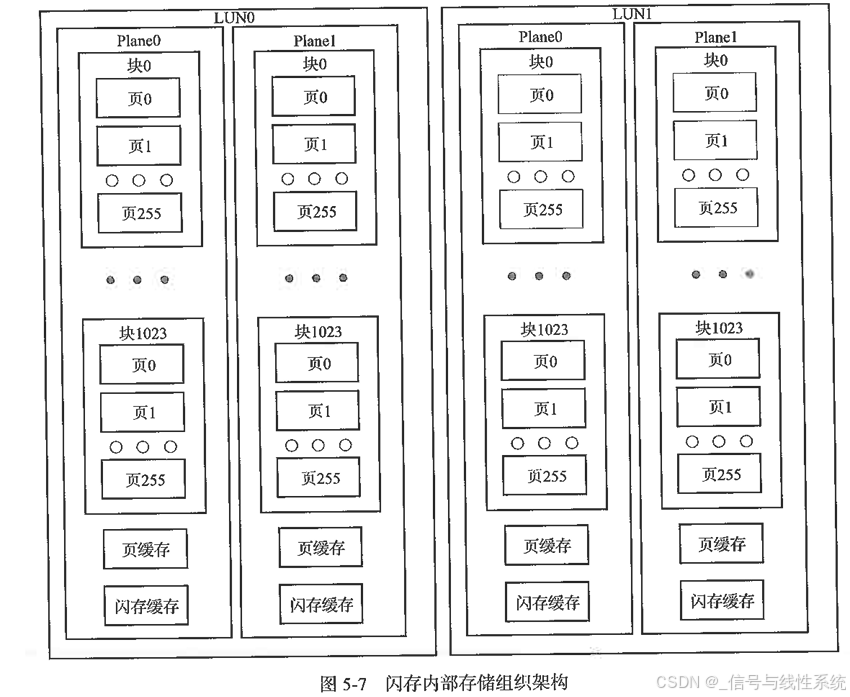

宏观角度

Page是读写操作的最小单位

Block是擦除操作的最小单位,因为在一个Block中,所有的存储单元都共用一个衬底,擦除操作要在衬底加一个强电压,会将所有存储单元的电子吸出来,因此擦除操作的最小单位是Block

Plane是芯片内部的一个区域,它拥有独立的Cache Register 和 Page Register的物理结构,可以独立进行读写擦操作,多个Plane可以并行执行读写擦操作。

LUN是SSD中能够独立执行命令的闪存单元,可以单独寻址,但是在一个LUN中,一次只能执行一个命令(因为闪存传输总线不能共用)

3405

3405

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?