利用modelsim直接添加库文件并进行仿真

由于某些原因,需要使用modelsim单独添加一些库文件进行编译,这里可以是altera/xilinx/lattice的库,也可以添加自己写的库,只要编译通过就行。

一 Modelsim添加altera/xilinx/lattice的库

1.在modelsim的安装目录下找到"modelsim.ini"文件,将属性选项里的"只读"去掉,添加库的时候会在里面写入路径。

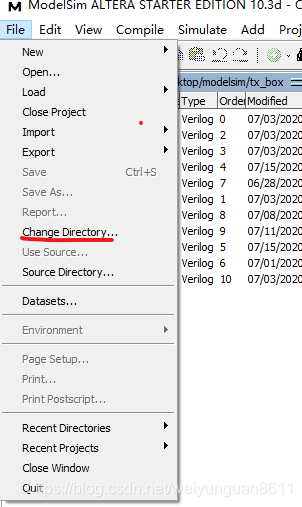

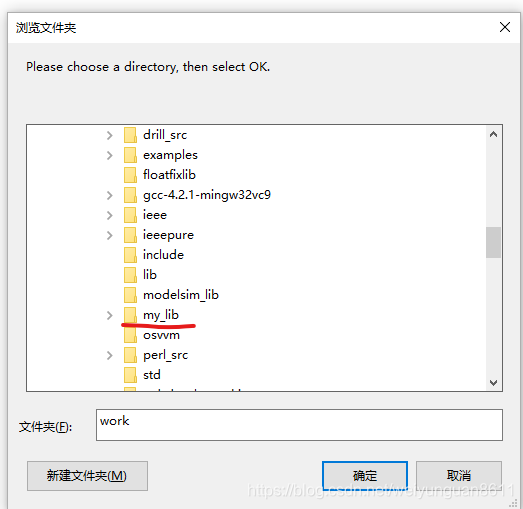

2.打开modelsim,点击file下的change directory,将路径改为你要添加库文件的文件夹,我在安装目录下新建了一个文件夹,这里我放到了my_lib文件夹下面。

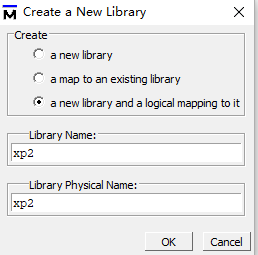

3.点击file-new-library,新建一个库,输入库名称,在modelsim的library界面下会新建一个xp2库。

接下来点击Modelsim菜单栏的compile–compile,出现编译窗口,将library选为你新建的库,找到D:\modelsim\modelsim_ase\my_lib\verilog\xp2,Ctrl+A选中全部文件(前提是你要有要加入的.v文件),点击compile开始编译,编译完成后点Done结束。注意这里上面的Library要选择你建立的库。

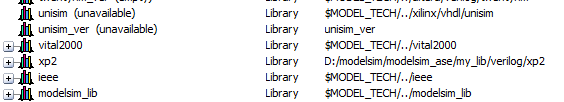

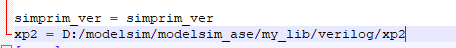

4.此时打开"modelsim.ini",里面多了一句xp2 = xp2,将后面那个改为你的物理路径,

xp2 = D:/modelsim/modelsim_ase/my_lib/verilog/xp2(否则会出现unname什么的,注意这里用 / 而不是用 \ )。最后将modelsim.ini的只读勾上,只是VHDL要麻烦一些得注意编译的顺序。

二 功能仿真

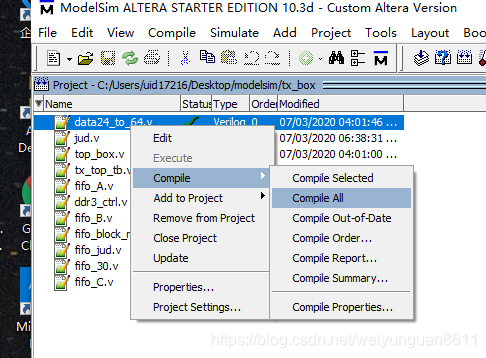

- New—project,新建一个工程,导入testbench和待测试文件,右击或在菜单栏中选择compile all。编译通过的status栏会有一个绿色的勾,未编译是黄色的问号,通不过是红色的叉叉。

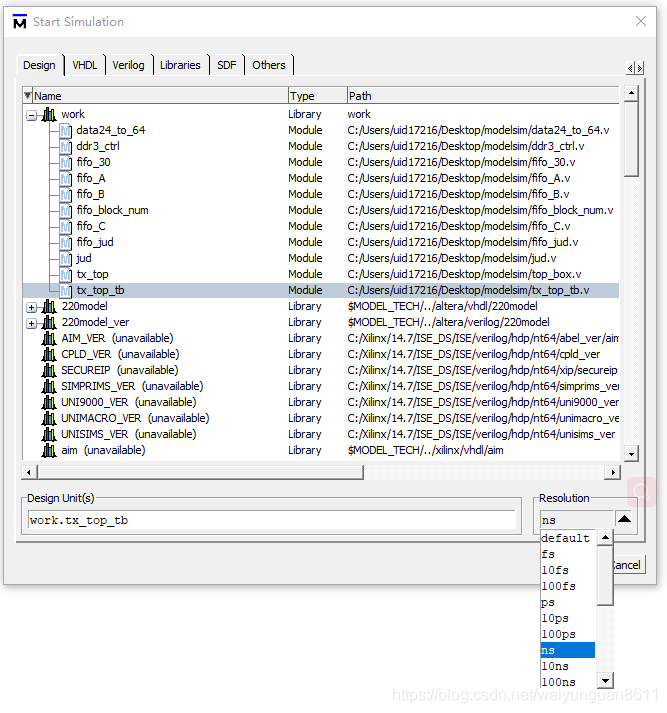

2 .仿真,点击菜单栏中的simulate—start simulate,在design标签中选择测试文件。选定进行仿真的文件(默认在work工作库中),如果文件中没有设置时间单位,可以在Resolution选择,最好把optimization中的勾取消,不然很多寄存器会被优化掉。如果没有用到pll等 ip core的话,点击OK就可以进行仿真了。这一步也可以直接在library界面,右击测试文件选择simulate without optimization 进行仿真。

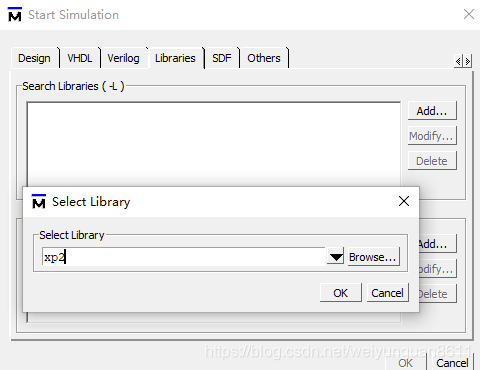

另外在library选项中切记加入自己刚才的库要不然会报错

到这里基本就结束了,可以开始进行仿真了。

参考链接:http://blog.sina.com.cn/s/blog_88c9ddc50101bn17.html

通过自己记录的方式,方便今后的学习,以及和小伙伴们共同进步。如果觉得有用的话请关注和点赞,感谢老铁。

另外我的fpga的全部资料和笔记在这里哦(欢迎浏览查看):https://blog.csdn.net/weiyunguan8611/article/details/100934712

本文详细介绍了如何在ModelSim中添加Altera/Xilinx/Lattice等库文件,并进行功能仿真。步骤包括修改modelsim.ini,创建库,编译库文件,以及设置仿真参数。适合FPGA初学者及进阶用户。

本文详细介绍了如何在ModelSim中添加Altera/Xilinx/Lattice等库文件,并进行功能仿真。步骤包括修改modelsim.ini,创建库,编译库文件,以及设置仿真参数。适合FPGA初学者及进阶用户。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?