Vivado 调试报错,显示

ERROR: [Labtools 27-3412] Mismatch between the design programmed into the device 'xc7a100t' (JTAG device index = '0'

and the probes file(s) 'E:/0_WORK/FQPB_Prj/par/FQPB_Prj_0126.runs/impl_1/IDCU_FPGA_TOP.ltx'.

The hw_probe 'u0_sys_clk_gen/async_rst' in the probes file has port index '1'. This port location for the ILA core at location (uuid_44686827098D55E5A4639609BA1F5BBF), does not support a data probe.

.

Resolution:

1) Ensure that the clock signal connected to the debug core and/or debug hub is clean and free-running.

2) Ensure that the clock connected to the debug core and/or debug hub meets all timing constraints.

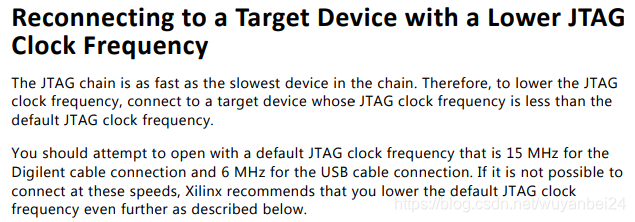

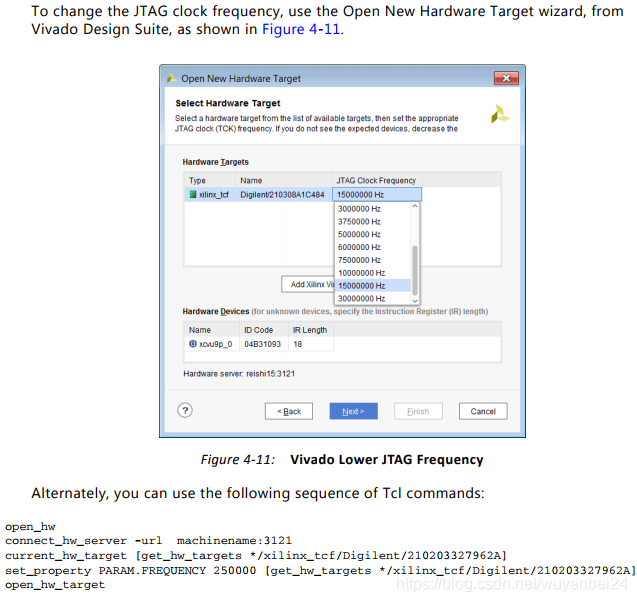

3) Ensure that the JTAG clock frequency is 2.5x times slower than the frequency of the clock connected to your debug hub.

首先排除ILA没有接时钟的问题,因为ILA采用的是free running的晶振时钟

然后从网上百度查看,现实ILA可能深度设置不对, 可以通过以下Tcl命令查询,修改ILA的深度

[Xicom 50-38] xicom: Unknown deviceType: 1

[Xicom 50-38] xicom: Could not set Parameter: capture_ctrl_config

get_property CONTROL.DATA_DEPTH [get_hw_ilas]

set_property CONTROL.DATA_DEPTH 1024 [get_hw_ilas]

经过以上操作还是不能解决时钟的问题,最后在Xilinx的官方论坛,有人遇到过相同的问题,链接如下:

https://forums.xilinx.com/xlnx/board/crawl_message?board.id=OTHER&message.id=10491

本质问题是买的仿真器太水,Jtag的时钟频率太高

1989

1989

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?