名称:多功能波形发生器Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

基于 Verilog HDL多功能波形发生器的设计设计任务:多功能波形发生器

内容及要求

1、要求产生三种波形:方波、三角波,正弦波

2、每个波形周期采样16个点

3、可输出频率分为有100HZ,200HZ,500HZ及1KHZ

设计任务

1、说明设计具体思路

2、画出系统模块框图

3、画出系统顶层原理图

4、按设计技术要求编写程序

5、出系统功能仿真波形图

6、设计出硬件实现电路图,下载测试

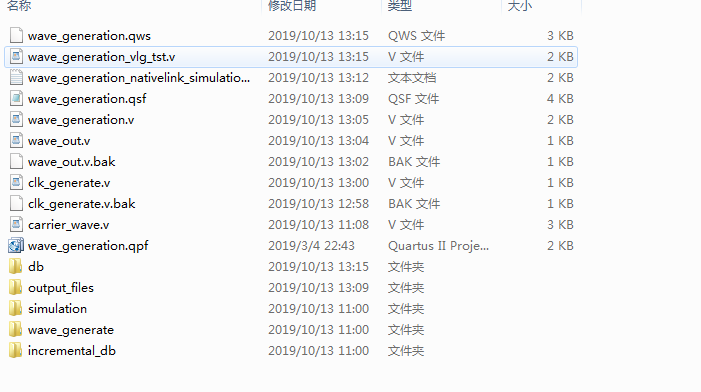

1. 工程文件

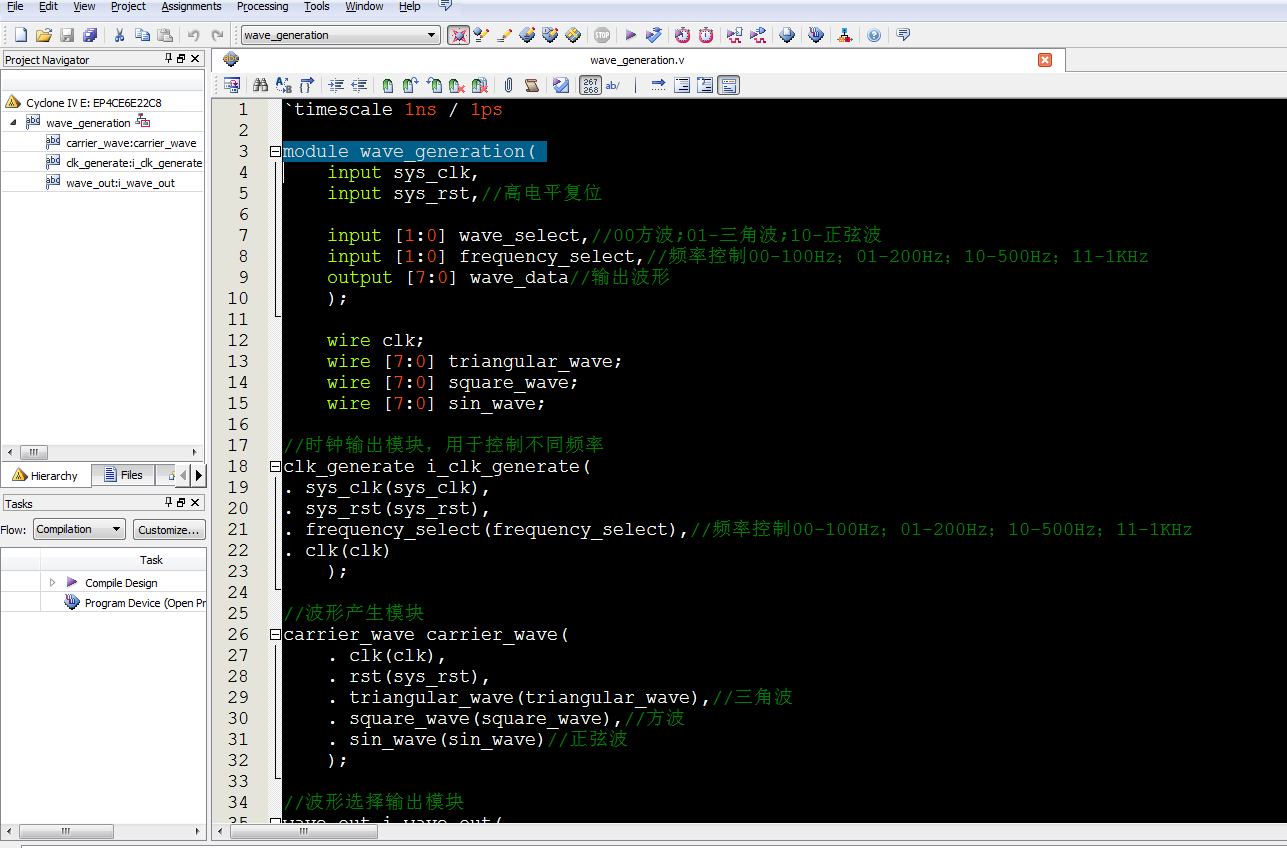

2. 程序文件

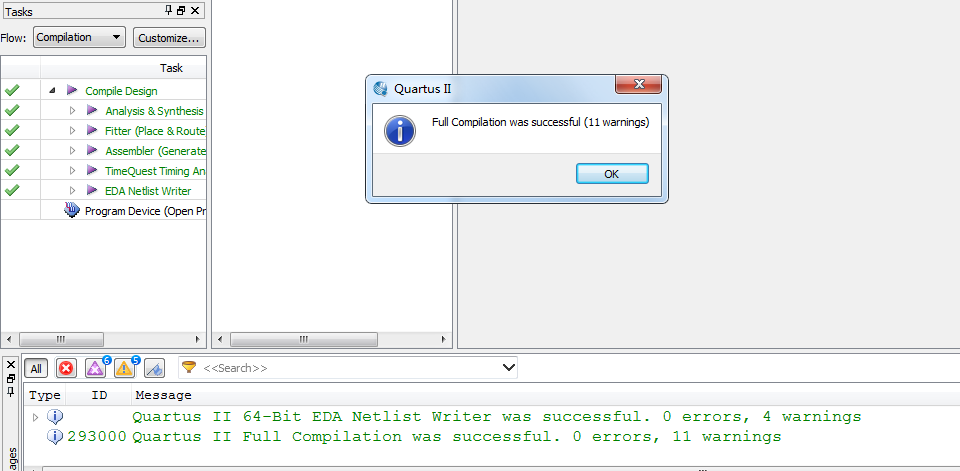

3. 程序编译

4. RTL图

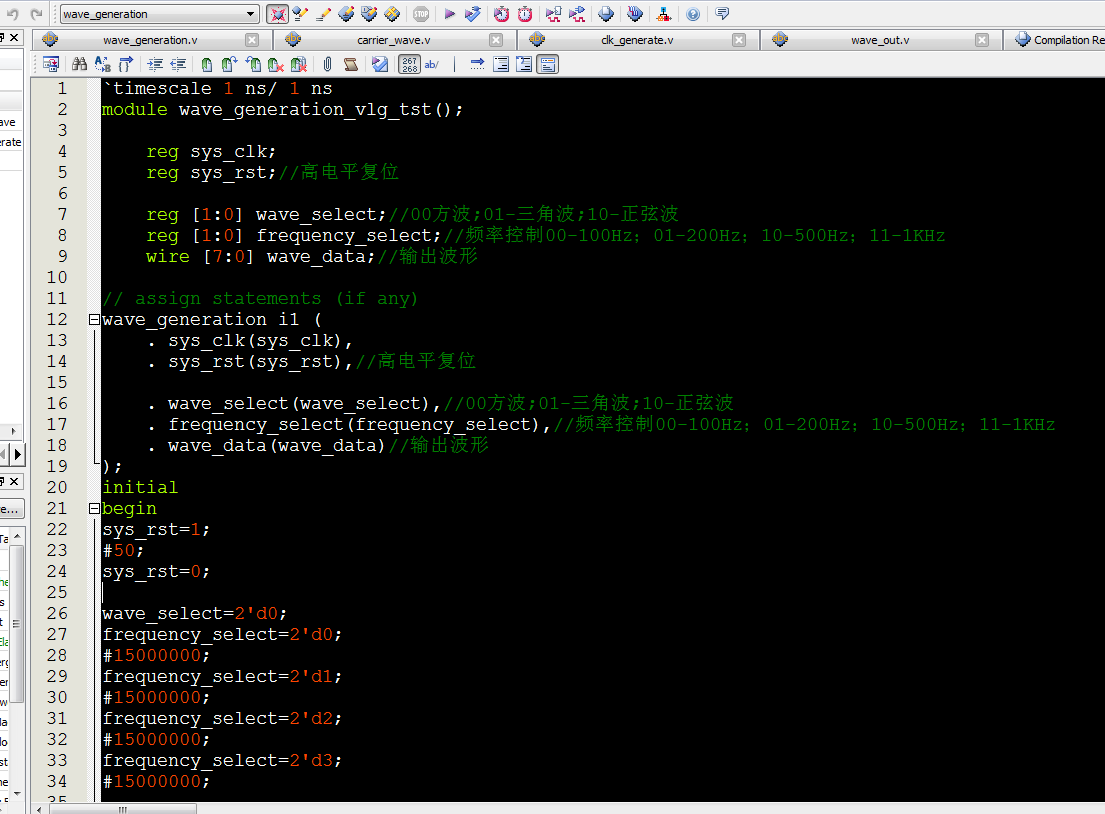

5. Testbench

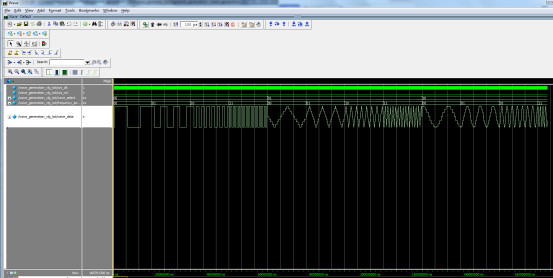

6. 仿真图

部分代码展示:

`timescale 1ns / 1ps module wave_generation( input sys_clk, input sys_rst,//高电平复位 input [1:0] wave_select,//00方波;01-三角波;10-正弦波 input [1:0] frequency_select,//频率控制00-100Hz;01-200Hz;10-500Hz;11-1KHz output [7:0] wave_data//输出波形 ); wire clk; wire [7:0] triangular_wave; wire [7:0] square_wave; wire [7:0] sin_wave; //时钟输出模块,用于控制不同频率 clk_generate i_clk_generate( . sys_clk(sys_clk), . sys_rst(sys_rst), . frequency_select(frequency_select),//频率控制00-100Hz;01-200Hz;10-500Hz;11-1KHz . clk(clk) ); //波形产生模块 carrier_wave carrier_wave( . clk(clk), . rst(sys_rst), . triangular_wave(triangular_wave),//三角波 . square_wave(square_wave),//方波 . sin_wave(sin_wave)//正弦波 ); //波形选择输出模块 wave_out i_wave_out( . sys_clk(sys_clk), . wave_select(wave_select),//00方波;01-三角波;10-正弦波 . triangular_wave(triangular_wave), . square_wave(square_wave), . sin_wave(sin_wave), . wave_data(wave_data)//输出波形 ); endmodule

源代码

扫描文章末尾的公众号二维码

本文详细介绍了一种基于VerilogHDL的多功能波形发生器的设计,包括产生方波、三角波和正弦波的功能,支持100Hz至1kHz的不同频率。文章涉及系统模块设计、顶层原理图、Verilog代码编写、Testbench测试以及Quartus仿真过程。

本文详细介绍了一种基于VerilogHDL的多功能波形发生器的设计,包括产生方波、三角波和正弦波的功能,支持100Hz至1kHz的不同频率。文章涉及系统模块设计、顶层原理图、Verilog代码编写、Testbench测试以及Quartus仿真过程。

2311

2311

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?