名称:基于FPGA的通用电子密码锁VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

电子密码锁要求

(1)如果按下数字键,第-个数字会从显示器的最右端开始显示,此后每新按一个数字时,显示器上的数字必须左移一格,以便将新的数字显示出来。

(2)假如要更改输入的数字,可以按倒退按键来清除前一个输入的数字,或者按清除键清除所有输入的数字,再重新输入四位数。

(3)由于这里设计的是一个四位的电子密码锁,所以当输入的数字键超过四个时,电路不予理会,而且不再显示第四个以后的数字。

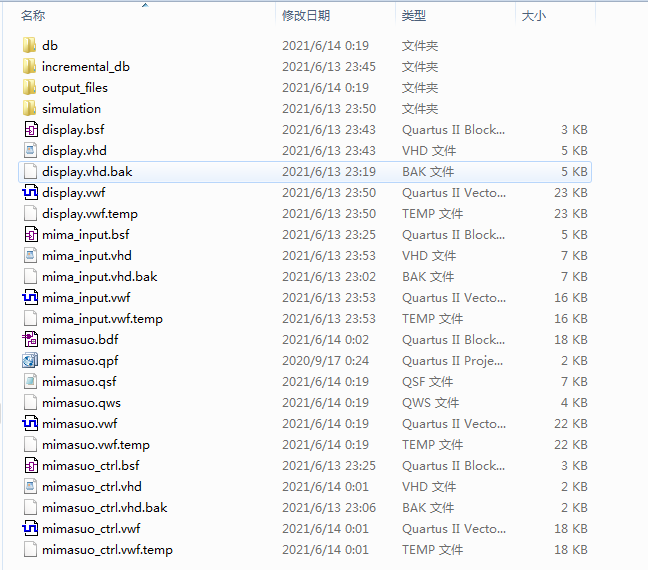

1. 工程文件

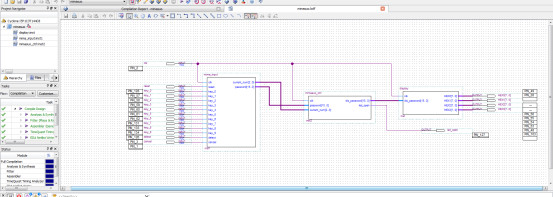

2. 程序文件

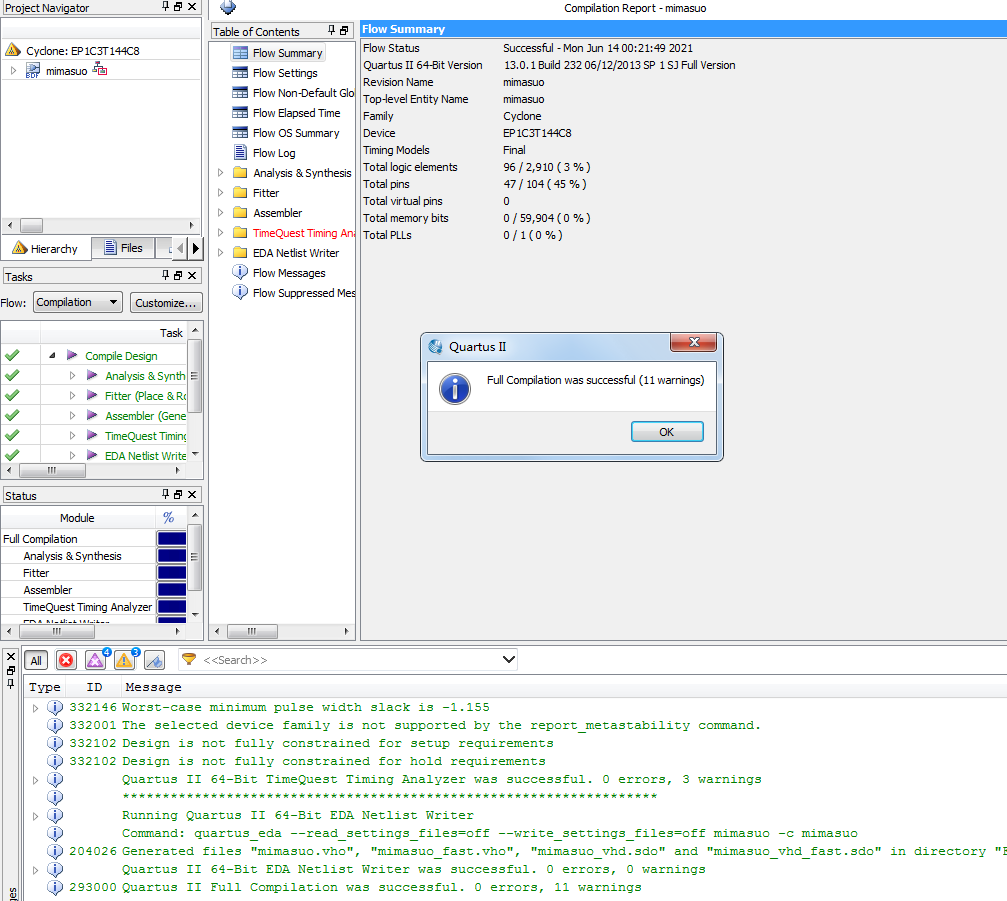

3. 程序编译

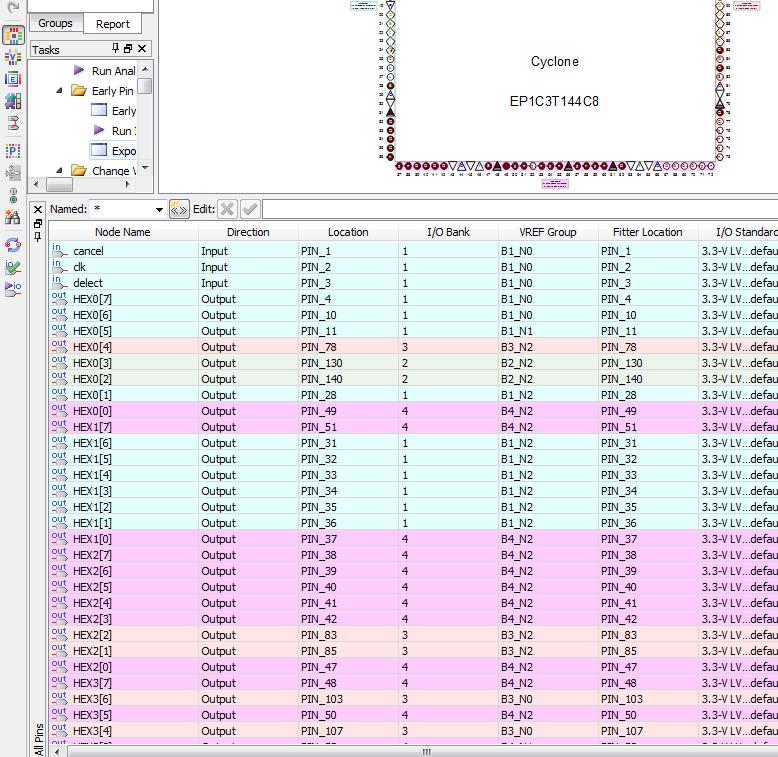

4. 管脚分配

5. 仿真图

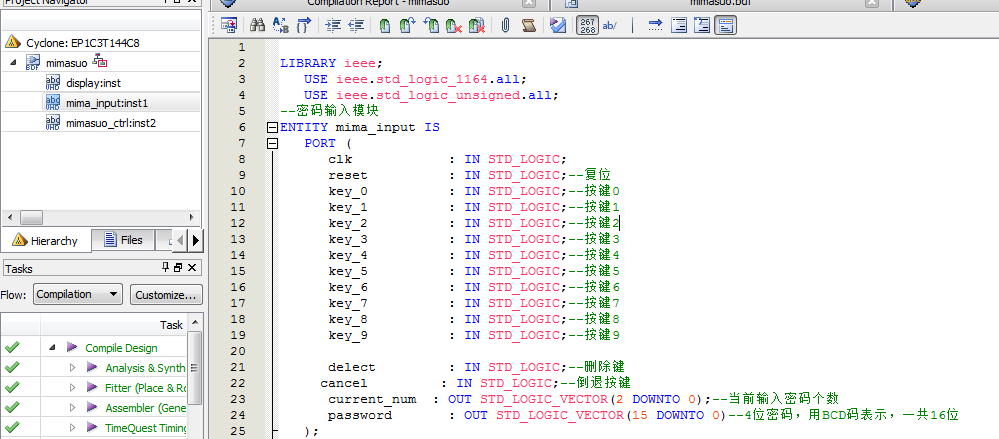

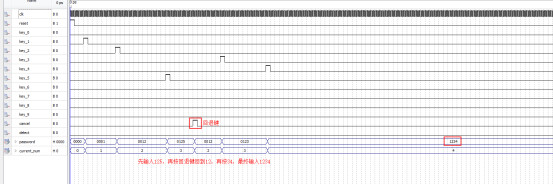

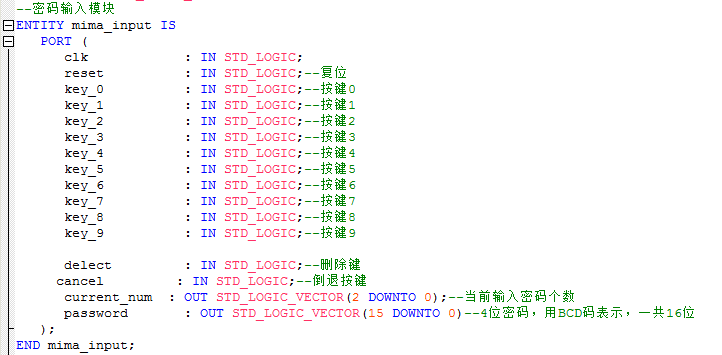

密码输入模块

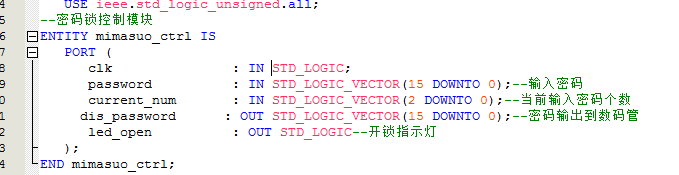

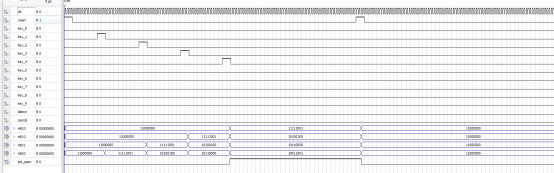

控制模块

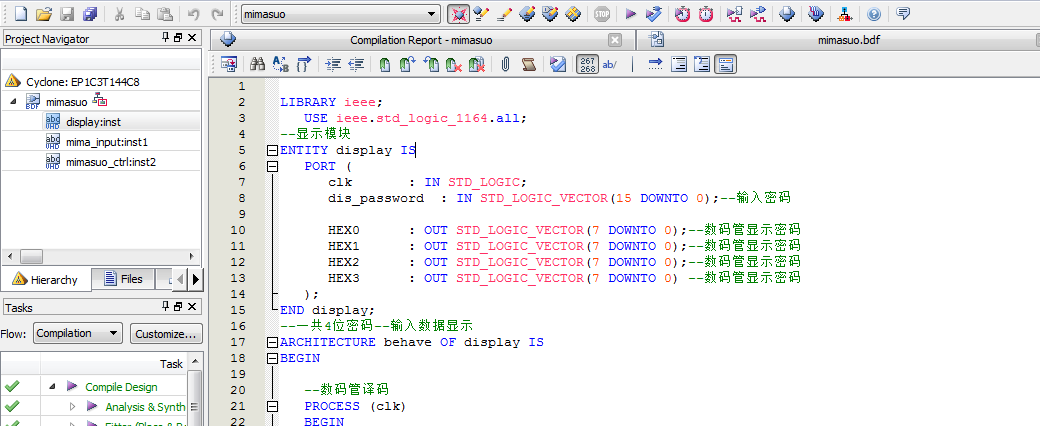

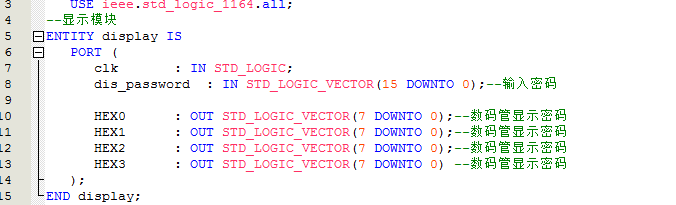

显示模块

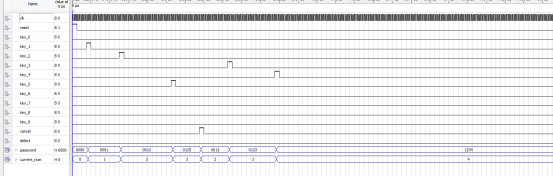

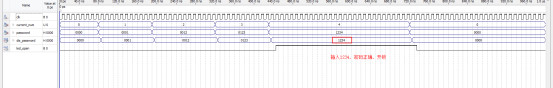

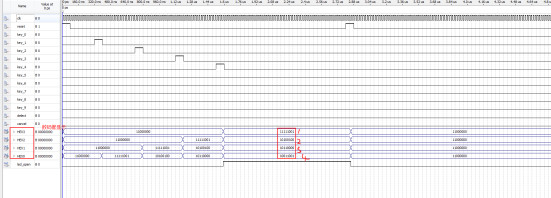

整体仿真

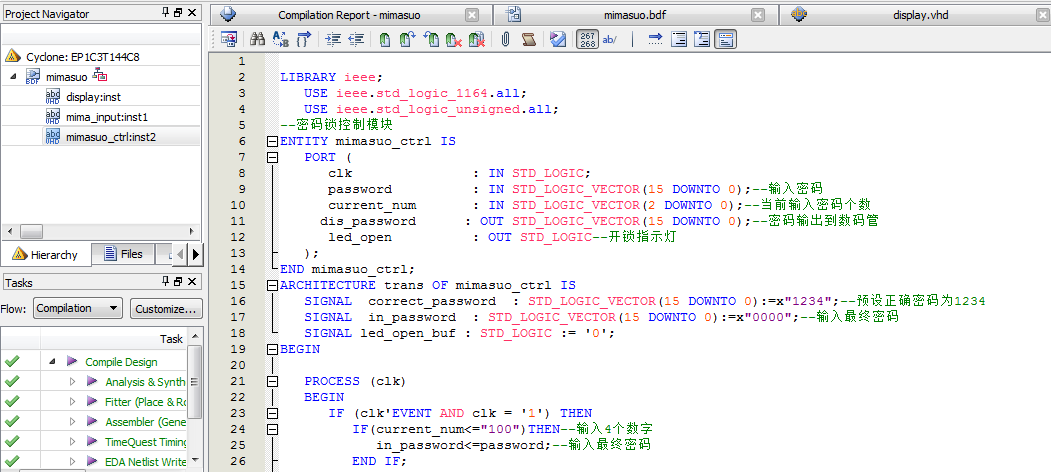

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --密码锁控制模块 ENTITY mimasuo_ctrl IS PORT ( clk : IN STD_LOGIC; password : IN STD_LOGIC_VECTOR(15 DOWNTO 0);--输入密码 current_num : IN STD_LOGIC_VECTOR(2 DOWNTO 0);--当前输入密码个数 dis_password : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);--密码输出到数码管 led_open : OUT STD_LOGIC--开锁指示灯 ); END mimasuo_ctrl; ARCHITECTURE trans OF mimasuo_ctrl IS SIGNAL correct_password : STD_LOGIC_VECTOR(15 DOWNTO 0):=x"1234";--预设正确密码为1234 SIGNAL in_password : STD_LOGIC_VECTOR(15 DOWNTO 0):=x"0000";--输入最终密码 SIGNAL led_open_buf : STD_LOGIC := '0'; BEGIN PROCESS (clk) BEGIN IF (clk'EVENT AND clk = '1') THEN IF(current_num<="100")THEN--输入4个数字 in_password<=password;--输入最终密码 END IF; END IF; END PROCESS; dis_password<=in_password; --控制开锁指示灯 PROCESS (clk) BEGIN IF (clk'EVENT AND clk = '1') THEN IF (in_password = correct_password) THEN led_open_buf <= '1';--高电平表示开锁 ELSE led_open_buf <= '0'; END IF; END IF; END PROCESS; led_open <= led_open_buf;--输出开锁指示灯 END trans;

源代码

扫描文章末尾的公众号二维码

9759

9759

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?