名称:基于FPGA的数字电子钟设计Verilog代码Quartus仿真

软件:Quartus

语言:Verilog

代码功能:

设计要求

基于模块化的设计思想,采用 Verilog HDL语言设计一个能进行时、分、秒计时的二十四小时制的数字电子钟,并具有整点报时功能。采用数码管进

行时间显示,要求显示格式为:小时-分钟-秒钟

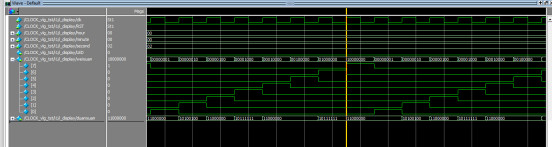

在EDA软件中完成数字电子钟的源代码设计,并进行仿真,仿真结果要能够体现出时、分、秒各自的跳变过程,并且能够给出整点报时控制信号的变

1、独立完成设计任务

2、详细阐述设计方案,绘制系统设计框图;

3、详细阐述系统调试方案,编写测试文件并进行仿真

4、撰写设计报告。详细阐述设计思想、指标论证、方案确定、结果分析等内容,并对所完成的设计做出总结和评价,对设计过程中遇到的问题及解

决方案进行记录并分析。

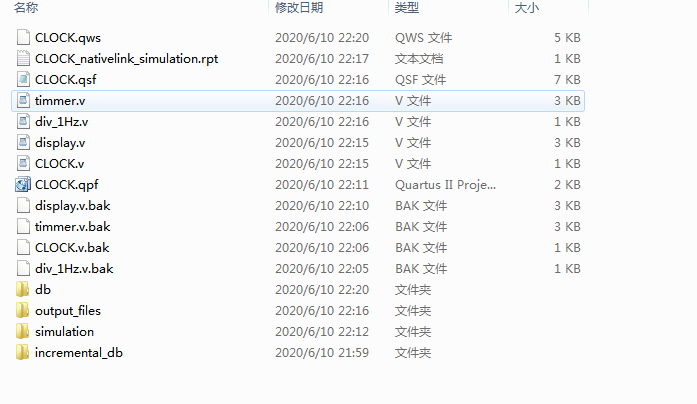

1. 工程文件

2. 程序文件

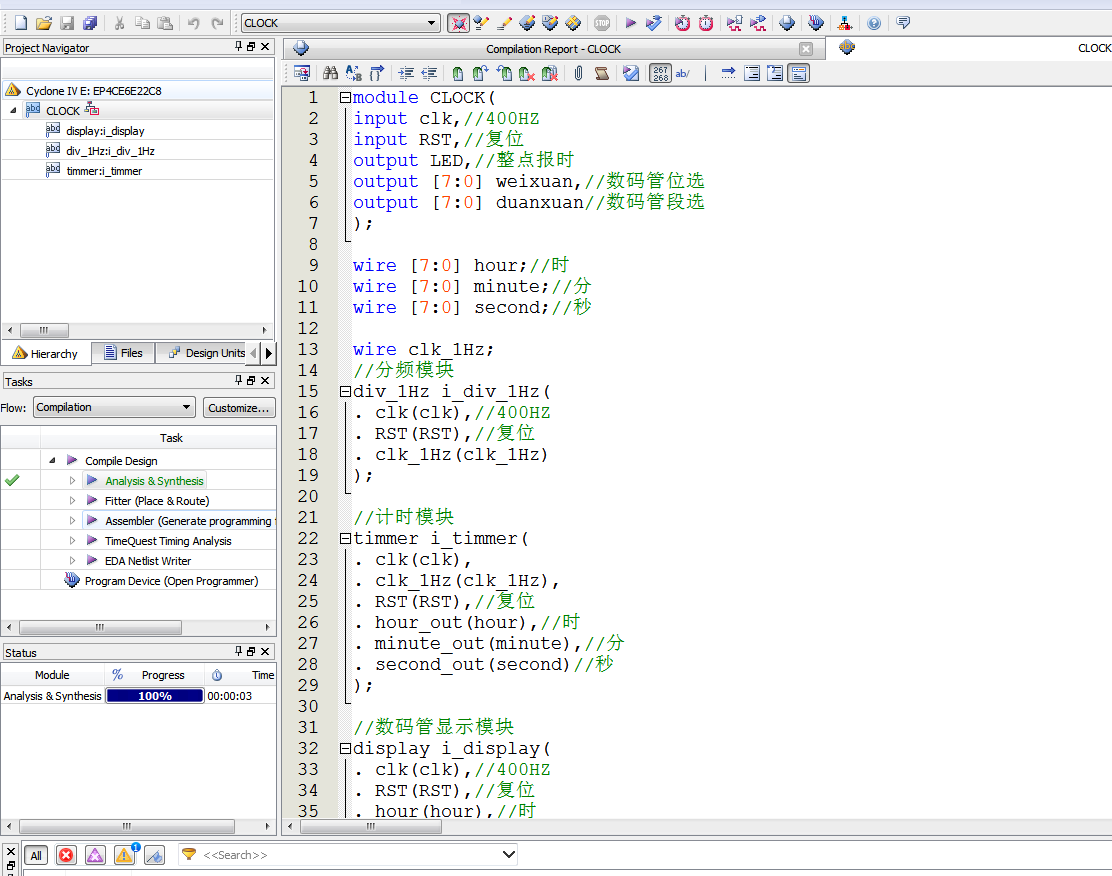

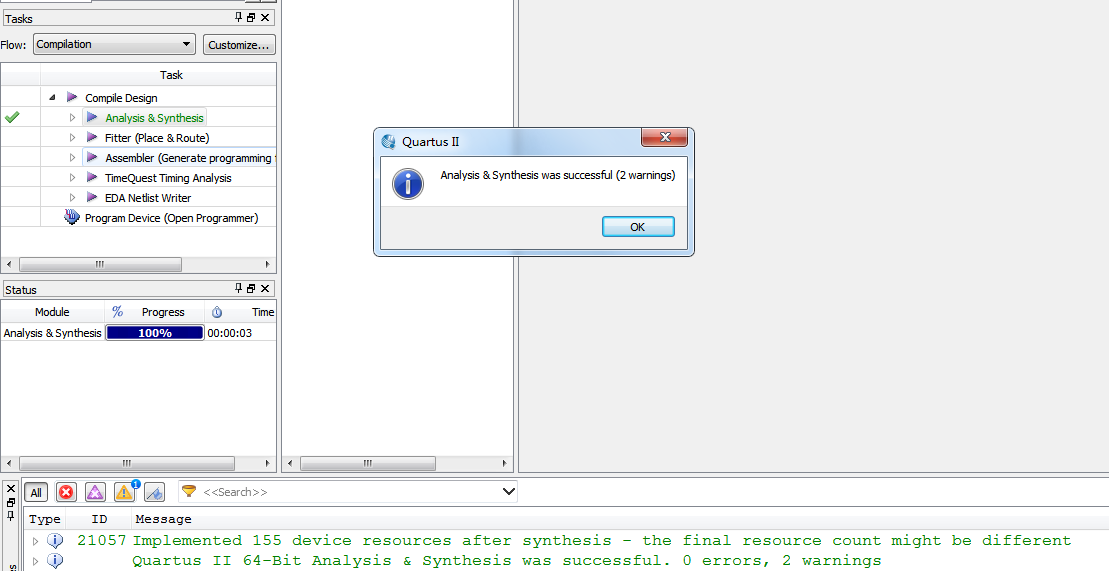

3. 程序编译

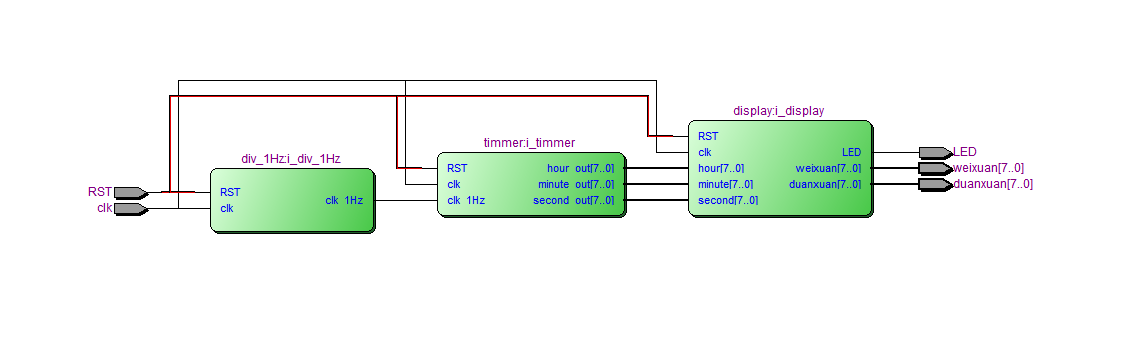

4. RTL图

5. testbench

6. 仿真图

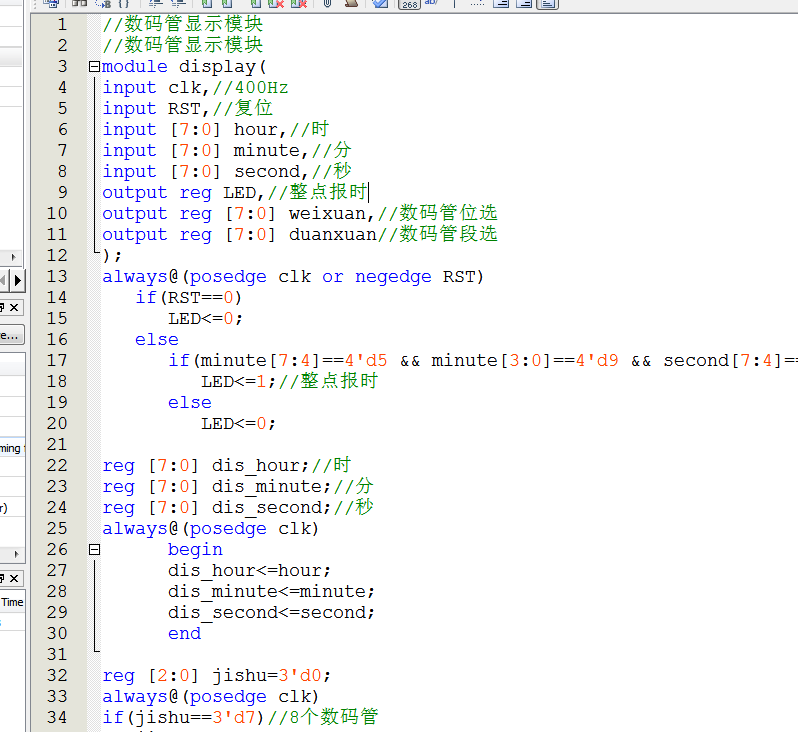

数码管显示模块

分频模块

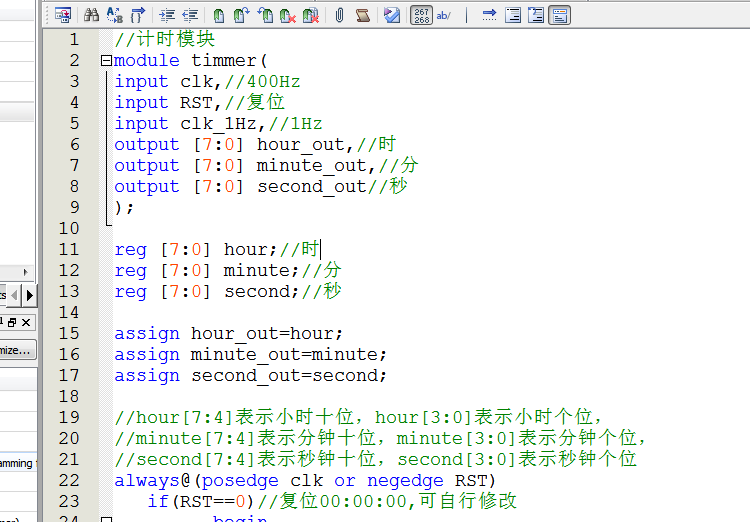

计时模块

部分代码展示:

module CLOCK( input clk,//400HZ input RST,//复位 output LED,//整点报时 output [7:0] weixuan,//数码管位选 output [7:0] duanxuan//数码管段选 ); wire [7:0] hour;//时 wire [7:0] minute;//分 wire [7:0] second;//秒 wire clk_1Hz; //分频模块 div_1Hz i_div_1Hz( . clk(clk),//400HZ . RST(RST),//复位 . clk_1Hz(clk_1Hz) ); //计时模块 timmer i_timmer( . clk(clk), . clk_1Hz(clk_1Hz), . RST(RST),//复位 . hour_out(hour),//时 . minute_out(minute),//分 . second_out(second)//秒 ); //数码管显示模块 display i_display( . clk(clk),//400HZ . RST(RST),//复位 . hour(hour),//时 . minute(minute),//分 . second(second),//秒 . LED(LED), . weixuan(weixuan),//数码管位选 . duanxuan(duanxuan)//数码管段选 ); endmodule

源代码

扫描文章末尾的公众号二维码

493

493

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?