名称:基于FPGA的cordic IP核设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

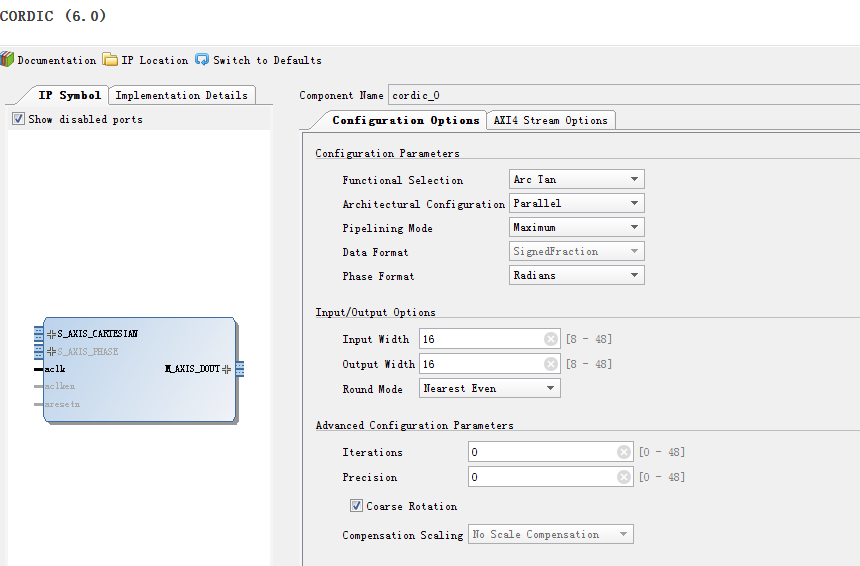

代码功能:cordic IP核设计及仿真

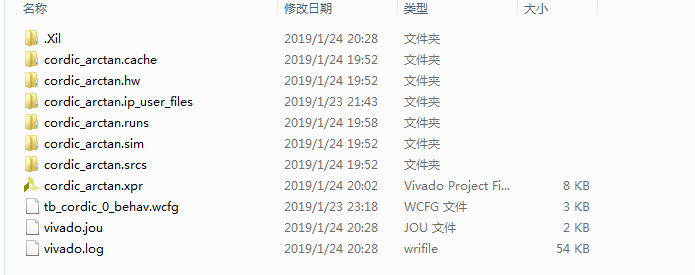

1、工程文件

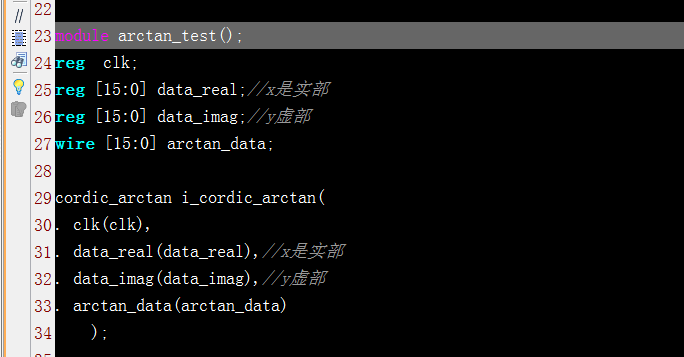

2、程序文件

3、Testbench

4、工程编译

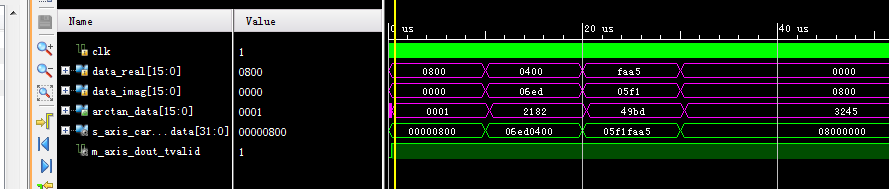

5、程序仿真

Input:x+y*i

求arctan(y,x)

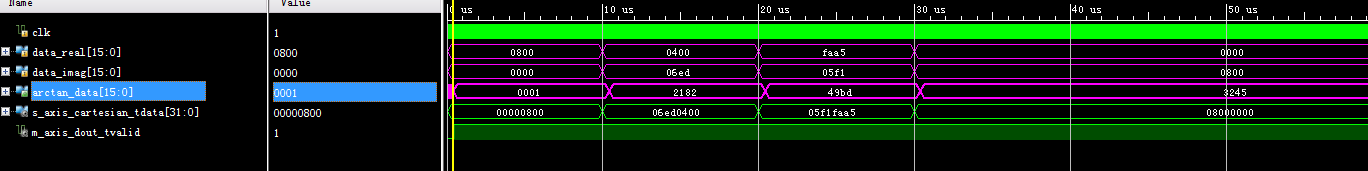

仿真图分析:

1.

输入数据格式:第1位为符号位,第2位为整数位,其余为小数位

输出数据格式:第1位为符号位,第2、3位为整数位,其余为小数位

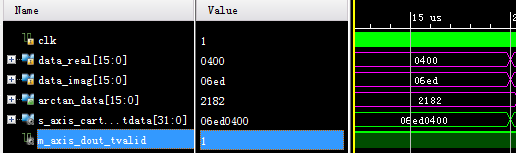

实部x=16’h0400=0000010000000000=00.00010000000000=0.0625

虚部y=16’h06ed=0000011011101101=00.00011011101101=0.1082

仿真结果arctan_data=16’h2182=0010000110000010=001.0000110000010=1.04712

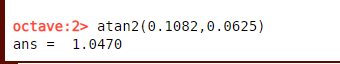

atan2(y,x)是matlab中用于求反正切的函数

使用matlab验证计算如下,与仿真结果一直,计算正确

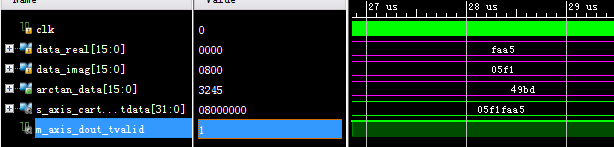

2.

实部x=32’hfaa5=111110*********1=11.11101010100101

实部为负数,取反加1

not(111110*********1)+1=0000010101011011=00.00010101011011=0.08368

故实部x=-0.08368

虚部y=32’h05f1=0000010111110001=00.00010111110001=0.09283

仿真结果arctan_data=16’=010*********

使用matlab验证计算如下,与仿真结果一直,计算正确

![]()

部分代码展示:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2019/01/23 21:40:34

// Design Name:

// Module Name: cordic_arctan

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module cordic_arctan(

input clk,

input [15:0] data_real,//x是实部

input [15:0] data_imag,//y虚部

output [15:0] arctan_data//输出结果

);

// s_axis_cartesian_tdata_real <= s_axis_cartesian_tdata(31 downto 0);

// s_axis_cartesian_tdata_imag <= s_axis_cartesian_tdata(63 downto 32);

// m_axis_dout_tdata_phase <= m_axis_dout_tdata(31 downto 0);

wire [31 : 0] s_axis_cartesian_tdata;

wire s_axis_cartesian_tvalid;

wire m_axis_dout_tvalid;

assign s_axis_cartesian_tdata={data_imag,data_real};//输入,虚部在前,实部在后

assign s_axis_cartesian_tvalid=1;//valid保持为1,即保持有效

//调用cordic

源代码

扫描文章末尾的公众号二维码

6万+

6万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?