名称:基于FPGA的MIPS处理器中32-bit算术逻辑单元(ALU)Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

MIPS处理器中32-bit算术逻辑单元(ALU)

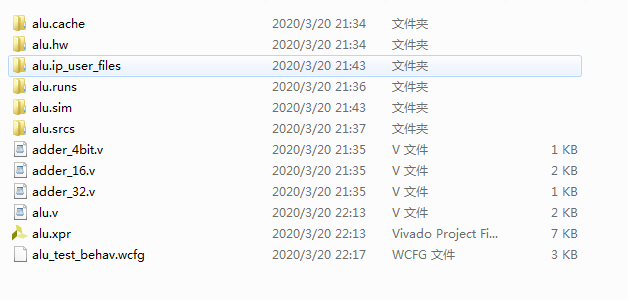

1. 工程文件

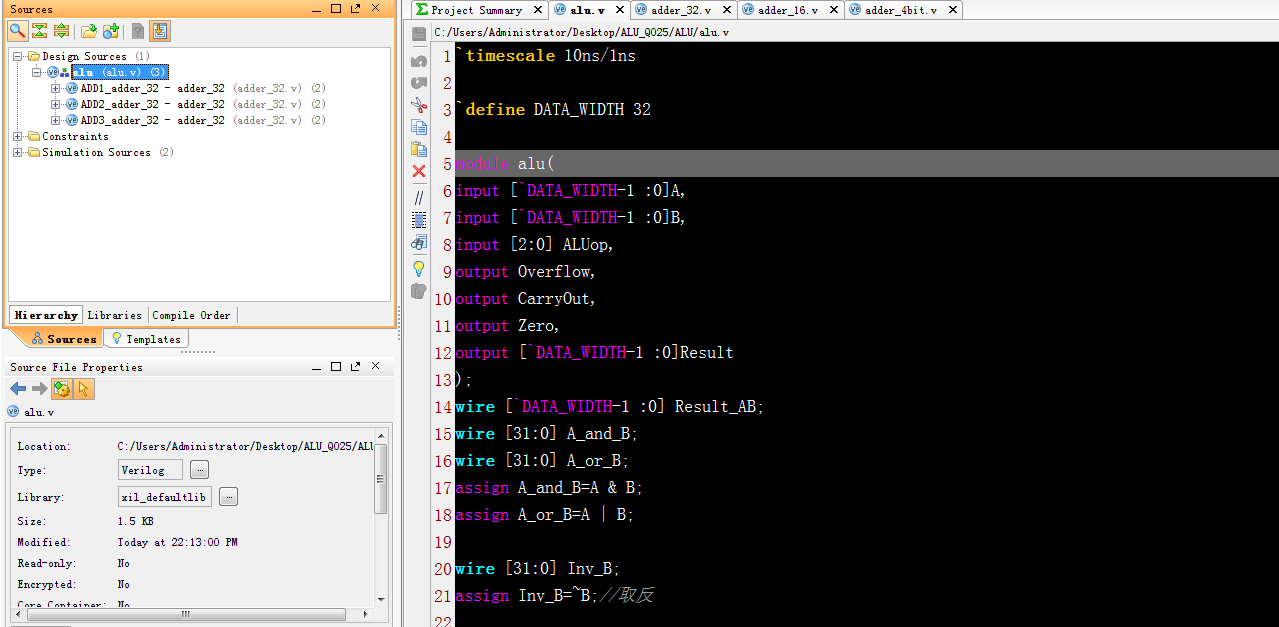

2. 程序文件

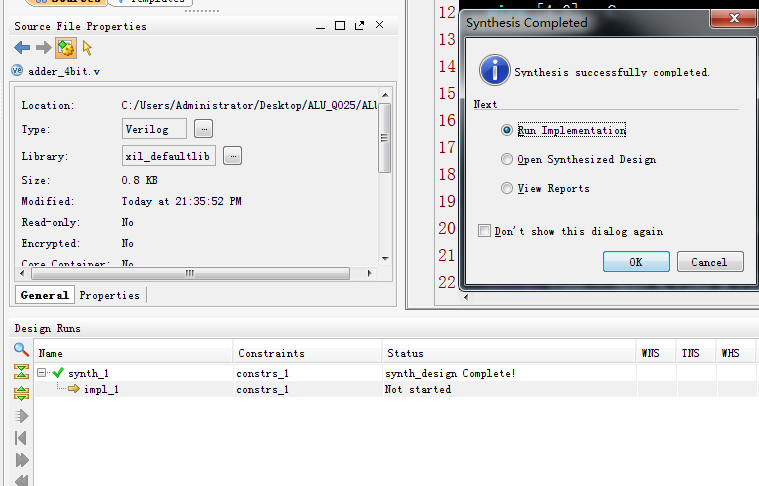

3. 程序编译

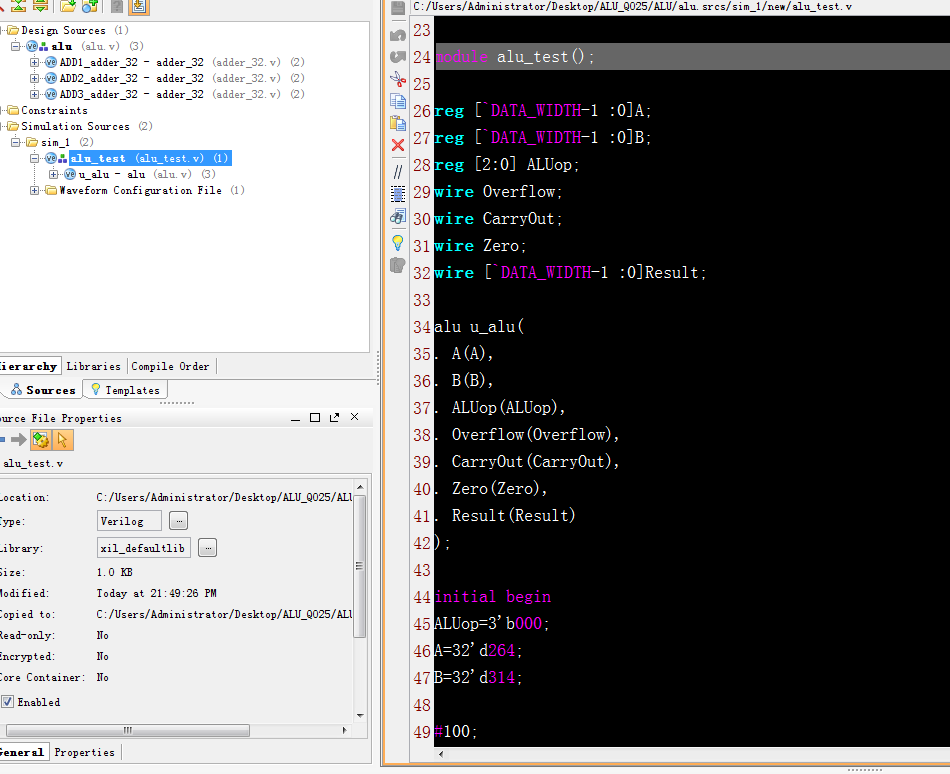

4. Testbench

5. 仿真图

部分代码展示:

`timescale 10ns/1ns `define DATA_WIDTH 32 module alu( input [`DATA_WIDTH-1 :0]A, input [`DATA_WIDTH-1 :0]B, input [2:0] ALUop, output Overflow, output CarryOut, output Zero, output [`DATA_WIDTH-1 :0]Result ); wire [`DATA_WIDTH-1 :0] Result_AB; wire [31:0] A_and_B; wire [31:0] A_or_B; assign A_and_B=A & B; assign A_or_B=A | B; wire [31:0] Inv_B; assign Inv_B=~B;//取反 wire [31:0] sub_B;//取反后加1 //32位加法器 adder_32 ADD1_adder_32( .adder_A(Inv_B), .adder_B(32'd1), //+1 .CIN(1'd0), .COUT(), .S(sub_B) ); wire [31:0] A_add_B; wire [31:0] A_sub_B; wire COUT_add; wire COUT_sub; //32位加法器 adder_32 ADD2_adder_32( .adder_A(A), .adder_B(B), //A+B .CIN(1'd0), .COUT(COUT_add), .S(A_add_B) ); //32位加法器 adder_32 ADD3_adder_32( .adder_A(A), .adder_B(sub_B), //A-B .CIN(1'd0), .COUT(COUT_sub), .S(A_sub_B) );

源代码

扫描文章末尾的公众号二维码

455

455

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?