名称:时序逻辑设计之数字钟实验设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

时序逻辑设计之数字钟实验设计

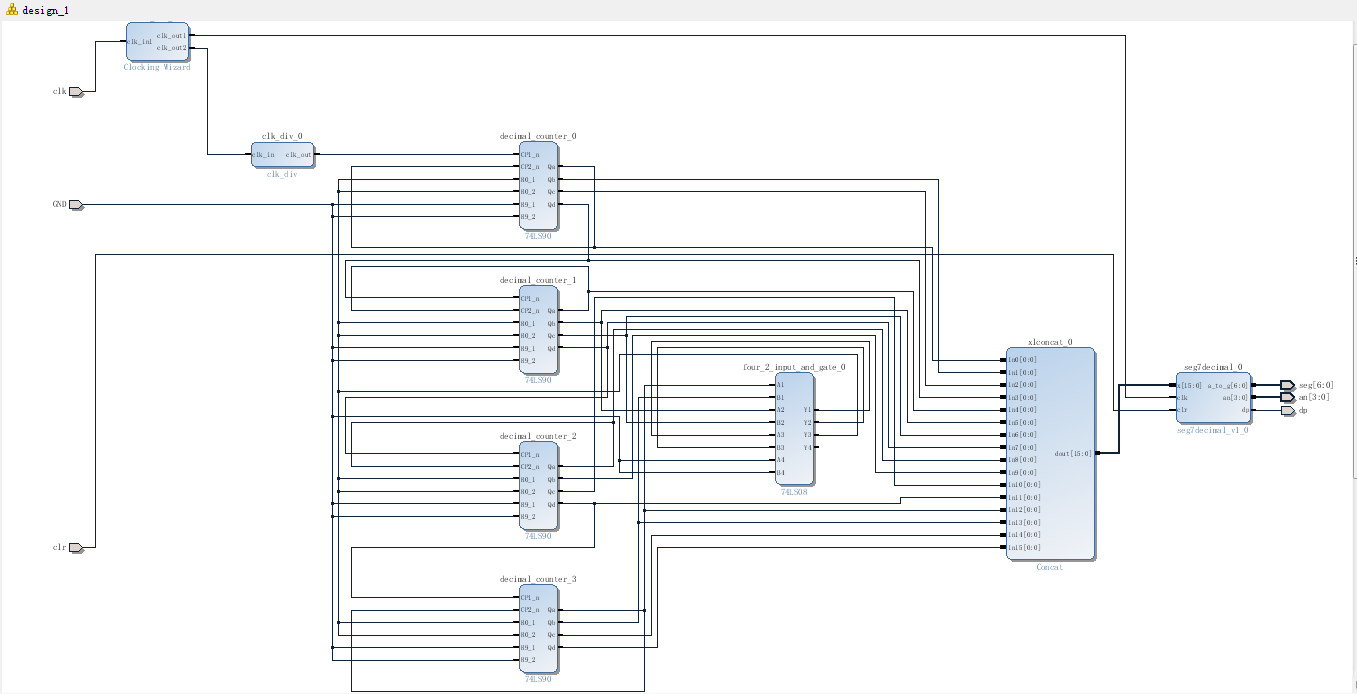

本实验实现了一个简单的数字钟,能实现计时的功能。由于数码管只有4位,因此本数字钟只能计分和秒。

本系统的逻辑部分主要由74系列的P构成。

1. 工程文件

2. 原理图设计

3. 程序编译

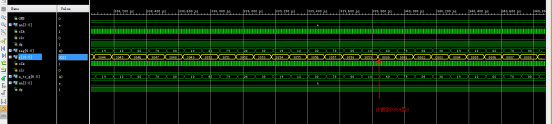

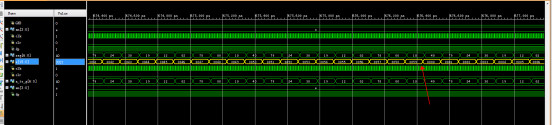

4. 仿真图

注:仿真时将clk_div参数设置为10,上板验证时参数设置为100000000

参数设置

部分代码展示:

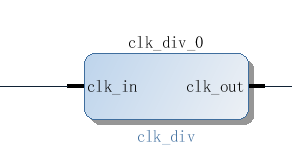

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 2014/10/10 21:49:35 // Design Name: // Module Name: clk_div // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module clk_div #(parameter N = 100000000)( input clk_in, output reg clk_out ); reg [31:0]count; always@(posedge clk_in)begin if(count < N)begin count <= count + 1'b1; clk_out <= 1'b0; end else begin count <= 0; clk_out <= 1'b1; end end endmodule

源代码

点击下方的公众号卡片获取

2058

2058

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?