名称:蔬菜大棚自动控温系统(DS18B20)设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

蔬菜大棚自动控温系统(DS18B20)

1、使用DS18B20作为温度传感器

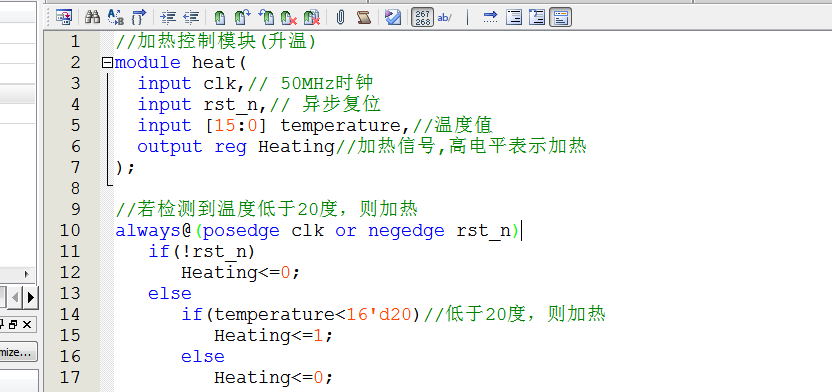

2、若检测到温度低于20度,则加热(电热棒)

3、若检测到温度高于30度,则启动电机(空调压缩机)降温

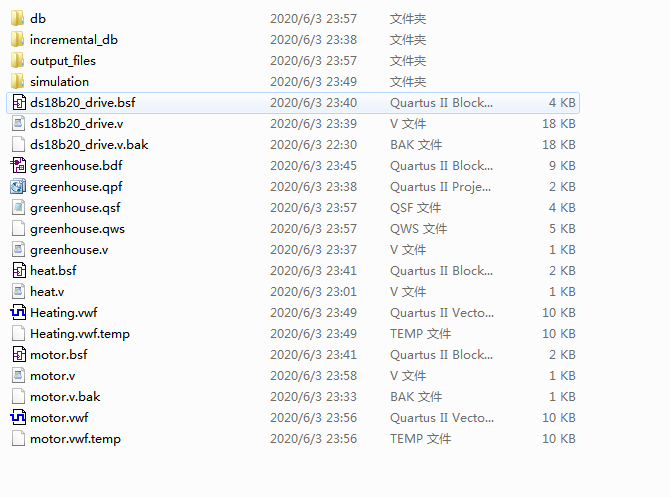

1. 工程文件

2. 程序文件

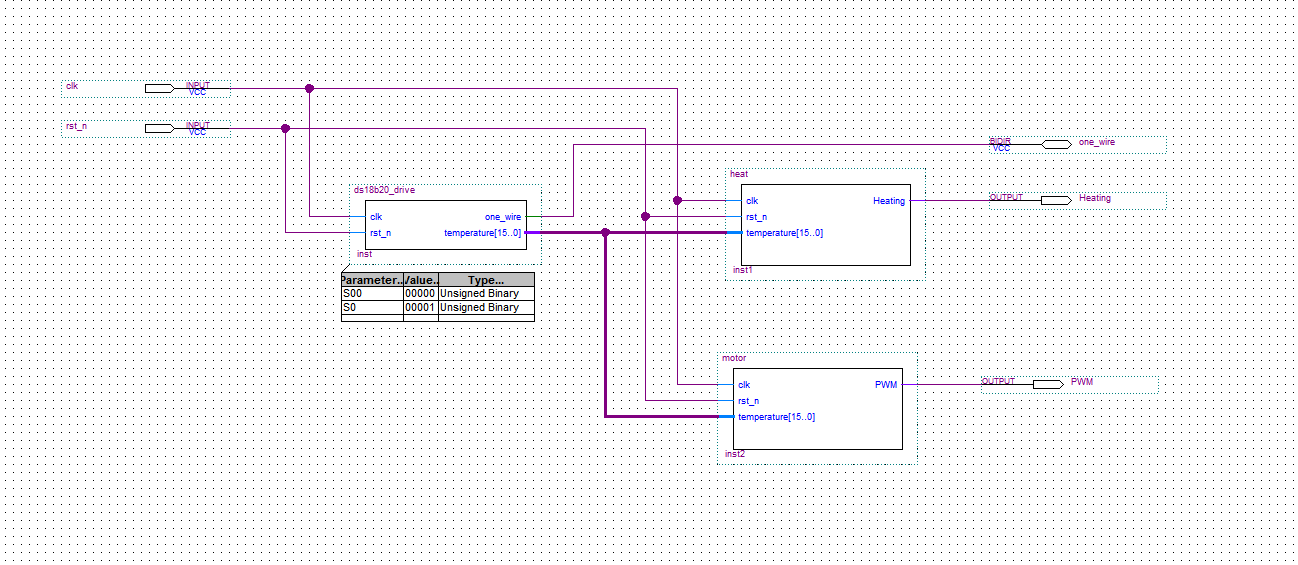

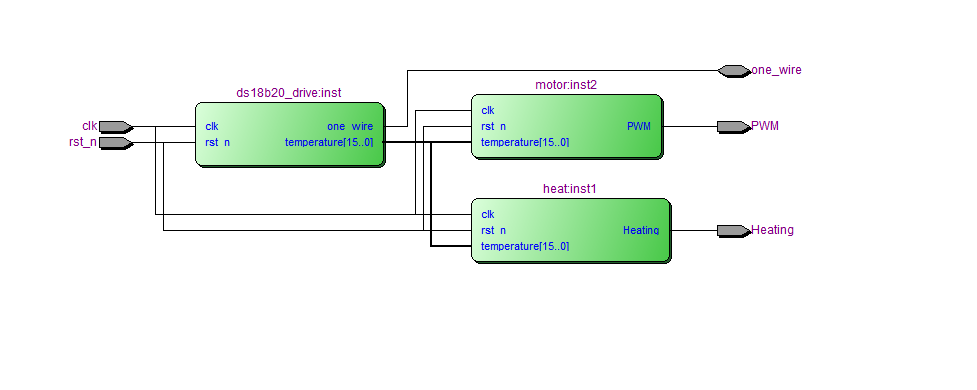

原理图

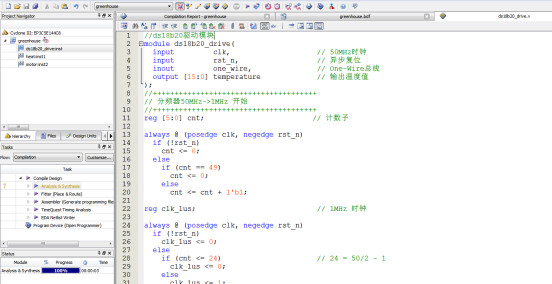

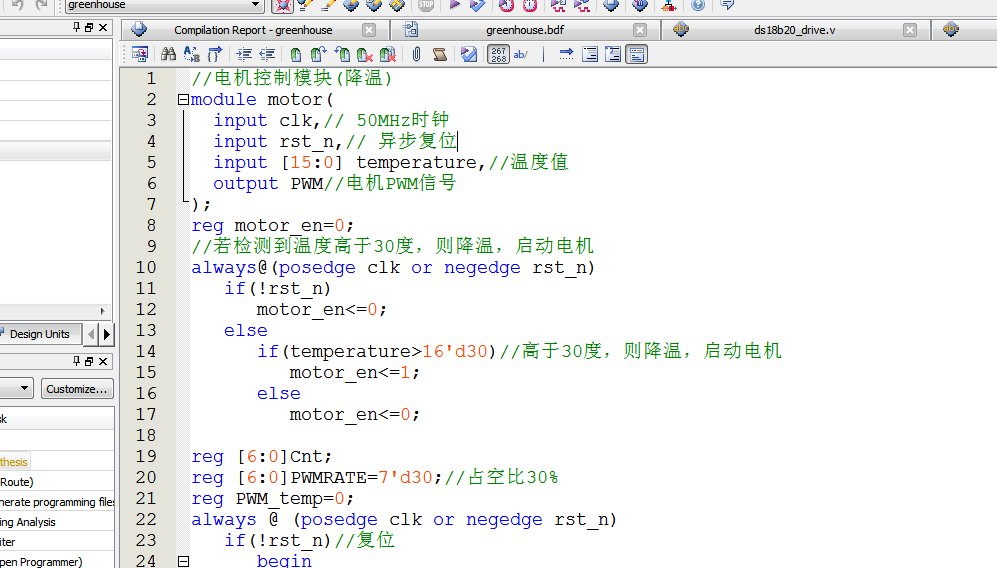

代码

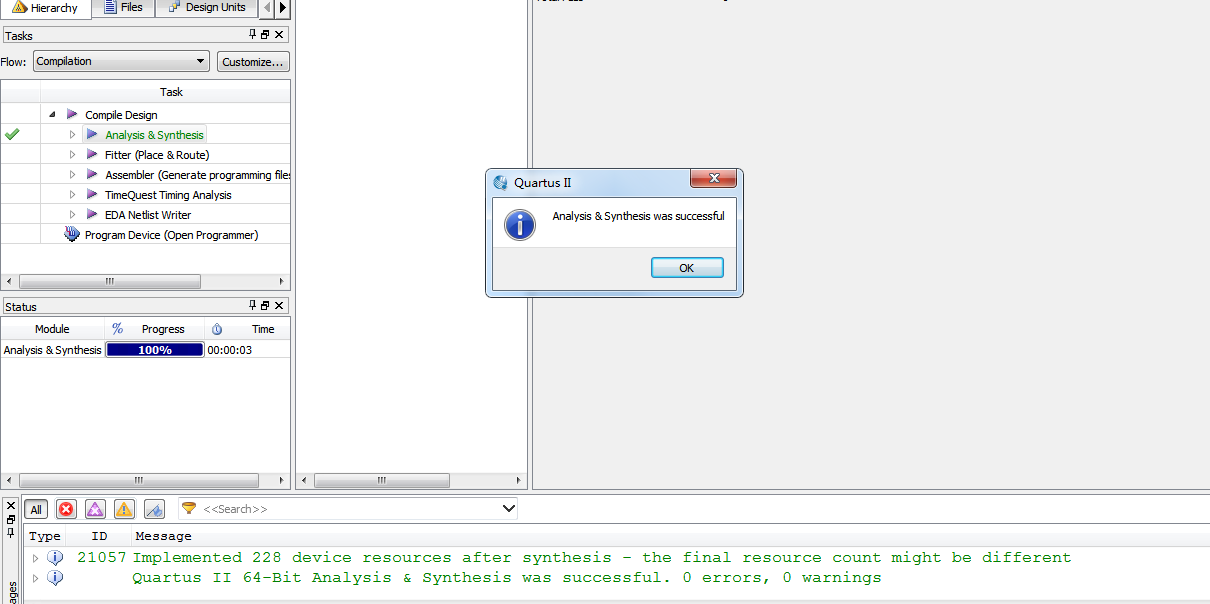

3. 程序编译

4. RTL图

5. 仿真

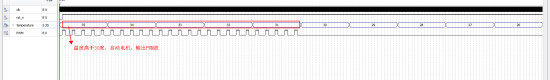

5.1 加热模块仿真

//若检测到温度低于20度,则加热

5.2 电机(PWM)模块仿真

//若检测到温度高于30度,则降温,启动电机

部分代码展示:

//ds18b20驱动模块 module ds18b20_drive( input clk, // 50MHz时钟 input rst_n, // 异步复位 inout one_wire, // One-Wire总线 output [15:0] temperature // 输出温度值 ); //++++++++++++++++++++++++++++++++++++++ // 分频器50MHz->1MHz 开始 //++++++++++++++++++++++++++++++++++++++ reg [5:0] cnt; // 计数子 always @ (posedge clk, negedge rst_n) if (!rst_n) cnt <= 0; else if (cnt == 49) cnt <= 0; else cnt <= cnt + 1'b1; reg clk_1us; // 1MHz 时钟 always @ (posedge clk, negedge rst_n) if (!rst_n) clk_1us <= 0; else if (cnt <= 24) // 24 = 50/2 - 1 clk_1us <= 0; else clk_1us <= 1; //-------------------------------------- // 分频器50MHz->1MHz 结束 //-------------------------------------- //++++++++++++++++++++++++++++++++++++++ // 延时模块 开始 //++++++++++++++++++++++++++++++++++++++ reg [19:0] cnt_1us; // 1us延时计数子 reg cnt_1us_clear; // 请1us延时计数子 always @ (posedge clk_1us) if (cnt_1us_clear) cnt_1us <= 0; else cnt_1us <= cnt_1us + 1'b1; //-------------------------------------- // 延时模块 结束 //-------------------------------------- //++++++++++++++++++++++++++++++++++++++ // DS18B20状态机 开始 //++++++++++++++++++++++++++++++++++++++ //++++++++++++++++++++++++++++++++++++++ // 格雷码 parameter S00 = 5'h00; parameter S0 = 5'h01; parameter S1 = 5'h03; parameter S2 = 5'h02; parameter S3 = 5'h06; parameter S4 = 5'h07; parameter S5 = 5'h05; parameter S6 = 5'h04; parameter S7 = 5'h0C; parameter WRITE0 = 5'h0D; parameter WRITE1 = 5'h0F; parameter WRITE00 = 5'h0E; parameter WRITE01 = 5'h0A; parameter READ0 = 5'h0B; parameter READ1 = 5'h09; parameter READ2 = 5'h08; parameter READ3 = 5'h18;

源代码

点击下方的公众号卡片获取

559

559

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?