名称:格雷码译码器及伪随机序列发生器设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

设计一个输入8位格雷码输出8位(bit)二进制码的译码器,,(输入G7-G0并行8位,输出:B7--B0并行8位,提示:B(7)=G(7)其它:B(i)B(i+1)xorg(i)

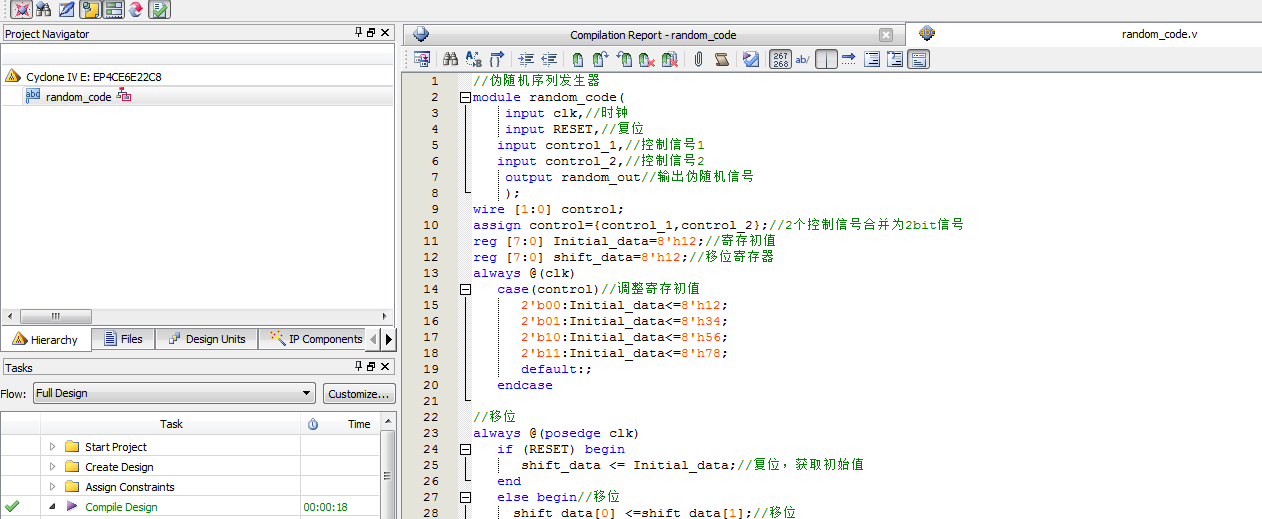

设计一个伪随机序列发生器,采用的生成多项式为1+X3+X7。要求具有个 RESET端和两个控制端来调整寄存器初值(程序中设定好四种非零初值可选)

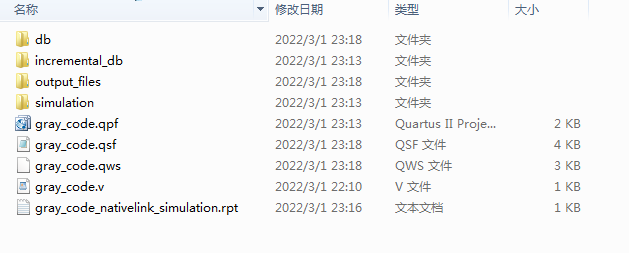

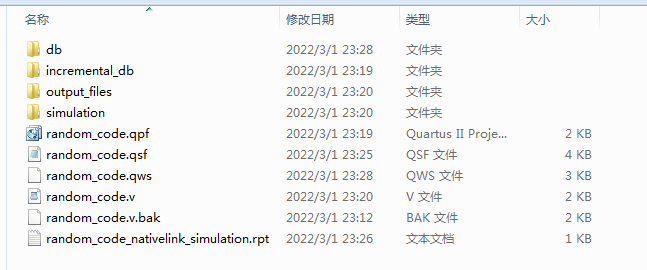

1. 工程文件

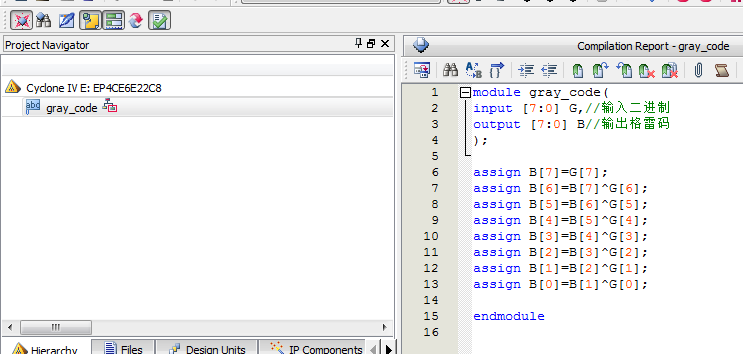

2. 程序文件

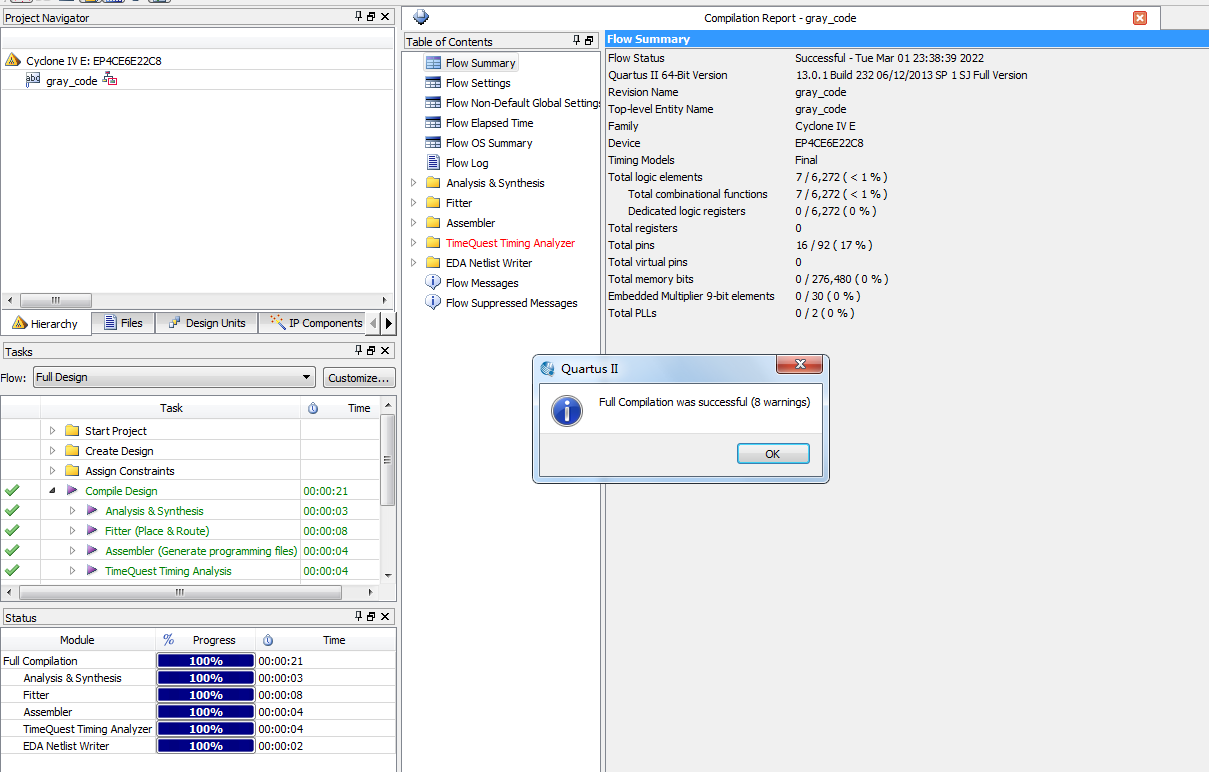

3. 程序编译

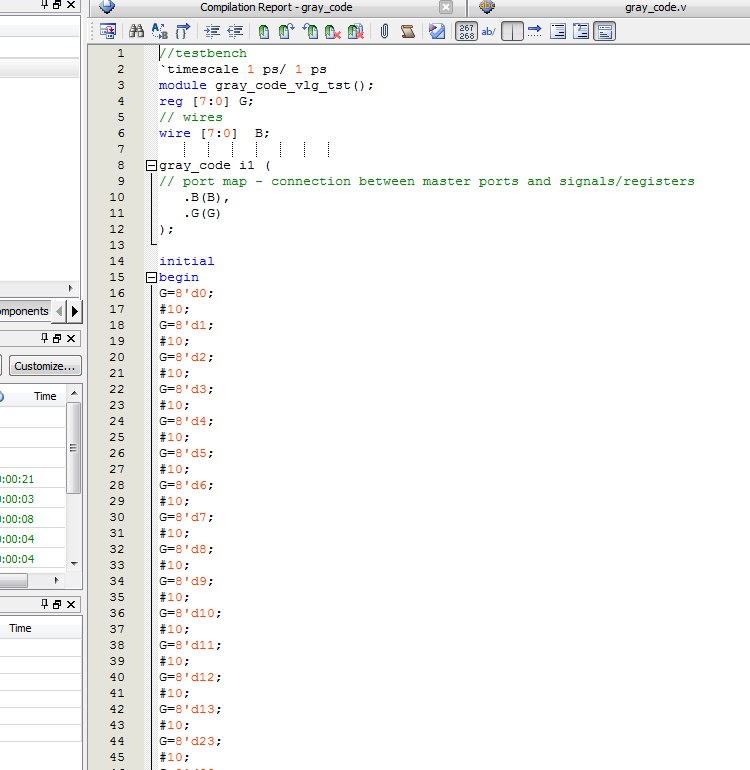

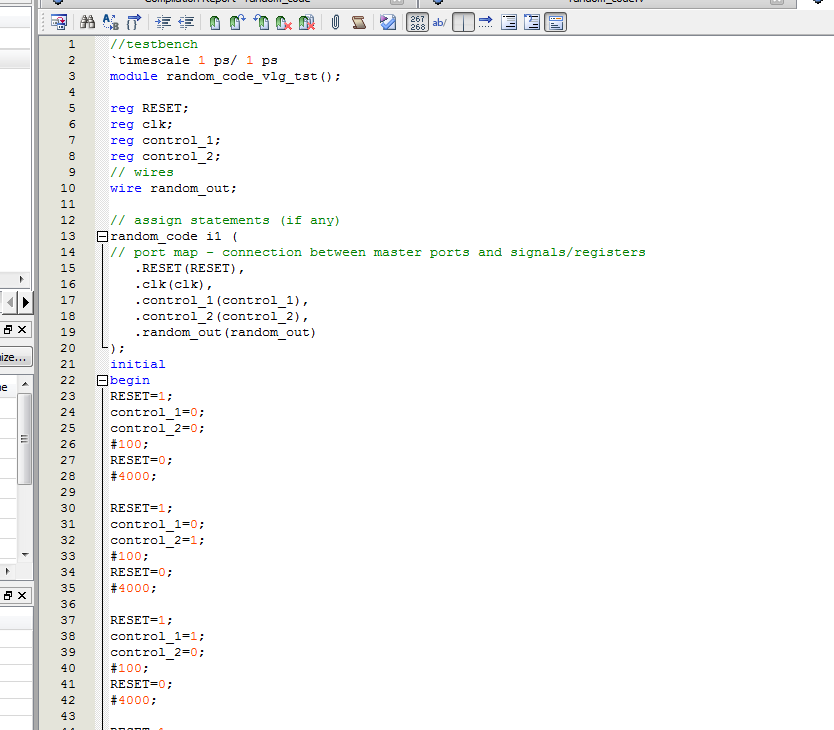

4. Testbench

5. 仿真图

1. 工程文件

2. 程序文件

3. 程序编译

4. Testbench

5. 仿真图

部分代码展示:

module gray_code( input [7:0] G,//输入二进制 output [7:0] B//输出格雷码 ); assign B[7]=G[7]; assign B[6]=B[7]^G[6]; assign B[5]=B[6]^G[5]; assign B[4]=B[5]^G[4]; assign B[3]=B[4]^G[3]; assign B[2]=B[3]^G[2]; assign B[1]=B[2]^G[1];

源代码

点击下方的公众号卡片获取

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?