名称:帧同步器设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

帧同步器设计

1、输入1bit的码元信号,具有位同步码使能信号

2、帧头为“1110010”

3、要求输出3组信息码,其中信息码1为9位,信息码2为8位,信息码3为8位

4、使用quartus 9.0软件版本

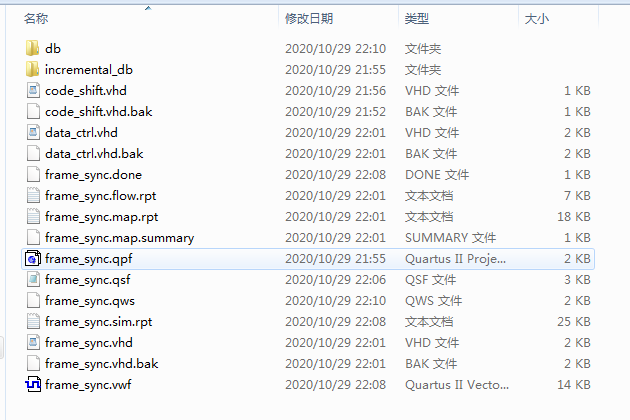

1. 工程文件

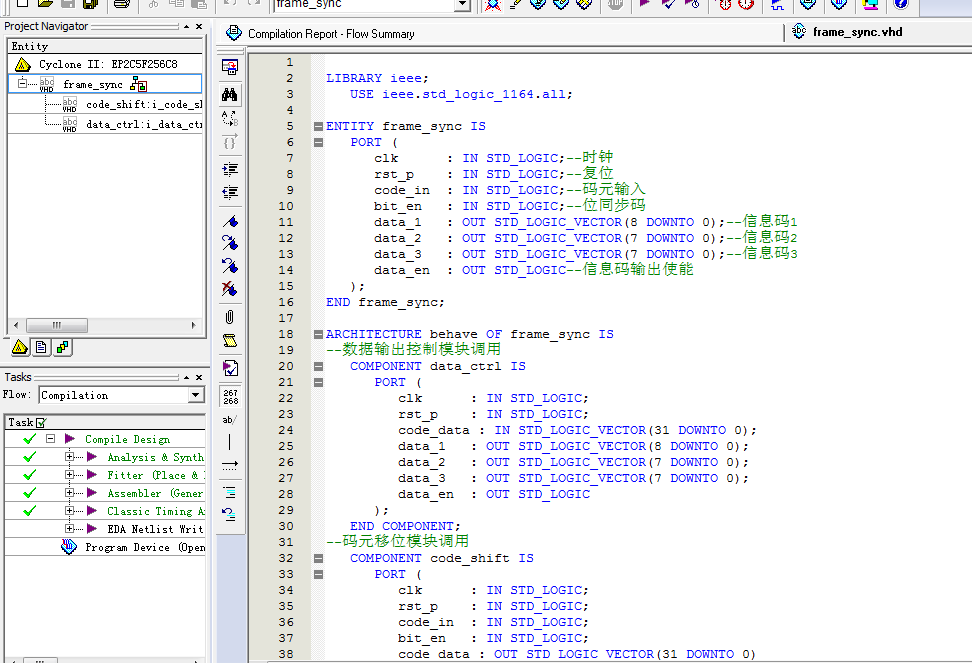

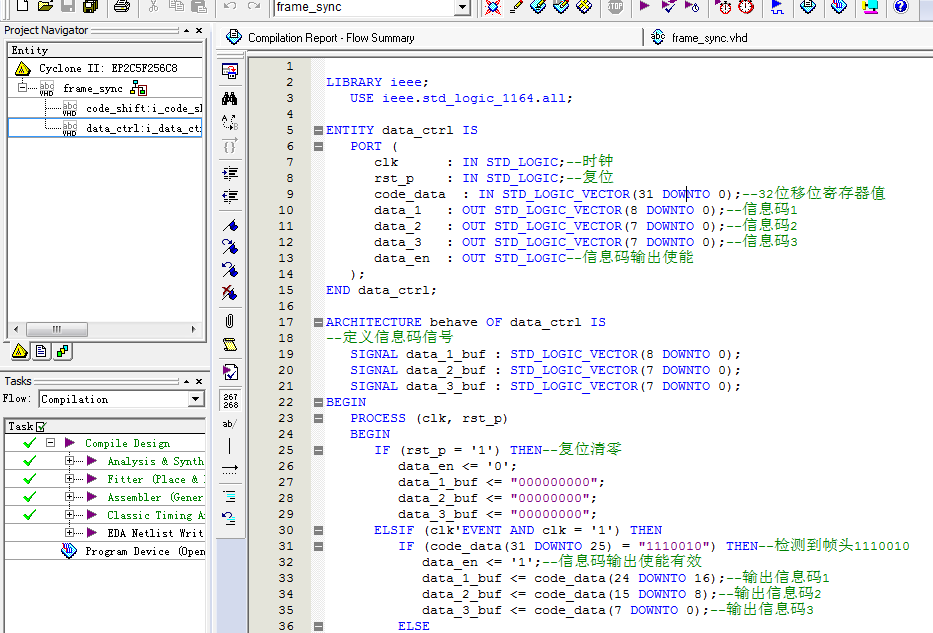

2. 程序文件

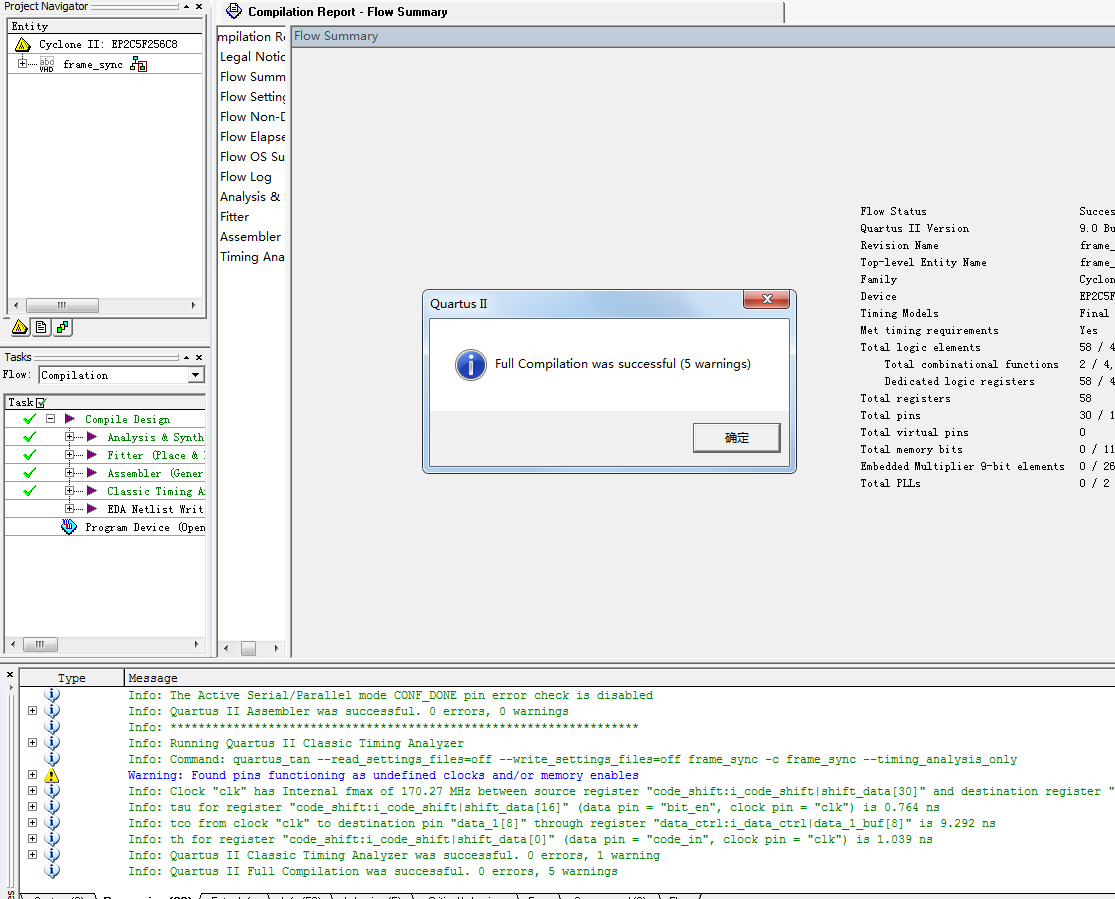

3. 程序编译

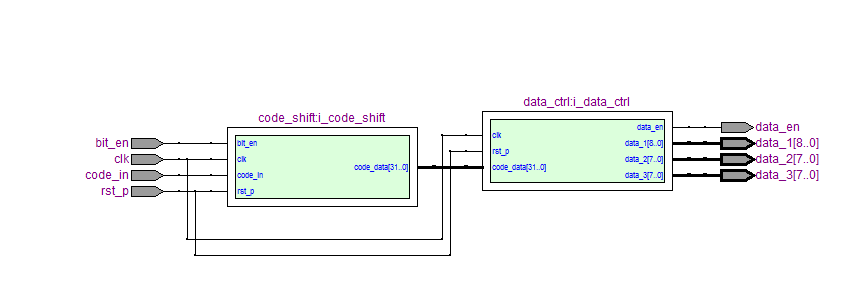

4. RTL图

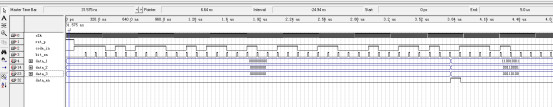

5. 仿真图

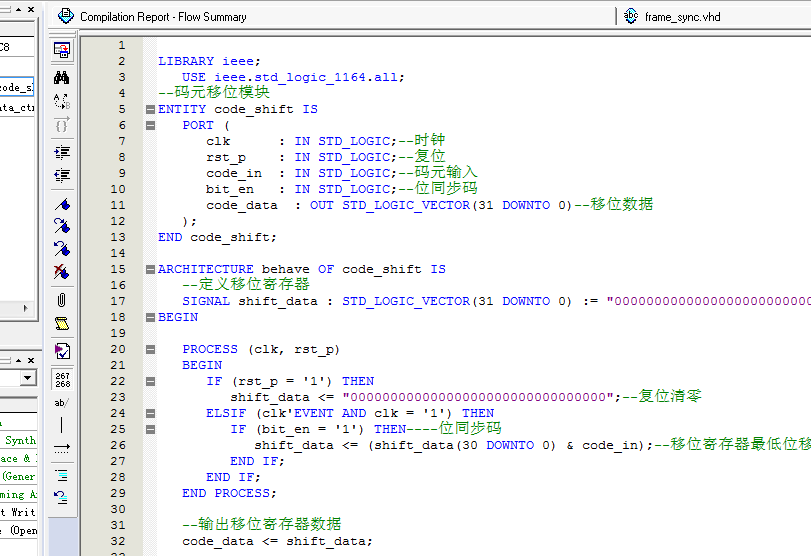

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; --码元移位模块 ENTITY code_shift IS PORT ( clk : IN STD_LOGIC;--时钟 rst_p : IN STD_LOGIC;--复位 code_in : IN STD_LOGIC;--码元输入 bit_en : IN STD_LOGIC;--位同步码 code_data : OUT STD_LOGIC_VECTOR(31 DOWNTO 0)--移位数据 ); END code_shift; ARCHITECTURE behave OF code_shift IS --定义移位寄存器 SIGNAL shift_data : STD_LOGIC_VECTOR(31 DOWNTO 0) := "00000000000000000000000000000000"; BEGIN PROCESS (clk, rst_p) BEGIN IF (rst_p = '1') THEN shift_data <= "00000000000000000000000000000000";--复位清零 ELSIF (clk'EVENT AND clk = '1') THEN IF (bit_en = '1') THEN----位同步码 shift_data <= (shift_data(30 DOWNTO 0) & code_in);--移位寄存器最低位移入码元 END IF; END IF; END PROCESS; --输出移位寄存器数据 code_data <= shift_data; END behave;

源代码

点击下方的公众号卡片获取

929

929

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?