名称:简易电子秒表设计Verilog代码Quartus DE2-115开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:

基本功能

⑴ 基本电子秒表具有分、秒、1/10秒显示,具有启动、停止、暂停、归零四个按键;

⑵ 当秒表归零后,按动启动键,秒表开始计时;之后按动停止键,秒表停止,显示器显示停止时刻时间;若开始计时后,按动暂停键,秒表停止,显示器显示暂停时刻时间,再次按动暂停键,秒表继续计时;

⑶ 倒计时功能:秒表归零后,按动倒计时置数键后,手动设置倒计时时长分和秒。设置结束后,按动启动键,开始倒计时,倒计时结束后,发出提示音,提示音时长自定;

本代码已在DE2-115开发板验证,DE2-115开发板如下,其他开发板可以修改管脚适配:

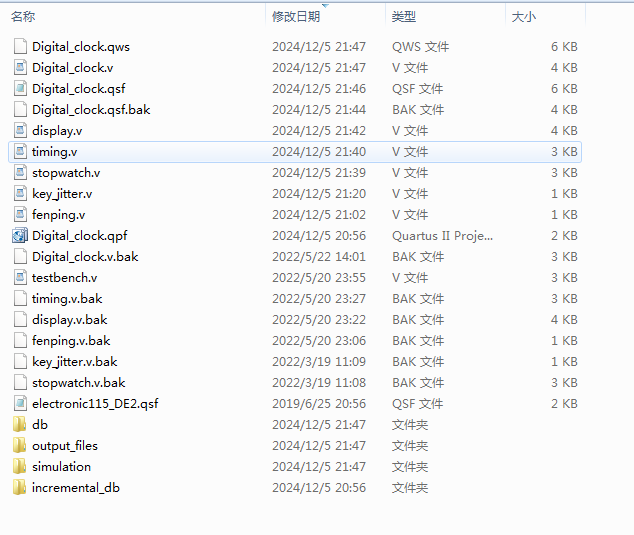

1、工程文件

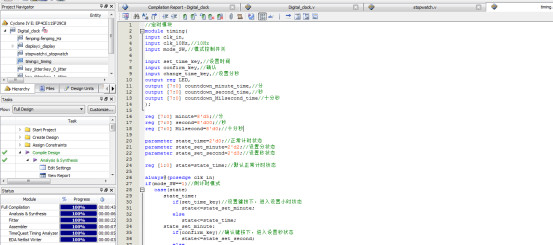

2、程序文件

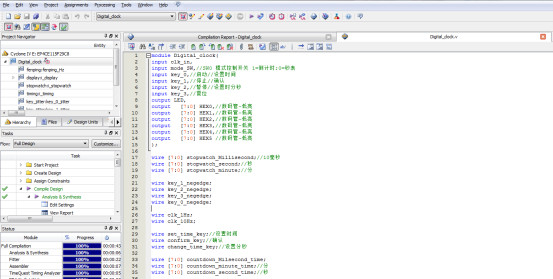

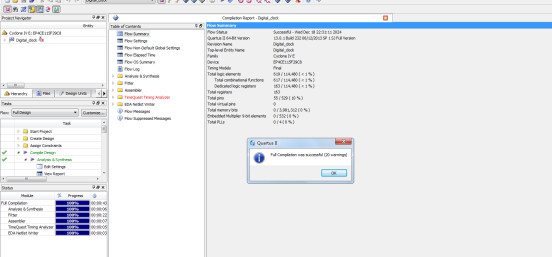

3、程序编译

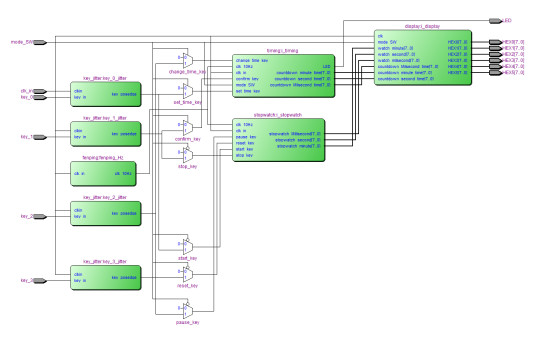

4、RTL图

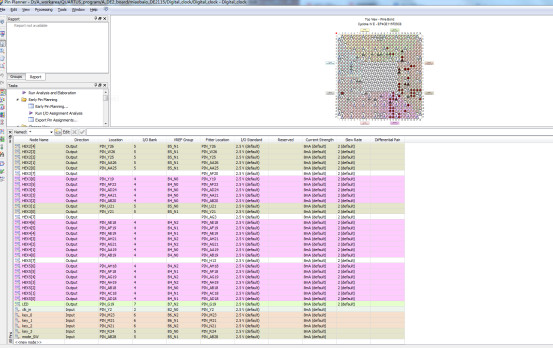

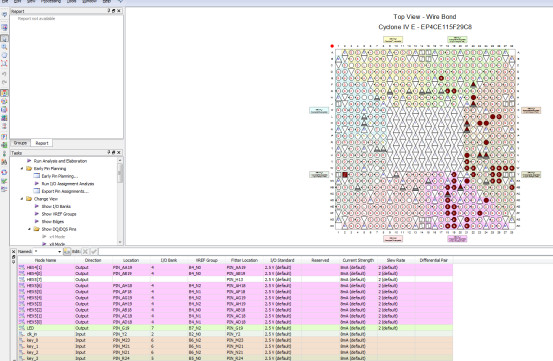

5、管脚分配

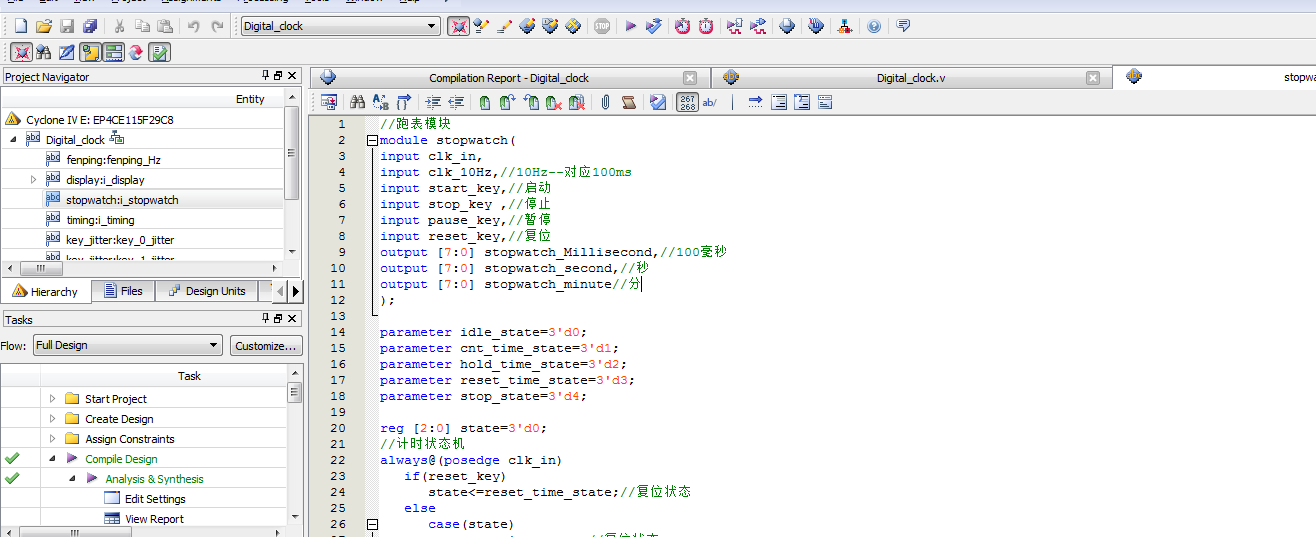

部分代码展示:

module Digital_clock( input clk_in, input mode_SW,//SW0 模式控制开关 1=倒计时;0=秒表 input key_0,//启动//设置时间 input key_1,//停止//确认 input key_2,//暂停//设置时分秒 input key_3,//复位 output LED, output [7:0] HEX0,//数码管-低亮 output [7:0] HEX1,//数码管-低亮 output [7:0] HEX2,//数码管-低亮 output [7:0] HEX3,//数码管-低亮 output [7:0] HEX4,//数码管-低亮 output [7:0] HEX5 //数码管-低亮 ); wire [7:0] stopwatch_Millisecond;//10毫秒 wire [7:0] stopwatch_second;//秒 wire [7:0] stopwatch_minute;//分 wire key_1_negedge; wire key_2_negedge; wire key_3_negedge; wire key_0_negedge; wire clk_1Hz; wire clk_10Hz; wire set_time_key;//设置时间 wire confirm_key;//确认 wire change_time_key;//设置分秒 wire [7:0] countdown_Milsecond_time; wire [7:0] countdown_minute_time;//分 wire [7:0] countdown_second_time;//秒 wire start_key;//启动 wire stop_key ;//停止 wire pause_key;//暂停 wire reset_key;//复位

源代码

点击下方的公众号卡片获取

2665

2665

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?