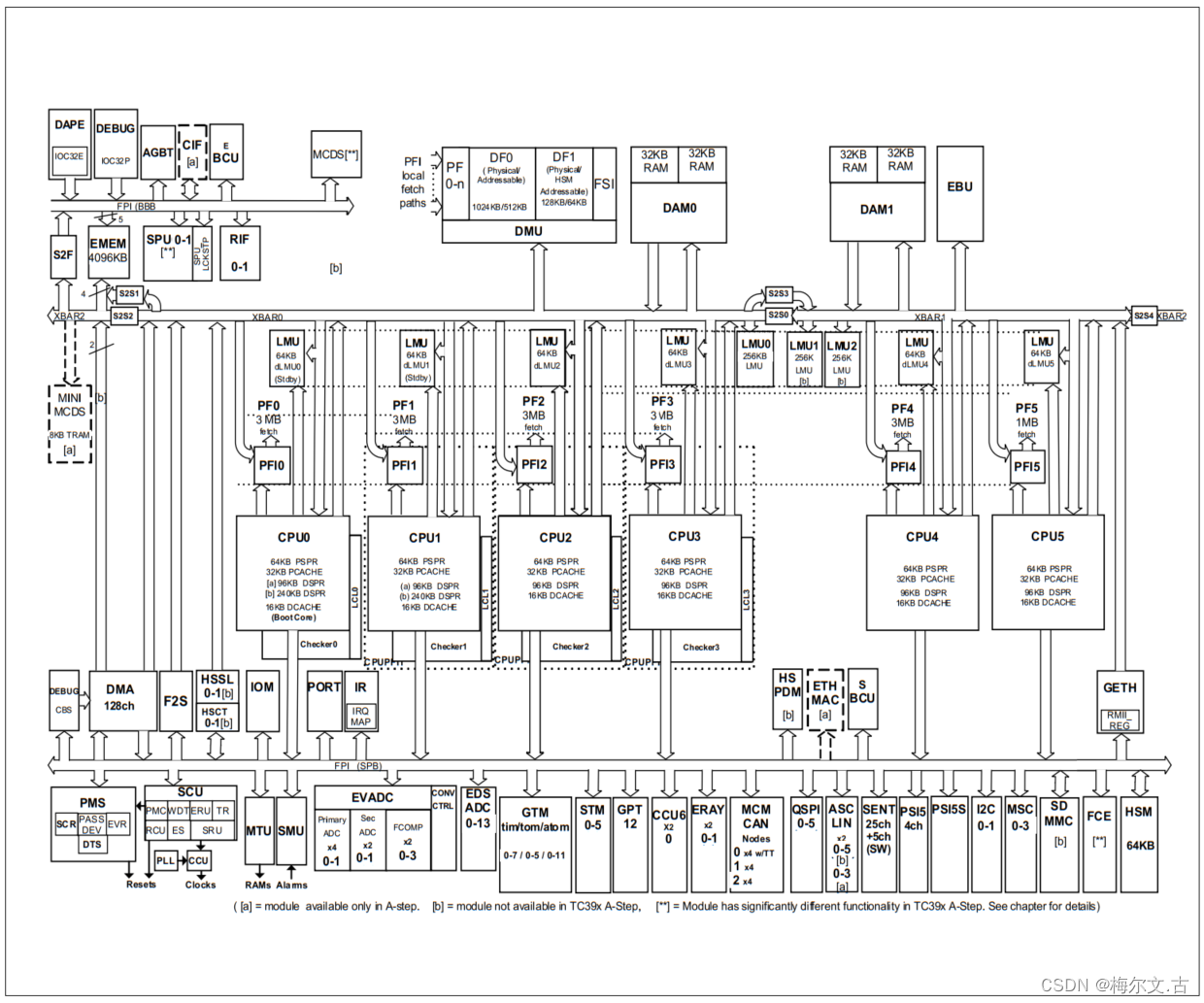

AURIX的芯片手册:

内存

内存在电脑中起着举足轻重的作用。内存一般采用半导体存储单元,包括随机存储器(RAM),只读存储器(ROM),以及高速缓存(CACHE)。

RAM作为主存的主要部分,按其结构分为:

动态随机存取存储器 (Dynamic Random Access Memory,DRAM), 同步动态随机存取内存(synchronous dynamic random-access memory,简称SDRAM), 静态随机存取存储器(Static Random-Access Memory,SRAM)。

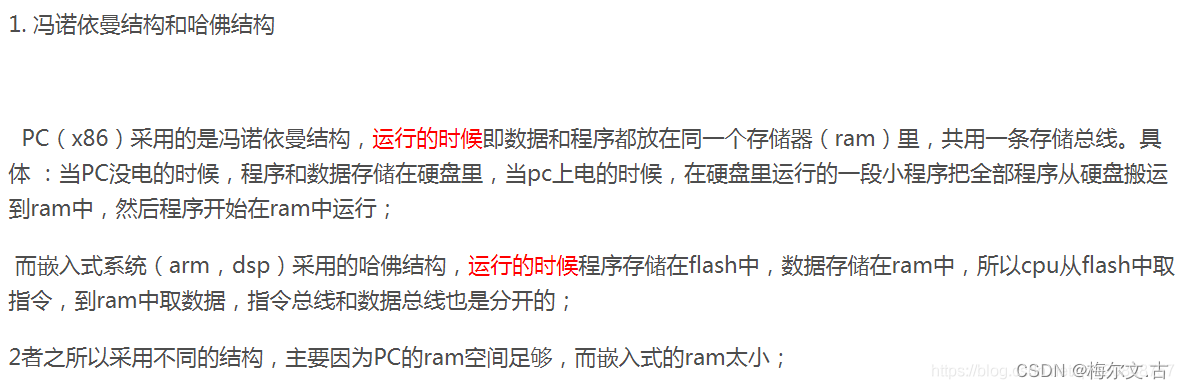

可以理解为FLASH是一个静态的存储【也就是只读存储器(ROM)】,可以用来存储函数或者常量,也就是定义的这部分烧录到芯片里,执行内容不会有改变。即便掉电,里面的数据也不会丢失。

而RAM是一个动态的存储,可以读数据,也可以写数据。RAM可以在运行过程中,可以当flash用。但是如果掉电,RAM里的数据不会保存,一旦掉电,数据就全没了。

举例:一个手机里存着我们很多的数据,如果手机关机,这些数据或者图片是存放在FLASH里的,因为FLASH是存放静态数据的,而当手机重新上电的时候,flash里的数据会通过指令传输到RAM里,之后在被系统里的函数调用,从而开机后,手机可以看到关机前的数据。

缓存:

万字整理内存管理之Cache

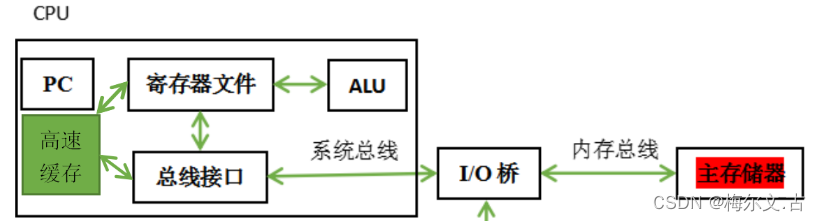

高速缓冲存储器(Cache),是位于CPU与主内存间的一种容量较小但速度很高的存储器:

由于CPU的速度远高于主内存,CPU直接从内存【(RAM)、(ROM)】中存取数据要等待一定时间周期,

文章详细阐述了内存的不同类型,如RAM(动态和静态)、ROM以及CACHE在计算机系统中的作用。AURIX芯片的CPU使用Cache来提升数据访问速度,分为I-Cache(指令Cache)和D-Cache(数据Cache)。启用Cache后,CPU在取指令和数据时会先检查Cache,提高效率;非Cache模式下,CPU直接访问物理地址,速度较慢。文章还探讨了如何通过链接文件调整函数和变量的存储位置。

文章详细阐述了内存的不同类型,如RAM(动态和静态)、ROM以及CACHE在计算机系统中的作用。AURIX芯片的CPU使用Cache来提升数据访问速度,分为I-Cache(指令Cache)和D-Cache(数据Cache)。启用Cache后,CPU在取指令和数据时会先检查Cache,提高效率;非Cache模式下,CPU直接访问物理地址,速度较慢。文章还探讨了如何通过链接文件调整函数和变量的存储位置。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

913

913

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?