XILINX ARTIX-7 FPGA 可以使用GTP 传送最高3G-SDI的信号。本文记录 GTP调用方法,与SDI IP的互联方法等,最后实现1080p60彩条内部产生后经SDI回环后接收,仅适用于ARTIX-7或更高系列。组建工程部分参考赛灵思 xapp1097 实例。

操作概览:

调用GTP IP取出xxx_gt.v和xxx_common.v备用 → 调用3G-SDI IP → 下载 xapp1097.zip → 包装3G-SDI IP → 实现1080p60彩条内部产生后经SDI回环然后接收,使用VIO调试观察接收端锁定情况。

IP说明:

需要调用两个IP:SMPTE SD/HD/3G-SDI 和 7 Series FPGAs Transceivers Wizard(使用GTP)

需要下载一个文件:xapp1097

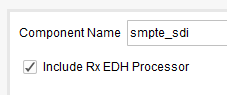

SDI IP 将使用到顶层和以下所有代码(SDI IP须命名为smpte_sdi),使用xapp1097内模块后 SDI IP被包装成名为a7gtp_sdi_rxtx_wrapper.v 的模块。

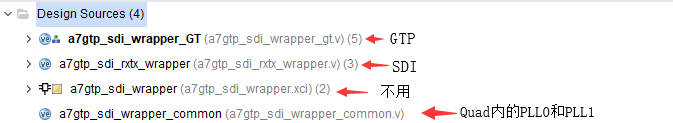

GTP IP 使用 xxx_gt.v作为顶层,其内部包含的.v文件也可以从GTP IP示例工程中获得。xxx_common.v可以从GTP IP 示例工程中获得。

1. 新建一个vivado工程,我使用2017.4版本。添加GT IP核 7 Series FPGAs Transceivers Wizard

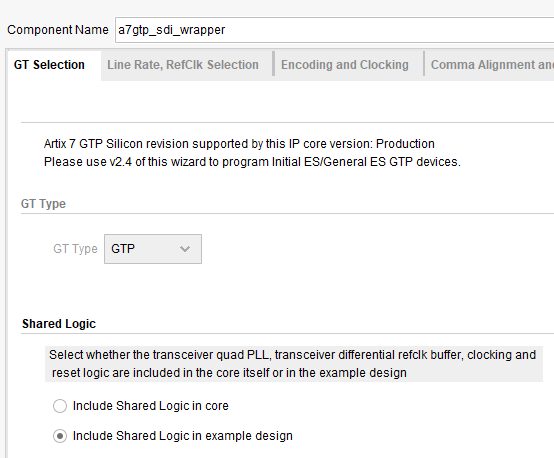

2. IP核命名为 a7gtp_sdi_wrapper,按照下图设置

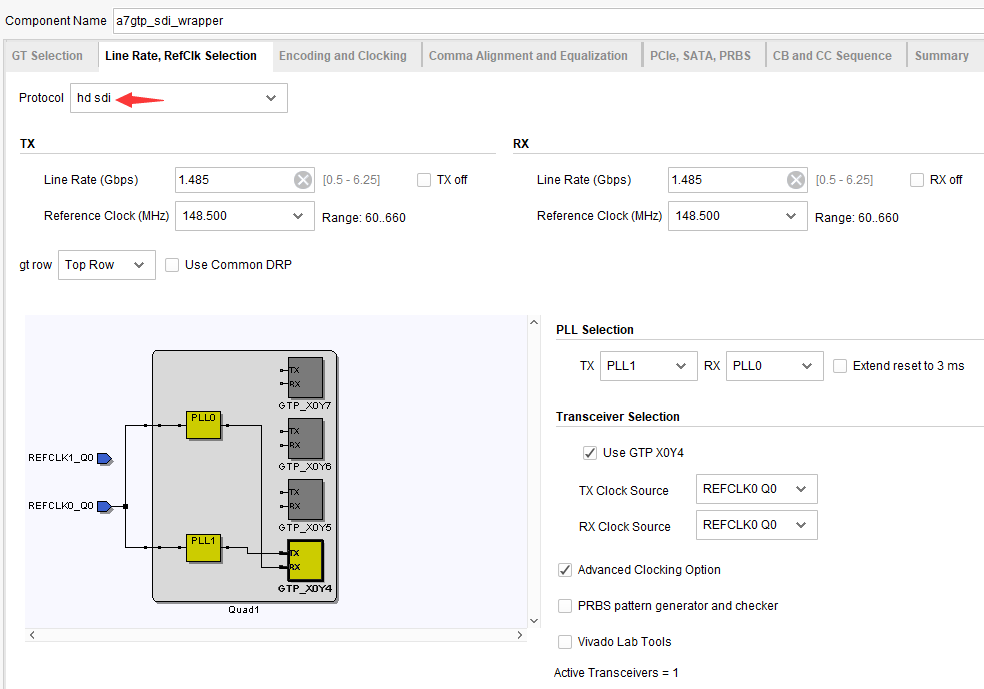

3. 翻到第二页,协议必须选择hd sdi,根据xapp1097即使用3g-sdi也必须选择hd sdi。一个GTP收发器使用两个PLL,确保两个PLL都使能,因为最后的应用需要TX端动态切换两个PLL,由于板子上只有148.5Mhz video OSC只能连接到一个时钟源,因此,不支持发送1.485/1.001 Gb/s HD-SDI和2.97/1.001 Gb/s 3G-SDI。但是,接收端因为有CDR unit,只有148.5Mhz晶振也可以接收5种SDI信号。(按照下图连接时钟源后TX端切换PLL并不能改变频率)

- 270 Mb/s SD-SDI

- 1.485 Gb/s HD-SDI

- 1.485/1.001 Gb/s HD-SDI (不支持发送该比特率除非有148.35 MHz osc)

- 2.97 Gb/s 3G-SDI

- 2.97/1.001 Gb/s 3G-SDI (同上)

按照下图设置,此板连148.5Mhz晶振连接在REFCLK0_Q0上。

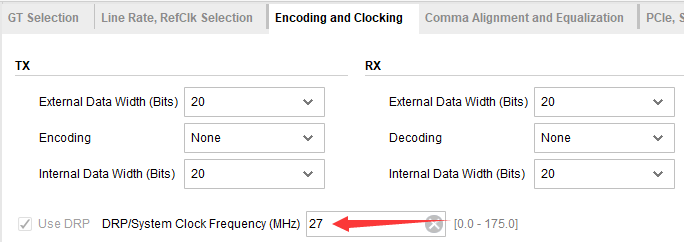

4. 翻到下一页,DRP/system clock freq 设置为27Mhz,该时钟用作SDI IP 和GTP IP辅助时钟,从外部 OSC接入(SDI专用),事实证明 该时钟可以不是精确的27Mhz,也可由内部PLL产生。其他设置默认

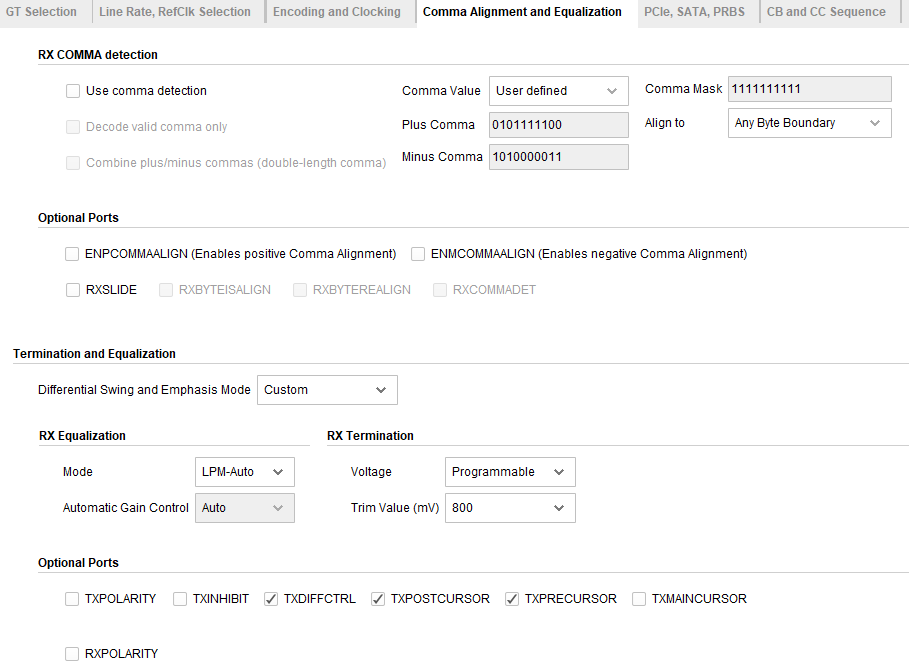

5. 下一页,按照下图设置

6. 下一页,可以勾选LOOPBACK用于调试,注意LOOPBACK是在FPGA内部进行回环,本文其实没有用到。其他默认

7. 其他页默认配置,点OK,generate

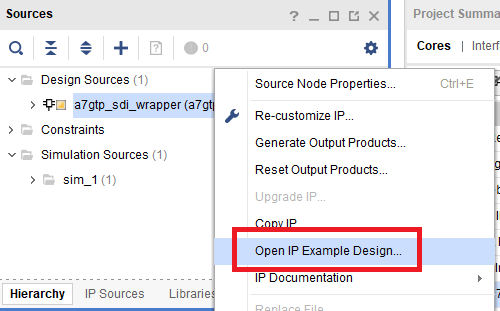

8. 右键打开示例工程,这会在示例工程中产生一个support文件夹,里面一个文件会用到。关闭示例工程

9. 找到示例工程下a7gtp_sdi_wrapper_common.v文件拷贝到原工程下(仅为方便)

cp ./a7gtp_sdi_wrapper_ex/a7gtp_sdi_wrapper_ex.srcs/sources_1/imports/example_design/support/a7gtp_sdi_wrapper_common.v

./sdi.srcs/sources_1/ip/a7gtp_sdi_wrapper

该模块是对2个PLL的封装,一个GTP Quad 中含有2个PLL和4个收发器,一个_common.v 对应一个GTP Quad,可以实例化到多个GTP Quad

10. 将以下文件加入工程

a7gtp_sdi_wrapper_gt.v 下面三个可以从example_design内获得

+-------a7gtp_sdi_wrapper_gtrxreset_seq.v

+-------a7gtp_sdi_wrapper_rxrate_seq.v

+-------a7gtp_sdi_wrapper_sync_block.v

a7gtp_sdi_wrapper_common.v

11. 创建SMPTE SD/HD/3G-SDI IP,必须命名为 smpte_sdi

12. 下载 xapp1097,删除SDI_wrapper内 a7gtp_sdi_rxtx_wrapper_ise.v 然后把以下目录加入工程

./SDI_wrapper

./dru

包含如图

13. 再把 /ac701_sdi_demo内的verilog文件加入,不要chipscope内的。

14. 可以发现新增了两个包装文件。这两个文件需要修改(下图2个“新增”),代码参见。在a7_sdi_rxtx.v中有一个ILA和两个VIO,所以需要手动添加这三个的IP,此处不细讲。

最后包含如上(注意还需要有ILA和VIO)

15. a7gtp_sdi_rxtx_wrapper.v 内的 FXDCLK_FREQ变量设置为DRP/system clock freq。

16. a7_sdi_rxtx.v 包装了SDI信号源、SDI IP以及 GTP的原语,还有一个逻辑分析仪和VIO,VIO用于选择发送模式。顶层ac701_sdi_demo.v包装了a7_sdi_rxtx.v和GTP PLL0/1。顶层内可以实例化两个a7_sdi_rxtx.v,那么约束过后会使用两个收发器。

17. 引脚约束(单个收发器)

set_property IOSTANDARD LVCMOS33 [get_ports clk_27M]

set_property IOSTANDARD LVCMOS33 [get_ports sdi0_sd_hd]

set_property PACKAGE_PIN F6 [get_ports mgtp_refclk0_p]

set_property PACKAGE_PIN B8 [get_ports mgtp_rx0_p]

set_property PACKAGE_PIN B4 [get_ports mgtp_tx0_p]

set_property PACKAGE_PIN C18 [get_ports clk_27M]

set_property PACKAGE_PIN A14 [get_ports sdi0_sd_hd]

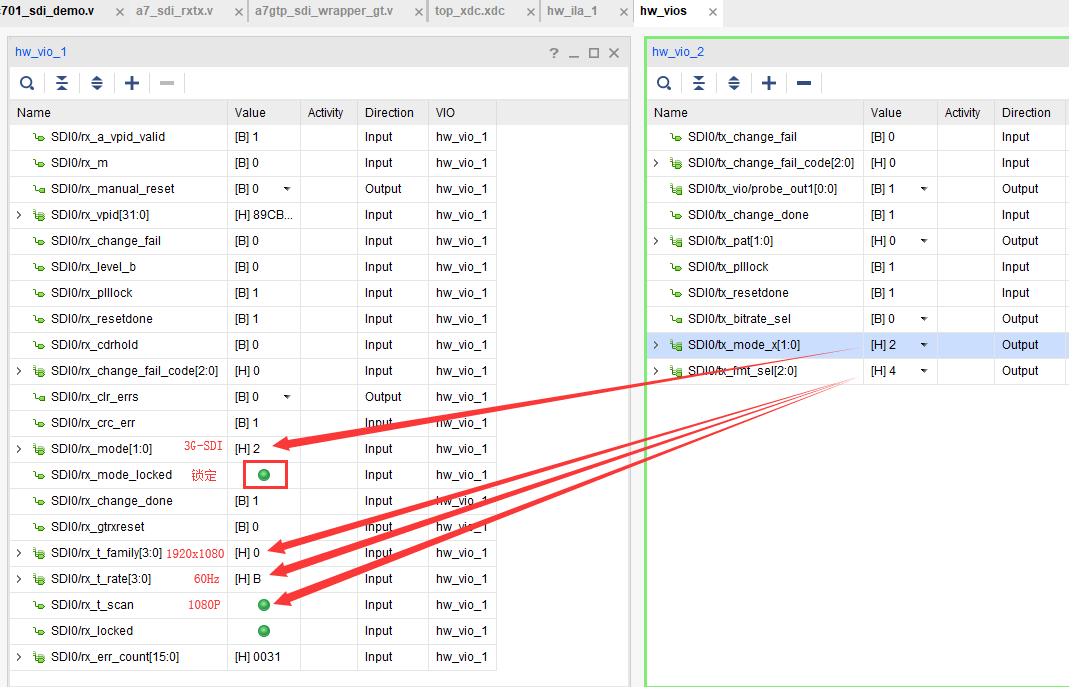

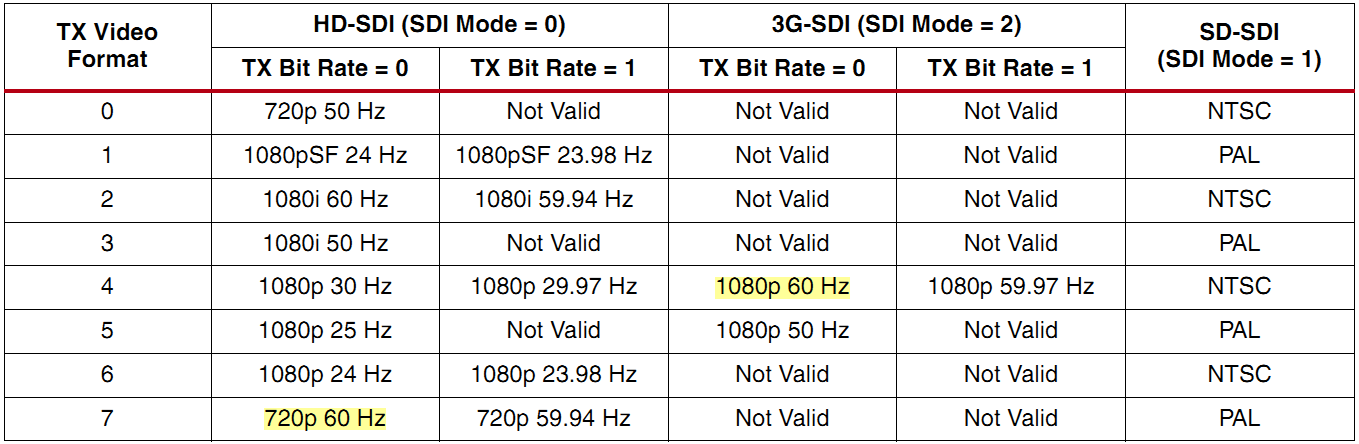

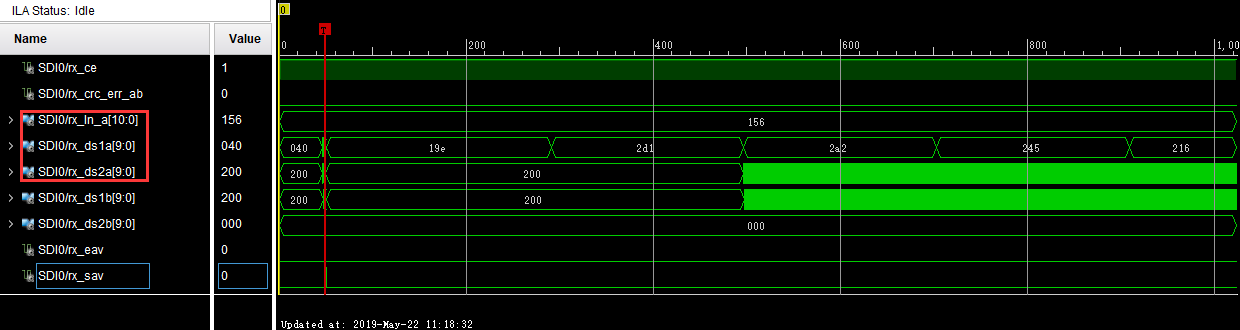

18. 综合产生bit文件下载。输入输出对接同轴电缆。打开调试界面如下。接收锁定(mode_locked,rx_locked)成功

VIO

tx模式选择

ila rx SDI数据口

以上

操作省略较多 仅参考备忘用途

引用:

xapp1097-smpte-sdi-a7-gtp.pdf

xapp1097.zip

ug482_7Series_GTP_Transceivers.pdf

pg071-v-smpte-sdi.pdf

本文介绍如何使用Xilinx Artix-7 FPGA通过GTP传送3G-SDI信号,涵盖GTP调用及与SDI IP互联方法,最终实现1080p60彩条内部产生并经SDI回环接收,适用于Artix-7及以上系列。

本文介绍如何使用Xilinx Artix-7 FPGA通过GTP传送3G-SDI信号,涵盖GTP调用及与SDI IP互联方法,最终实现1080p60彩条内部产生并经SDI回环接收,适用于Artix-7及以上系列。

1120

1120

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?