FPGA基于查找表(LUT)结构,本质上是一个ram。

1.组合逻辑

组合逻辑中,组合电路必须在所有情况下都为所有输出分配至少一个值,这意味着要写全else子句或分配输出的默认值。如果缺少, 输出默认保持不变,则形成了一个锁存器。

锁存器的弊端:1.FPGA中并没有锁存器结构,当形成了锁存器之后,需要花费更多的资源来构成它,形成了浪费。2.锁存器不利于时序分析,latch会对整体设计的时序性能有很大影响:latch对毛刺敏感,这就对时序要求提出了更高要求,数据需要保持长时间的稳定。

2.可编程输入输出单元

简写为IOB,是芯片与外界电路的接口部分,完成不同电气特性下对输入输出信号的驱动与匹配要求。FPGA内的IO按组分类,每个组的接口标准都由其接口电压VCCO决定每组都能独立支持不同IO标准。通过软件的灵活配置,可适配不同电气标准和IO物理特性,可以调整驱动电流大小,改变上下拉电阻。

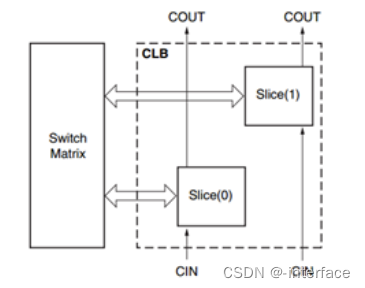

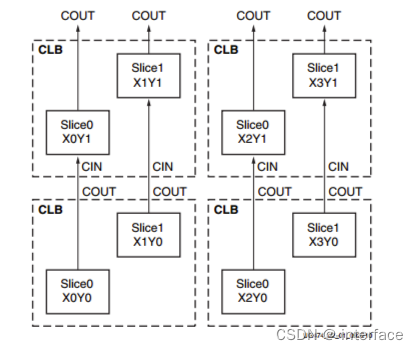

3.可配置逻辑块(CLB)

CLB是FPGA内基本逻辑单元,由查找表和可编程寄存器组成。查找表完成纯组合逻辑功能,内部寄存器可配置成触发器或寄存器。CLB由多个slice基本逻辑单位构成,每个slice由两个4输入函数/进位逻辑/算数逻辑/存储逻辑和函数复用器构成。

4.嵌入式块RAM(BRAM)

可以配置成单端口RAM/双端口RAM/内容地址存储器以及FIFO等常用存储结构。

5.数字时钟管理模块(DCM)

FPGA提供数字时钟管理和相位环路锁定。相位环路锁定能提供精确的时钟综合,且能降低抖动,实现过滤功能。

6.布线资源

布线资源用以连通FPGA内的所有单元,连线长度和工艺水平决定信号在连线上的驱动能力和传输速度。布线资源可以分为四类:全局布线资源,长线资源,短线资源,分布式布线资源。

7.底层内嵌的功能单元

主要指DLL/PLL/DSP/CPU等软处理核,现在越来越丰富的内嵌功能单元,使得FPGA成了系统级设计工具,使其具备了软硬件联合设计的能力,逐步向SOC过渡。

DLL:锁相环,根据电压调整输出频率。

PLL:延迟锁相环,对输入输出插入buffer,相位延迟补偿。

8.内嵌专用硬核资源

内嵌专用硬核资源是相对底层嵌入的软核而言的,指FPGA处理能力强大的硬核,等效于ASIC。为了提高FPGA性能,芯片生产商在芯片内部集成了一些专用硬核,包括乘法器/串并收发器/PCIE等。

1027

1027

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?