基于VU9P的双FMC+开发板

基于XCVU9P的双FMC+板卡。包含一片XCVU9P-2FLGB2014I/XCVU13P-2FLGB2014I、2组64-bit/8GB DDR4,28路光口;适合做雷达信号处理算法、AI等处理,尤其是波束合成算法。

AD9653是一款4通道、16位、125 MSPS模数转换器(ADC),内置片内采样保持电路,专门针对低成本、低功耗、小尺寸和易用性而设计。该产品的转换速率最高可达125 MSPS,具有杰出的动态性能与低功耗特性,对小封装尺寸的应用很有意义。

板卡上面插了两个FMC子卡,每个FMC子卡有2片AD9653,8个通道

7 系列设备中的所有 ISERDESE2 块都包含一个 Bitslip 子模块。 该子模块用于源同步网络类型应用程序中的字对齐目的。Bitslip 对 ISERDESE2 模块中的并行数据重新排序,允许将解串器接收到的重复串行模式的每个组合呈现给 FPGA 架构。这种重复的串行模式通常称为训练模式(许多网络和电信标准都支持训练模式)。 而Ultrascale以上的FPGA使用的是ISERDESE3,其与之前的原语比较(ISERDESE2),它没有BITSLIP 输入,无法进行同步的比特滑动操作没有可选的CE 输入;没有OFB输入,串行输出和输入之间时无法直接连接的;没有SHIFTIN和 SHIFTOUT 管脚,无法使用这些针脚将解串扩展到14位。需要自己写程序实现

第一片AD9653

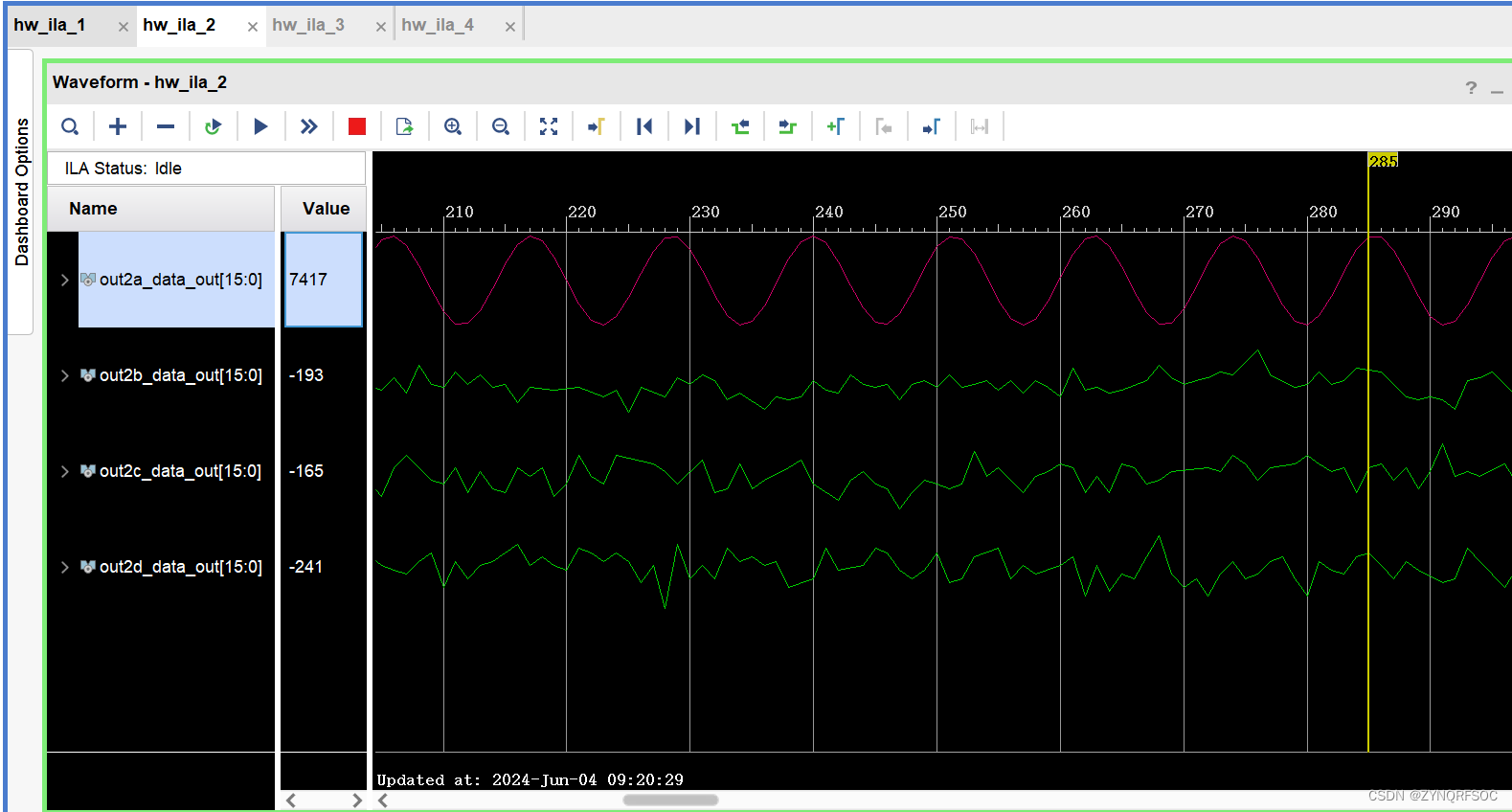

第二片AD9653

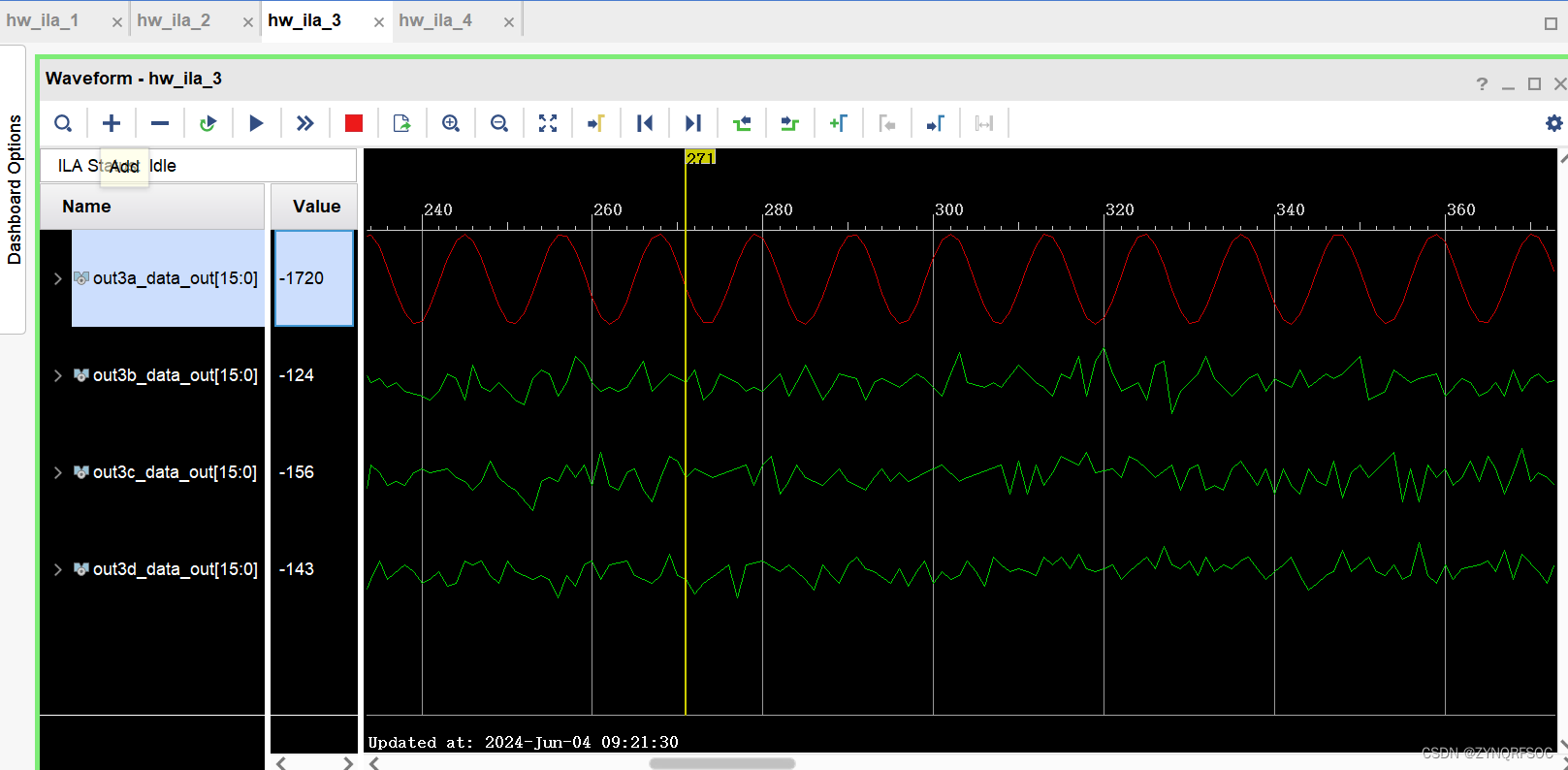

第三片AD9653

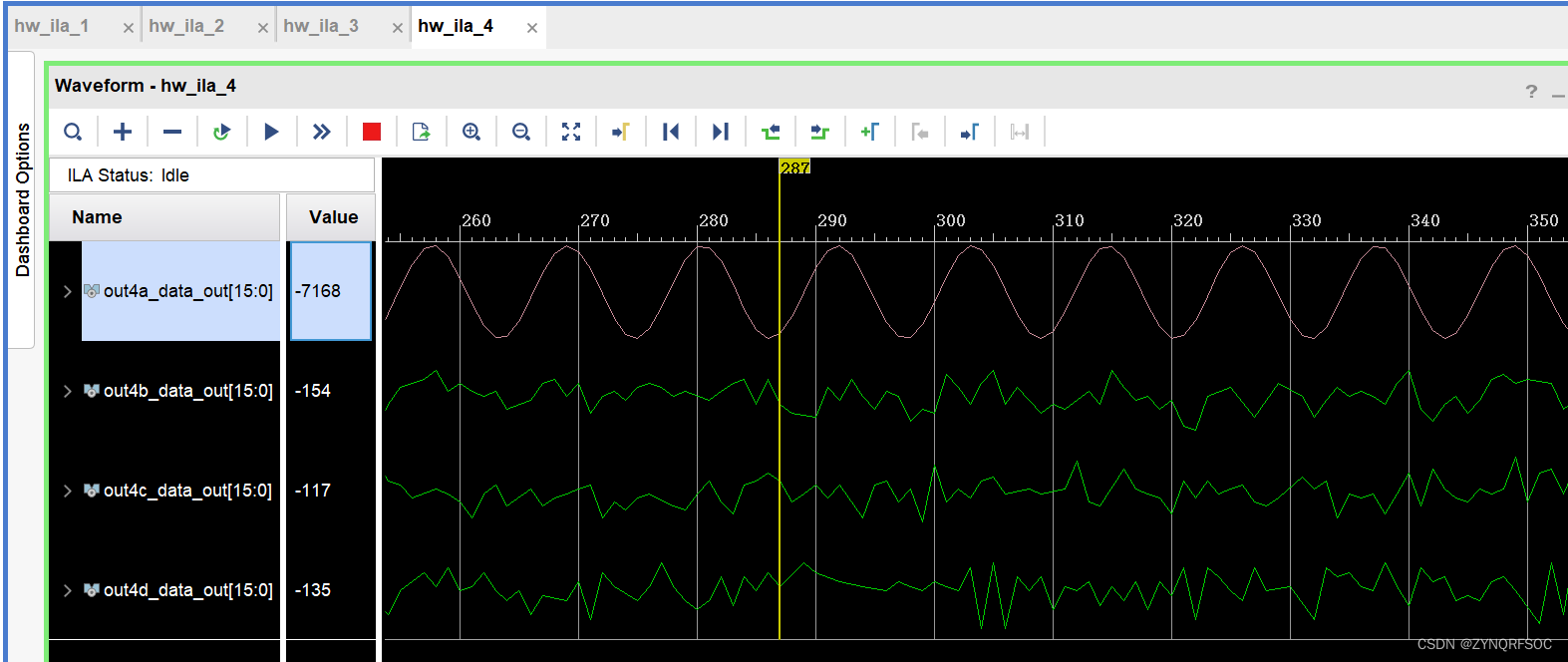

第四片

1078

1078

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?